Fターム[5J500AF15]の内容

Fターム[5J500AF15]に分類される特許

201 - 220 / 982

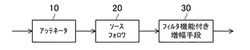

半導体集積回路およびそれを備えたチューナシステム

【課題】集積回路化されたRF信号処理回路について低電圧動作でも良好な歪特性を実現する。

【解決手段】半導体集積回路は、入力された信号を可変減衰量で減衰させるアッテネータ(10)と、アッテネータ(10)の出力を受けるソースフォロワ(20)と、ソースフォロワ(20)の出力に対してフィルタリング処理を行ってから可変ゲインで増幅する増幅手段(30)とを備えている。

(もっと読む)

差動増幅回路、レギュレータモジュール及びハイパワーアンプ

【課題】製造時の工程及び製品の消費電力の点で優れたレギュレータモジュール、及びそれを用いたバイアス回路を提供する。

【解決手段】パワーアンプモジュールとレギュレータモジュール801を含むパワーアンプをバイポーラトランジスタと電界効果トランジスタとを同一基板上に備える技術によって1チップで構成する。レギュレータモジュール801はデプリーション型トランジスタによる差動増幅回路を内包する。該差動増幅回路の一方のFETQ4のソース端子を、ダイオード接続したバイポーラトランジスタQ7を介して、FETQ3のソース端子と接続することで、バイポーラトランジスタQ7の電位差をレギュレータの出力電圧とすることが可能となる。

(もっと読む)

増幅回路

【課題】 圧電アクチュエータの駆動用途などに用いられる、高電圧出力が要求されるBTL方式を用いた増幅回路において、より容易にポップノイズの発生を抑制することができる増幅回路を提供する。

【解決手段】 前段に低電圧で動作するBTL方式のシングル差動変換回路A1、後段にシングル差動変換回路A1の出力信号VOT、VOBを増幅する増幅器A2a、A2bとを備えた増幅回路を構成する。シングル差動変換回路A0のパワーオン時の遷移状態においては、後段の増幅器A2a、A2bのミュート機能を起動することで出力信号OUTP、OUTNを0Vに固定し、出力ノイズの発生をマスクする。信号VOT、VOBが安定した後、ミュート機能を解除する。

(もっと読む)

増幅装置

【課題】温度変化によって最適動作点が変動しても電力効率を高効率化することができる。

【解決手段】増幅部1は、信号を増幅する第1の増幅器1aと、信号が所定レベル以上になると信号を増幅する第2の増幅器1bとを備える。検出部2は、温度変化を検出する。算出部3は、検出部2の温度変化の検出により、増幅部1から出力される出力信号の隣接チャネル漏洩電力比を算出する。制御部4は、算出部3によって算出された隣接チャネル漏洩電力比に基づいて、第1の増幅器1aおよび第2の増幅器1bのゲートバイアスを制御する。

(もっと読む)

高周波回路

【課題】低電圧のバッテリを用いて高電力を得ることが可能であり、且つ、低電力時の動作安定性を確保した高周波回路を提供する。

【解決手段】送信すべき高周波信号を増幅する増幅回路を複数並列に接続し、各増幅回路の出力を合成して空中線に供給する増幅部と、増幅部に低出力の動作をさせるローパワーモード時に、ローパワー信号を出力する制御部と、ローパワー信号によって複数の増幅回路のうち一部を停止させる動作抑制回路とを備えた。

(もっと読む)

高周波電力増幅器

【課題】回路規模を大きくすることなく、電力効率を改善する高周波増幅器を提供する。

【解決手段】高周波電力増幅器は、第1スイッチ素子104の他端と第2スイッチ素子105の他端との間に接続され、第1スイッチ素子104および第2整合回路115を介して第2アンプに電源を供給し、第2スイッチ素子105および第3整合回路116を介して前記第3アンプ103に電源を供給するための第1電源ライン133を具備し、第1スイッチ素子104の前記他端は、第1整合回路114の入力ノードと接続され、第2スイッチ素子105の前記他端は、第1電源ライン131を介して、第1整合回路114の入力ノードと接続され、第3アンプ103の出力ノードから当該高周波電力増幅器の出力側をみたインピーダンスが、第2アンプ102の出力ノードから当該高周波電力増幅器の出力側をみたインピーダンスより高い。

(もっと読む)

絶縁増幅器

【課題】精度が高く、かつ、シンプルな構成の絶縁増幅器

【解決手段】信号源1と、その非反転入力端子に信号源1の電圧を入力しその反転入力端子を第1の抵抗を介してアースに落とした演算増幅器と、第1の直流電源と、その発光素子が演算増幅器の出力端子に接続されその受光素子が第1の直流電源と前記演算増幅器の反転入力端子の間に接続された第1のフォトカプラと、第2の直流電源と、その発光素子が第1のフォトカプラの発光素子に極性を揃えて直列に挿入されその受光素子が第2の直流電源に接続された第2のフォトカプラと、第2のフォトカプラの受光素子に直列に挿入された第2の抵抗からなり、前記第2の抵抗に生じる電圧を出力信号として取り出す。

(もっと読む)

通信システムのための送信機のアーキテクチャ

【課題】通信システムの送信機の動作を制御し、応答時間の迅速化、出力電力の調整における線形性の向上、干渉の低減、電力消費量の低減、回路の複雑性の緩和、およびコストの低減を図った制御装置回路を提供する。

【解決手段】可変利得素子は、特定の利得範囲をカバーする可変利得をもつ。電力増幅器部は、可変利得素子に接続され、多数の個別の利得設定を含み、利得設定の1つはバイパス設定である。制御装置回路は、可変利得素子および電力増幅器部への制御信号を供給する。可変利得素子および電力増幅器部の利得は、出力伝送電力における過渡電流(transient)を低減し、出力伝送電力レベルの線形調節を行うように更新される。可変利得素子および電力増幅器部は、例えば、必要がないときは電力増幅器部の電源を切ることによって、電力消費量を低減するように制御される。

(もっと読む)

高効率、バランスを保たれた出力増幅器システム

【課題】高効率オーディオ増幅器システムを提供すること。

【解決手段】高効率増幅器システムであって、第1出力ステージによって増幅される第1の増幅された信号を出力するように構成される、第1出力ステージと、第1出力ステージと並列に連結される第2出力ステージであって、第2出力ステージによって増幅される第2の増幅された信号を出力するように構成される、第2出力ステージと、第1および第2出力ステージに含まれる複数のスイッチをコントロールするように動作可能なパルス幅変調器であって、パルス幅変調器が、さらに、第1および第2出力ステージから出力される電流を表す信号に基づいて、第1および第2出力ステージの出力電力のバランスを保つように動作可能である、パルス幅変調器とを含む、高効率増幅器システム。

(もっと読む)

電力増幅器

【課題】入力の整合回路での損失の低減、並びに、回路の簡略化及び小型化が可能な電力増幅器を提供する。

【解決手段】電力増幅器100であって、第1金属配線である環状1次コイル121と、複数の第2金属配線である複数の直線2次コイル122とを有し、入力インピーダンスの整合をとるとともに、入力信号を複数の分配信号に分配する入力側トランスフォーマ120と、複数の分配信号の1つを増幅する1対のトランジスタ111をそれぞれが備える複数のプッシュプル増幅器110と、第3金属配線である環状2次コイル131と、複数の第4金属配線である複数の直線1次コイル132とを有し、増幅された複数の分配信号を合成するとともに、出力インピーダンスの整合をとる出力側トランスフォーマ130とを備え、1対のトランジスタ111の2つの入力端子は、第2金属配線を介して互いに接続され、2つの出力端子は、第4金属配線を介して互いに接続される。

(もっと読む)

高周波増幅装置

【課題】高周波増幅装置のダイナミック利得特性を一定にし、高効率に動作させ高周波増幅装置の非線形歪みを低減した高周波増幅装置を提供する。

【解決手段】印加される電源電圧に基づき入力信号を増幅するソース接地又はエミッタ接地された高周波電力増幅器7、入力信号の包絡線成分を検出する第1の包絡線検出手段3、第1の包絡線検出手段で検出された包絡線成分に従った電源電圧を生成して高周波電力増幅器のドレイン電圧又はコレクタ電圧供給端子に印加するドレイン電圧又はコレクタ電圧生成手段4〜6、高周波増幅装置の瞬時入力信号に対する瞬時出力信号のダイナミック利得特性が一定となるように、入力信号の包絡線成分に従って高周波電力増幅器へのゲート電圧又はベース電圧を生成し高周波電力増幅器の入力信号も入力されるゲート電圧又はベース電圧供給端子に印加するゲート電圧又はベース電圧調整手段8〜11、を備えた。

(もっと読む)

高効率オーディオ増幅器システム

【課題】高効率オーディオ増幅器システムを提供すること。

【解決手段】高効率増幅器システムであって、該高効率増幅器システムは、デューティーサイクルの50%より大きい間に連続的に伝導するように動作可能な少なくとも2つの伝導性デバイスを有する第1出力ステージと、該第1出力ステージと並列に連結される第2出力ステージとを含み、該第2出力ステージが、インターリーブスイッチングによって動作可能なスイッチングモード出力ステージとして動作可能であり、該第1出力ステージおよび第2出力ステージが、負荷を供給するように協働的に動作可能であり、該第1出力ステージが、決定された閾値に従って、該第2出力ステージの動作を選択的に有効にし、そして、無効にするように構成される、高効率増幅器システム。

(もっと読む)

高周波増幅器

【課題】入力変調信号のエンベロープのダイナミックレンジが大きい場合においても、利得の低下を抑えることができるエンベロープトラッキング方式の高周波増幅器を提供すること。

【解決手段】変調電源回路100は、エンベロープ信号に対応した変調電源制御信号に応じて出力電圧を可変する変調電源120と、前記出力電圧が高い第1の電圧領域で最適な動作をする第1の高周波デバイス140と、前記出力電圧が第1の電圧領域より低い第2の電圧領域で最適な動作をする第2の高周波デバイス150と、第1の高周波デバイス140又は第2の高周波デバイス150のどちらかの通過経路及び出力信号を切り替える入力RFスイッチ160及び出力RFスイッチ170と、入力RFスイッチ160及び出力RFスイッチ170を切替制御する切替信号を生成する切替信号生成部112とを備える。

(もっと読む)

RF電力増幅装置およびその動作方法

【課題】低電力出力時の消費電流を低減して、DC電圧変換器による実装面積の増大を軽減する。

【解決手段】RF電力増幅装置200は、外部電源電圧Vcc1、2、3によって動作するドライバー段増幅器230と第1のRF増幅器270aと第2のRF増幅器270bとDC電圧変換器280を具備する。ドライバー段増幅230の出力は第1と第2のRF増幅器270a、270bの入力に供給され、第1のRF増幅器270aの実効素子サイズは第2のRF増幅器270bのそれより大きな素子サイズに設定される。DC電圧変換器280に外部電源電圧Vcc3が供給され、DC電圧変換器280は低電圧の動作電源電圧Vcc4を生成して、第2のRF増幅器270bの出力端子に供給する。第1のRF増幅器270aの出力端子には、DC電圧変換器280を介することなく、外部電源電圧Vcc2が供給可能とされる。

(もっと読む)

ソースフォロワ回路、ソースフォロワ型フィルタ回路

【課題】入力MOSトランジスタのオーバードライブ電圧が低い場合でも、出力信号が歪まないソースフォロワ回路を提供することを目的とする。

【解決手段】ソースフォロワ回路を、MOSトランジスタ(Tr)1、Tr2でなるTr対、ドレインがTr1のソース及び出力端子17に接続するTr3、ドレインがTr2のソース及び出力端子18に接続するTr4でなるTr対、ゲートとドレインがTr3のゲートに接続してTr3と電流ミラーを構成するTr7、Tr7のドレインに接続してTr7に電流を供給する電流源9、ゲートとドレインがTr4のゲートに接続してTr4と電流ミラーを構成するTr8、Tr8のドレインに接続してTr8に電流を供給する電流源10、Tr7のゲートと出力端子18との間に接続される容量素子11、Tr8のゲートと出力端子17との間に接続される容量素子12によって構成する。

(もっと読む)

半導体装置及びデータプロセッサ

【課題】動作電源電圧以上のアナロ信号を入力するための回路の回路規模を削減できる半導体装置を提供する。

【解決手段】アナログ信号(ISin)と基準電圧信号(HAVC)の夫々の外部入力端子からの入力に対して、対応する入力端子に一端が接続された入力抵抗素子(11,21)と、入力抵抗素子の他端に接続され電流経路を形成するトランジスタ(14,24)と、対応する入力抵抗素子の他端に接続して当該他端の電圧を所定の一定電圧とするように前記トランジスタのコンダクタンスをフィードバック制御する定電流回路(16,26)とを設け、アナログ信号側の前記トランジスタに流れる電流と基準電圧信号側の前記トランジスタに流れる電流とをカレントミラー回路で夫々鏡映し、前記カレントミラー回路で得られる一対のミラー電流に応ずる差動信号を差動回路(40)に供給する。差動回路は差動信号の差に基づいてアナログ信号の信号成分を出力する。

(もっと読む)

飽和増幅回路

【課題】小さい振幅の入力信号に対しては、飽和増幅部が有するDCオフセットの影響をキャンセルし、大きい振幅の入力信号に対しては、オフセットの帰還量を制限して飽和増幅出力の品質低下を抑制することが可能な飽和増幅回路を提供する。

【解決手段】DCオフセットをキャンセルするためのオフセットキャンセル回路12を備えた多段の差動増幅器からなる飽和増幅回路であって、差動増幅器への入力信号の振幅を判定するレベル判定回路15を有し、該レベル判定回路により予め定められた値より大きい振幅の入力信号と判定された場合は、前記のオフセットキャンセル回路12の帰還機能を無効とする。

(もっと読む)

変圧器電力合成器

【課題】複数の入力ポートと少なくとも1つの出力ポートとを備え、高い変圧器結合効率及び高い電力合成効率を達成するオンチップ変圧器電力合成器を提供する。

【解決手段】変圧器電力合成器は、複数の一次巻線導体と複数の二次巻線導体とを含む。一次巻線導体は、入力ポートにそれぞれ電気的に接続される。加えて、各一次巻線導体は対応する入力ポートのプラス端子とマイナス端子との間に電気的に接続されている。二次巻線導体は、一次巻線導体にそれぞれ磁気的に結合される。二次巻線導体は、出力ポートのプラス端子とマイナス端子との間に直列接続及び並列接続を含むトポロジー構造を持つように構成される。

(もっと読む)

フォールデッドカスコード型の差動アンプ及び半導体装置

【課題】回路を構成する素子数を削減すると共に、差動アンプのオフセットや抵抗の比精度による誤差を低減できるフォールデッドカスコード型の差動アンプ及び半導体装置を提供する。

【解決手段】フォールデッドカスコード型の差動アンプ14の入力段30をHVMOSにより構成し、出力段32をLVMOS20により構成することにより、従来では、2つの差動アンプにより構成していた差動増幅アンプを1つの差動アンプ14により構成することができる。

(もっと読む)

スイッチング回路及び包絡線信号増幅器

【課題】複数のスイッチング素子にて増幅したPWM信号を低損失で合成し、変調信号を復調することが可能なスイッチング回路、及び該スイッチング回路を備える包絡線信号増幅器を提供する。

【解決手段】スイッチング回路33は、一端が電源Vddに接続されたコイルL2と、該コイルL2の他端及びドレインD1,・・Dn間にコイルL3が各別に介装されたn個のトランジスタM1,・・Mnと、コイルL1,・・L1を介してゲートG1,・・Gnを縦続接続する接続回路とを備える。入力端子331から与えられて接続回路を伝播するPWM信号によってトランジスタM1,・・Mnが順次オンする。ドレインD1,・・Dnから各別のコイルL3を介して出力されるPWM信号が、コイルL2の他端において加算されるときに、パルス幅変調の基本波及びn−1次以下の高調波が打ち消される。

(もっと読む)

201 - 220 / 982

[ Back to top ]