Fターム[5J500AK08]の内容

Fターム[5J500AK08]に分類される特許

1 - 20 / 54

同相電圧帰還回路及び全差動演算増幅器

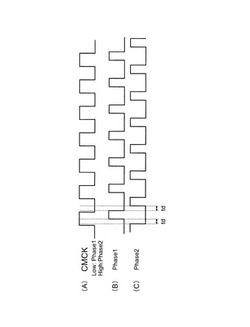

【課題】クロックフェイズの切り替わりにおける電圧スパイクの低減と共に出力電圧の収束速度の向上を図る。

【解決手段】第1及び第2の同相電圧検出器301,302は、ノンオーバーラップ期間が設定された2相クロックで駆動され、第1の同相電圧検出器301は、第1のクロック位相において充電動作し、第2のクロック位相において出力同相電圧の生成と電荷保持動作をし、第2の同相電圧検出器302は、第2のクロック位相において充電動作し、第1のクロック位相において出力同相電圧の生成と電荷保持動作をし、ノンオーバーラップ期間において、第1及び第2の同相電圧検出器301,302は、スイッチ35a〜35f、36a〜36fにより入力段及び出力段と電気的に分離され、同相電圧出力トランジスタのゲート・ソース間寄生容量により電荷保持動がなされる構成となっている。

(もっと読む)

差動増幅器

【課題】出力電圧の出力精度に段差が発生していた。

【解決手段】電流源で駆動される第1、第2の差動対と、その電流源を駆動する第1の基準電流発生回路と、を備える第1の差動入力部と、電流源で駆動される第3、第4の差動対と、その電流源を駆動する第2の基準電流発生回路と、を備える第2の差動入力部と、前記第1、第2の差動入力部との出力に応じて、出力する出力部と、を有し、前記第1、第2の基準電流発生回路の第1、第2の電流経路上に接続される第1、第2のトランジスタを入力信号に応じて制御することで、前記第1、第2の差動入力部の出力を制御する差動増幅器。

(もっと読む)

演算増幅器

【課題】所定のS/Nを維持しながら消費電流の増加を抑制することのできる演算増幅器を提供する。

【解決手段】実施形態の演算増幅器は、正相信号Vpと逆相信号Vmが入力される差動増幅回路100と、差動増幅回路100へ動作電流を供給するカレントミラー回路200とを有する。この演算増幅器は、入力信号電圧検出回路1が、正相信号Vpと逆相信号Vmとの間の電圧差を検出し、動作電流制御回路2が、その電圧差の大きさに応じた制御信号を出力する。この制御信号の制御により、可変定電流回路3が、カレントミラー回路200へ入力する定電流の大きさを変化させる。

(もっと読む)

半導体集積回路装置

【課題】 差動増幅回路の出力信号の特性を改善する。

【解決手段】入力データ信号が‘Low’レベルになると、トランジスタ16に流れる電流I1の電流が減少し、抵抗14と抵抗14aとの接続部(ノードD)の電位が高くなる。この電位は、トランジスタ18にゲートに入力(負帰還)され、該ゲート電位が高くなることによって、テイル電流量I_TAILが増加する方向に調整される。入力データ信号が‘High’レベルになると、電流I1の電流が多く流れ、ノードDの電位が下がる。これによって、トランジスタ18のゲート電位(負帰還)が下がり、テイル電流量I_TAILを絞る方向に調整される、これによって入力波形の立上りと立下りとで、それぞれ出力波形との遅延時間の差が小さくなる。

(もっと読む)

演算増幅器

【課題】入力オフセット電圧温度変動を悪化させることなく入力オフセット電圧のゼロ調整を可能とする。

【解決手段】差動対をなすように第1及び第2のPチャネルMOSトランジスタ1,2が差動接続されてなる差動増幅回路101を有すると共に、第1及び第2のPチャネルMOSトランジスタ1,2へテール電流を供給する第3の定電流源13に対して負の温度特性を有する電流を生成、出力する負温度特性電流生成回路103と、第1及び第2のPチャネルMOSトランジスタ1,2の各々へ入力オフセット電圧補正電流を供給する入力オフセット電圧補正電流生成回路102とを具備し、入力オフセット電圧補正電流生成回路102は、負温度特性電流生成回路103の出力電流を基に、入力オフセット電圧補正電流を出力調整可能に構成されたものとなっている。

(もっと読む)

半導体装置

【課題】消費電流を削減する。

【解決手段】第1及び第2の入力端子に現れる電位差を第1及び第2の電源に基づいて増幅する差動アンプ(図2のMN1、MN2が相当)と、差動アンプを動作させるバイアス電流を制御するバイアストランジスタ(図2のMN3が相当)と、差動アンプの負荷となるカレントミラー回路(図2のMP1、MP2が相当)と、カレントミラー回路のダイオード接続側と其々の制御端が接続されると共に第1及び第2の電源間に直列に接続される、バイアストランジスタと逆導電型の第1及び第2のトランジスタ(図2のMP4、MP6が相当)を有し、第1及び第2のトランジスタの間の接続ノードをバイアストランジスタの制御端に接続するバイアス制御回路と、を備える。

(もっと読む)

オペアンプ

【課題】位相余裕を減らすことなく電源立ち上げ時における出力電圧の立ち上がりを速くする。

【解決手段】電源電圧が立ち上がると、入力電圧VinpがVinmよりも高くなるので、トランジスタ9がオン、トランジスタ10がオフとなり、差動対11に供給される動作電流は全てトランジスタ9に流れる。電流検出回路62に電流が流れないので、トランジスタ73がオフし、第2の定電流回路69が出力する増分動作電流I2は、ダイオード72を通して差動対11に流れ込む。トランジスタ9に流れる電流は定常動作電流I1+増分動作電流I2となり、位相補償コンデンサ8の充電電流が増えて出力電圧Voの立ち上がりが速くなる。

(もっと読む)

差動増幅回路

【課題】差動増幅回路における入力オフセット電圧の上昇を抑制しつつ、同相入力電圧範囲を拡張する。

【解決手段】本発明による差動増幅回路は、ソース及びバックゲートが第1電流源205に共通接続された差動対トランジスタ201、202を備える差動入力段回路111と、差動入力段回路111の出力端子に接続される出力段回路121と、第1電流源205と出力段回路121の第2電流源206のそれぞれの電流I1、I2を、差動入力段回路111への入力電圧VIN1、VIN2に応じた大きさに調整する電流制御回路101とを具備する。

(もっと読む)

フィルタ回路

【課題】フィルタ回路の遮断周波数精度を悪化させること無く、回路規模を低減することができるフィルタ回路を提供する。

【解決手段】駆動電流生成回路303は、容量C1に第1の基準電流を一定期間充電することにより生成される充電電圧を用いて、容量C1と第1の基準電流の比に比例した第1の駆動電流を生成する。OTA301は、正入力端子と負入力端子間の電位差に応じて、第1の駆動電流から、容量C1と第1の基準電流の比に逆比例した第2の駆動電流を生成して電圧に変換し、この電圧に応じて第2の基準電流を分配する。OTA301は、第2の基準電流を分配した電流と同量の電流を折り返して供給するカレントミラー回路を有し、正入力端子と負入力端子間の電位差に応じた電流をカレントミラー回路により折り返して負荷容量302に供給する。

(もっと読む)

差動増幅回路および液晶表示装置

【課題】消費電流を増加させずにスルーレートを向上する差動増幅回路、表示用駆動回路を提供する。

【解決手段】差動増幅回路は、差動信号を入力する入力段と、入力段の出力に基づいて容量性負荷を駆動する出力段とを具備する。入力段は、差動信号を入力する差動信号入力部(MN1/MN2、MN11/MN12/MP21/MP22)と、差動入力部にバイアス電流を供給する電流源(MN3、MN10/MP20)と、電流源(MN3、MN10/MP20)に並列に挿入される可変容量(Cs)を含むスルーレート調整部(414、415)とを備える。

(もっと読む)

広帯域増幅器

【課題】高い周波数までの二次歪成分を除去し、出力電流信号の線形性を向上させることができ、二次歪耐性(IIP2)を向上させることができる広帯域増幅器を実現する。

【解決手段】第1及び第2のMOSトランジスタQ1,Q2による差動対が発生する二次歪成分電流と逆極性の電流信号を差動対の負荷電流源となる第3及び第4のMOSトランジスタQ3,Q4によって発生し、逆極性の二次歪電流を相互に打ち消し合うように作用させて線形性を向上させ、更に、第1及び第2のMOSトランジスタQ1,Q2の入力へのバイアスを設定する第1のバイアス回路を第1及び第2のMOSトランジスタのドレイン電流が流れるように、且つ、該ドレイン電流をゲート電圧で二回微分した成分の絶対値が極小となるようなバイアス値を得るようにし、且つ、第3及び第4のMOSトランジスタQ3,Q4のサイズを二次歪み成分が主成分である電流を生成するように設定する。

(もっと読む)

パワーアンプモジュール及び携帯情報端末

【課題】パワーアンプのバイアスを変えて複数のモードを設定してもそれぞれに最適な温度補償を実現できる手段を提供する。

【解決手段】温度が下がった場合に減衰量が増加するアッテネータを並列に接続した3極管動作をさせるFET100でパワーアンプモジュールを構成する。FET100のゲート電圧は制御電圧発生回路300で制御する。この制御電圧発生回路300により温度特性を決定することで最適な温度補償を実現可能ならしめる。

(もっと読む)

受光回路および受光回路を備える電子機器

【課題】受光回路における、素子のバラツキによる特性の劣化や、出力インピーダンスの劣化といった問題や、受光素子への正常なバイアス電圧を確保できないといった問題の、少なくとも1つを解決する。

【解決手段】施形態の受光回路は、電流源回路とローパスフィルタと電流検知回路とを持つ。電流源回路は、受光素子に対し直流電流を供給する。ローパスフィルタは、使用する信号帯域をカットする。電流検知回路は、前記電流源回路と同一種類のデバイスにより前記電流源回路とカレントミラー回路を構成し、流入電流を検知し、該検知結果に応じて、前記ローパスフィルタを介し前記電流源回路を制御する。

(もっと読む)

利得変動補償装置

【課題】電圧源から提供する電圧が変動した場合でも増幅回路に流れる電流量を制御し、利得の変動を補償する利得変動補償装置を提供すること。

【解決手段】利得変動補償装置100は、電圧源111から提供される電圧及び定電流源を用いて入力信号を増幅する増幅回路110と、電圧源111から提供される電圧の変動を検知する電源電圧変動検知部120と、電源電圧変動検知部120により検知された電圧の変動量に応じて、増幅回路110に流れる電流量を制御する電流可変回路130とを備える。利得変動補償装置100は、増幅回路110又はその差動回路の定電流源トランジスタと並列に電流可変回路130を接続し、事前に電流可変回路130に電流を流し、電源電圧変動検知部120において電源電圧の変動を検知する。電流可変回路130は、電圧変動量に応じて電流量の調整を行い、増幅回路110に流れる電流量を制御する。

(もっと読む)

単相差動変換器

【課題】

低雑音の単相差動変換器を提供する。

【解決手段】

単相差動変換器は,第1の出力負荷抵抗と第1の増幅トランジスタとが電源と基準電圧との間に設けられ,第1の増幅トランジスタに単相入力信号が供給され,第1の出力負荷抵抗の第1の増幅トランジスタ側のノードに第1の出力端子が設けられた非反転増幅回路と,第2の出力負荷抵抗と第2の増幅トランジスタとが電源と基準電圧との間に設けられ,第2の増幅トランジスタに単相入力信号が供給され,第2の出力負荷抵抗の第2の増幅トランジスタ側のノードに第2の出力端子が設けられた反転増幅回路と,第1,第2の出力端子に単相入力信号の周波数帯域で高インピーダンスを有する第1,第2のインピーダンス手段を介して共通に設けられた追加電流源とを有する。

(もっと読む)

増幅回路、集積回路装置及び電子機器

【課題】特性が安定し、増幅効率の良い増幅回路、集積回路装置及び電子機器等を提供すること。

【解決手段】増幅回路は、出力ノードNPに増幅信号VPを出力する増幅用トランジスター10と、インダクターLA及びキャパシターCA、CBにより構成され、インダクターのインダクタンス値及びキャパシターのキャパシタンス値の少なくとも一方が可変に設定されるLC負荷回路20と、増幅信号VPの電圧振幅を検出する振幅検出回路30と、振幅検出回路30の検出結果に基づいてインダクタンス値及びキャパシタンス値の少なくとも一方を設定し、増幅信号VPの電圧振幅値を極大値に近づける制御を行う制御回路40とを含む。

(もっと読む)

半導体装置、データ伝送システム、及び半導体装置の制御方法

【課題】小振幅信号を高速に増幅して出力し、かつ、消費電力の少ないアンプを備える半導体装置を提供する。

【解決手段】クロックに同期してデータが更新される小振幅信号を受信するアンプ部と、アンプ部の出力に接続された出力部と、を備え、アンプ部はクロックに同期して小振幅信号の論理レベルが遷移しうるタイミングで電流源の電流を増加し、遷移しないタイミングで電流を減少する。出力部はクロックに同期してアンプ部の出力データの論理レベルが遷移しうるタイミングで出力インピーダンスを低下させて高速に負荷を駆動すると共に、論理レベルが遷移しないタイミングで出力インピーダンスを増加させて貫通電流が流れることを防ぐ。

(もっと読む)

差動増幅器

【課題】非反転入力端子の電圧が変化した場合でも、出力トランジスタに流れる電流を一定にすることができる、差動増幅器を提供する。

【解決手段】非反転入力端子143と、反転入力端子144と、P型MOSトランジスタ107及び108とN型MOSトランジスタ101及び102と定電流源121とからなる差動増幅回路と、P型MOSトランジスタ103及び104とN型MOSトランジスタ113及び114と定電流源122とからなる差動増幅回路と、P型MOSトランジスタ107及び108に電流を流す定電流源124とで構成される相補型フォールデッドカスコード増幅回路に、さらにP型MOSトランジスタ107及び108に電流を流す電流制御回路である、定電流源123とN型MOSトランジスタ105を備え、相補型差動対の負荷であるカスコード増幅回路に流れる電流を、非反転入力端子の電圧によって制御する構成とした。

(もっと読む)

差動増幅装置

【課題】本発明の一実施例では、入力差動信号の電位差に応じて電流供給能力を最適化する差動増幅装置を提供することを目的とする。

【解決手段】上記課題を解決するため、本発明の一実施例である差動増幅装置は、入力電圧の電位差に応じた電流駆動能力を有する差動アンプと、該入力電圧の電位差に応じた電圧振幅を有する調整信号を出力する調整部と、該差動アンプの電流駆動能力を該調整信号に応じて調整する電流源とを有する。

(もっと読む)

差動増幅回路

【課題】回路規模の大型化を抑えながら、駆動用電圧の上昇に伴う消費電流の増大を抑制すると共に駆動用電圧の下降に伴う印加電圧不足を解消することができる差動増幅回路を提供する。

【解決手段】NMOSトランジスタ16のドレイン端子及びソース端子間を流れる電流の大きさを予め定められた大きさにする電圧Vref0がNMOSトランジスタ16のゲート端子に印加されるように、閾値電圧が異なるNMOSトランジスタ26,28が並列接続されると共にNMOSトランジスタ26,28の各ドレイン端子の共通接続点に駆動用電圧Vccが印加され、共通接続点Fと負荷との接続点GがNMOSトランジスタ16のゲート端子に接続された。

(もっと読む)

1 - 20 / 54

[ Back to top ]