Fターム[5J500AK64]の内容

Fターム[5J500AK64]に分類される特許

1 - 20 / 49

コンデンサマイクロホン用インピーダンス変換器およびコンデンサマイクロホン

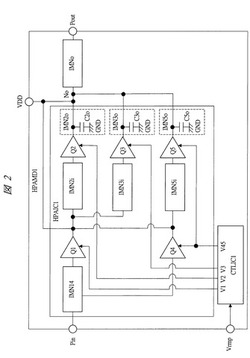

高周波電力増幅装置

【課題】トークカレントの低減または出力における位相偏差の低減を実現可能な高周波電力増幅装置を提供する。

【解決手段】例えば、トランジスタサイズが異なる複数の電力増幅用トランジスタQ1〜Q5と、複数のインピーダンス整合回路IMN14,IMN2i,IMN3i,IMN5i,IMN2o,IMN3o,IMN5o,IMNoを備え、電力指示信号Vrmpに応じて使用する信号経路を切り替える。高パワー時にはQ1→Q2の経路が使用され、中パワー時にはQ1→Q3の経路が使用され、低パワー時にはQ4→Q5の経路が使用される。ここで、当該高周波電力増幅装置は、各信号経路で経由する電力増幅用トランジスタの段数とインピーダンス整合回路の個数が等しくなるように構成される。

(もっと読む)

信号変換装置及び信号変換方法

【課題】ADCのSNRを向上し、かつ、マイクロフォン用IC全体の歪み特性の劣化を最低限に抑えること。

【解決手段】本発明にかかる信号変換装置は、入力アナログ信号を増幅して出力するプリアンプ回路と、入力クロックのサイクルに応じて、プリアンプ回路からの出力に基づくアナログ信号をデジタル信号へ変換するAD変換器と、入力クロックの周波数に応じて、デジタル信号へ変換される前のアナログ信号である変換前アナログ信号の調整を制御する調整制御回路と、を備える。

(もっと読む)

プリアンプ回路、及びマイクロフォン

【課題】低ノイズ特性を持つプリアンプ回路を提供すること

【解決手段】プリアンプ回路は、ソースフォロアとして機能するPMOSトランジスタM1A及びM1Bを備える。さらにプリアンプ回路は、差動増幅器として対となって機能するPMOSトランジスタM2A及びM2Bを備える。M1AのゲートとM2Bのゲートとが、可変容量C2を介して接続される。M1BのゲートとM2Aのゲートとが、可変容量C1を介して接続される。M1Aのソースと、M2Aのドレインと、が接続される。M1Bのソースと、M2Bのドレインと、が接続される。M2Aのソースと、M2Bのソースと、が接続される。

(もっと読む)

音声増幅回路およびそれを具備する撮像装置または撮像装置の周辺機器

【課題】MIC増幅回路における雑音と歪とを低減する。

【課題を解決するための手段】基板実装型MICコネクタを実装した第一の基板に、電源重畳回路と信号入力結合回路と入力音声増幅回路とを、表面実装部品の第一の演算増幅器とアナログスイッチICと金属皮膜抵抗と容量として実装し、前記信号入力結合回路は、前記第一の演算増幅器の正入力と接地間の抵抗と正入力と低電圧電源間の抵抗とが設置され、前記第一の基板と接続された第二の基板に電源発生部と平衡出力音声増幅回路とを第二の演算増幅器とアナログスイッチICと金属皮膜抵抗と容量として実装し、前記第二の演算増幅器の正入力と接地間の抵抗と正入力と低電圧電源間の抵抗とが設置され、前記平衡出力音声増幅回路の共通帰還回路がタンタル電解コンデンサの逆極性の直列接続または低歪率セラミックコンデンサで容量結合されたことを特徴とする音声増幅回路。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止することにより、規格値を超過するドレイン電流を発生することを回避できる接合形電界効果トランジスタを用いた増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面にイオン注入によりn型不純物層を設け、p+型半導体基板とpn接合を形成して接合容量をハイパスフィルタ5の容量4とする。

(もっと読む)

増幅回路装置

【課題】J−FETを増幅回路装置として採用する場合に、意図しない低周波信号の入力を防止し、規格値を超過するドレイン電流が発することを回避する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FETのゲート−ソース間に接続される抵抗とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。n型半導体基板上にバックゲート領域となるp型半導体層を設けてpn接合を形成し、この接合容量をハイパスフィルタ5の容量とする。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止し規格値を超過するドレイン電流が発生することを回避できる増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量4を付加し、当該容量4とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタを構成する。ハイパスフィルタの遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面に絶縁層を設けてこれを誘電体とし、導電部材と基板とで平行平板型の容量4を接続する。

(もっと読む)

電荷検出回路

【課題】差動アンプの入力側のゲイン調整を容易に行うことができる電荷検出回路を提供する。

【解決手段】電荷発生型センサ及び容量変化型センサの何れかで構成される物理量検出センサ1A,1Bの一端が差動アンプ3の負極入力端子に接続され、他端が前記差動アンプ3の正極入力端子に接続され、前記差動アンプ3の出力端子と前記負極入力端子との間にフィードバック抵抗Rf及びフィードバック容量Cfが並列に接続され、且つ前記差動アンプの正極入力端子と基準電圧との間にキャンセル抵抗Rc及びキャンセル容量Ccが並列に接続された差動型の電荷検出回路であって、前記差動アンプの負極入力端子及び正極入力端子の少なくとも一方に逆バイアス電源7,9によって逆バイアス電位が与えられた可変容量ダイオードD1,D2を接続してゲイン調整を可能とした。

(もっと読む)

増幅回路装置

【課題】意図しない低周波信号の入力を防止し、規格値を超過するドレイン電流が発生することのない接合形電界トランジスタを用いた増幅回路装置を提供する。

【解決手段】J−FETの封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FETのゲート−ソース間に接続される抵抗とによってハイパスフィルタを構成する。ハイパスフィルタの遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できるので、定常状態での外部要因によるゲート電位の変動の影響を低減できる。

(もっと読む)

デジタルアンプ

【課題】出力電流の過電流及び共振電流の検出時間を短くするとともに、出力の停止を最小限にし、より適切な電流制御動作を可能にする。

【解決手段】デジタルアンプは、スイッチング素子Q1、Q2の出力部において、出力電流における所定値以上の過電流を検出する過電流検出回路19と、過電流検出信号の位相を進める進相回路22と、出力フィルタ15において共振が発生した際の出力電流に関する所定値以上の共振電流を検出する共振電流検出回路21とを有する。駆動回路12は、過電流検出信号または共振電流検出信号に基づき、出力電流の異常状態が検出された場合に、駆動信号をオフしてスイッチング素子Q1、Q2のスイッチング動作を停止させることで、電流制限動作を行う。

(もっと読む)

増幅回路

【課題】入力レベルが通常レベルと、過大レベルの2つの出力を効果的に得る。

【解決手段】負帰還路を有するオペアンプ14の負入力端に入力される入力信号を増幅して出力信号を出力する。オペアンプ14の負入力端に入力される前記入力信号と前記負帰還路からの帰還信号を合わせた負入力端側信号と、前記オペアンプからの出力信号を重み付け加算し、合成信号を出力する信号合成手段(18,20,22)を有し、オペアンプ14の出力信号と、合成信号の2つの信号を得る。

(もっと読む)

充電回路、増幅回路

【課題】消費電力及びノイズを抑制しつつ、昇圧電圧でコンデンサを早く充電可能な充電回路を提供する。

【解決手段】充電回路は、入力されるクロック信号の周波数の上昇に応じて短くなる時間間隔ごとに入力電圧を昇圧した昇圧電圧を生成するチャージポンプ回路と、昇圧電圧を積分してコンデンサに印加する積分回路と、第1クロック信号がクロック信号としてチャージポンプ回路に入力される際にコンデンサの充電電圧が所定レベルとなるまでの時間よりも短い時間で充電電圧が所定レベルとなるよう、第1クロック信号より高い周波数の第2クロック信号をクロック信号としてチャージポンプ回路に出力した後に、第1クロック信号をクロック信号としてチャージポンプ回路に出力するクロック信号出力回路と、を備える。

(もっと読む)

アナログ回路及び半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、信号検出感度が高く、ダイナミックレンジの広い半導体装置を得ることを課題の一つとする。

【解決手段】チャネル形成層としての機能を有し、水素濃度が5×1019(atoms/cm3)以下であり、電界が発生していない状態においては、実質的に絶縁体として機能する酸化物半導体を有する薄膜トランジスタを用いてアナログ回路を構成することで、信号検出感度が高く、ダイナミックレンジの広い半導体装置を得ることができる。

(もっと読む)

入力回路

【課題】短時間で入力信号を受信可能な状態に遷移する入力回路を提供する。

【解決手段】入力端子P1は、外部からの入力信号S1を受ける。入力トランジスタM1は、その制御端子が入力端子P1に接続され、入力信号S1に応じて状態が変化する。初期化トランジスタM2は、入力端子P1と接地端子P2の間に設けられる。制御回路12は、入力回路10に対する電源の投入時に、初期化トランジスタM2をオンし、その後初期化トランジスタM2をオフする。

(もっと読む)

信号を送信するための無線局

【課題】無線局の送信機の出力電力を最大化する。これはバッテリの寿命を伸ばすという利点を有し、また移動電話における電気コンポーネントの寿命も伸びる。

【解決手段】無線局の送信機のアンテナは、可変のリアクタンスを有するインピーダンスを付加することによって、電力増幅器の出力インピーダンスに整合される。プロセッサによりこのインピーダンスの可変のリアクタンスが、電力増幅器の出力信号にしたがって調整される。可変のリアクタンスを有するインピーダンスは、複数のインダクタおよびキャパシタ、または可変のインダクタおよびキャパシタ、または複数のマイクロストリップ線路からなる。

(もっと読む)

増幅素子

【課題】ECMのインピーダンス変換および増幅に、J−FETを入力としバイポーラトランジスタを出力とする増幅素子に、バックゲート構造のJ−FETを用いると、バックゲート−半導体基板間の容量が、増幅素子の入出力間の寄生容量(ミラー容量)となり、増幅素子の入力ロスが増大する問題に対し有効な半導体装置を提供する。

【解決手段】接地されたp型半導体基板11にp型半導体層12を積層し、p型半導体層12にn型チャネル領域22を有するJ−FETと、n型コレクタ領域33bを有するバイポーラトランジスタを設けた増幅素子とする。これにより、増幅素子の入出力間の寄生容量が発生しなくなるため、ミラー容量による入力ロスの増大を防止できる。また、J−FETのチャネル領域は、エミツタ拡散31と同時に形成できるため、IDSSSや、ピンチオフ電圧が安定し、増幅素子としての消費電流のばらつきが低減し、生産性が向上する。

(もっと読む)

高周波電力増幅装置及びそれを有する無線通信装置

【課題】マルチバンド・マルチモードに対応し、受信感度の劣化を低減可能な高周波電力増幅装置を提供する。

【解決手段】本発明に係る高周波電力増幅装置は、CDMAモードかつ第1の周波数帯域内の第1高周波信号と、TDMAモードかつ第1の周波数帯域内の第3高周波信号とが択一的に入力される入力端子IN1と、CDMAモードかつ第2の周波数帯域内の第2高周波信号と、TDMAモードかつ第2の周波数帯域内の第4高周波信号とが択一的に入力される入力端子IN2と、入力された第1高周波信号を増幅する電力増幅器101と、入力された第2高周波信号を増幅する電力増幅器102と、入力された第3高周波信号を増幅する電力増幅器103と、入力された第4高周波信号を増幅する電力増幅器104とを有し、電力増幅器101、電力増幅器102、電力増幅器103及び電力増幅器104は、この順に並んで配置されている。

(もっと読む)

コンデンサマイクの増幅回路

【課題】コンデンサマイクの増幅回路において、電源電圧のノイズに対するノイズ耐性を向上させる。

【解決手段】本発明のコンデンサマイクの増幅回路によれば、電源電圧Vddのノイズ成分は互いに隣接する外部電源配線1、外部配線2の間にある寄生容量Cpx1を介して、増幅部10の演算増幅器11の反転入力端子(−)に印加されるが、もう一方の非反転入力端子(+)に内部電源配線13との容量結合により問題の電源電圧Vddのノイズ成分を印加するように構成したことにより、当該ノイズ成分を演算増幅器11でキャンセルすることができる。

(もっと読む)

増幅回路用の回路基板

【課題】グランドバウンスに基づくノイズが少ない増幅回路が容易に製造可能となる回路基板を提供する。

【解決手段】長尺な正極側接続部32と、長尺な負極側接続部34と、正極側接続部32の一端側と負極側接続部34の一端側とを接続する入力側電源ライン37と、入力側電源ライン37の中途部に設けられた第1のコンデンサ配置部38および第2のコンデンサ配置部40と、第1のコンデンサ配置部38と第2のコンデンサ配置部40との間に設けられた入力部36と、正極側接続部32の他端側と負極側接続部34の他端側とを接続する出力側電源ライン45と、出力側電源ライン45の中途部に設けられた第3のコンデンサ配置部46および第4のコンデンサ配置部48と、第3のコンデンサ配置部46と第4のコンデンサ配置部48との間に設けられた出力部44とを具備する。

(もっと読む)

1 - 20 / 49

[ Back to top ]