Fターム[5J500AM06]の内容

Fターム[5J500AM06]の下位に属するFターム

インバーテッド・ダーリントン接続 (1)

Fターム[5J500AM06]に分類される特許

1 - 20 / 20

ベース電流補償回路

【課題】印加電圧が変動しても、入力端子から流れ込む電流を一定とすることのできるベース電流補償回路を提供する。

【解決手段】実施形態のベース電流補償回路1は、補償対象トランジスタQ10のベースが接続される入力端子INにベースが接続されたアーリー効果相殺用トランジスタQ2が、補償対象トランジスタQ10に発生するアーリー効果と同じアーリー効果を補償電流生成用トランジスタQ1に発生させる。補償電流生成用トランジスタQ1に流れる電流は、カレントミラー回路11で折り返されて、補償対象トランジスタ10のゲートへ注入される。

(もっと読む)

増幅回路

【課題】SEPP回路の温度上昇の熱が放熱器を介してバイアス回路に伝わるまでの熱結合によるタイムラグを解消して、熱暴走の発生を未然に防止する。

【解決手段】トランジスタ素子を有して構成されるトランジスタQ1と、トランジスタQ1のトランジスタ素子とは逆極性のトランジスタ素子を有して構成されるトランジスタQ2と、が直列接続されると共に、両端が電源に接続されたシングルエンデッド・プッシュプル回路と、トランジスタQ1回路にバイアス電圧を印加するバイアス回路を構成するトランジスタQ5と、トランジスタQ2にバイアス電圧を印加するバイアス回路を構成するトランジスタQ6と、トランジスタQ1のベース電圧を検出してトランジスタQ5にフィードバックする直列接続の抵抗R3、R4と、トランジスタQ2のベース電圧を検出してトランジスタQ6にフィードバックする直列接続の抵抗R5、R6と、を備えている。

(もっと読む)

演算増幅器

【課題】極力小さな入力端子間電位差で、スルーレートを増大可能とする。

【解決手段】差動接続された第1及び第2のトランジスタ11,12の差動接続部分に第1の定電流源3が接続される一方、第1及び第2のトランジスタ11,12の差動接続部分と反対側に、カレントミラーを構成する第3及び第4のトランジスタ13,14が接続される一方、第1のトランジスタ11とダーリントン接続される第5のトランジスタ15が設けられると共に、そのダーリントン接続に電流供給可能に第2の定電流源4が設けられ、第2のトランジスタ12とダーリントン接続される第6のトランジスタ16が設けられると共に、そのダーリントン接続に電流供給可能に第3の定電流源5が設けられ、さらに、第5のトランジスタ15と差動対をなす電流補償用トランジスタ17が設けられ、その入力及び出力は、第2のトランジスタ12と同一に接続されてなるものである。

(もっと読む)

電力増幅器のバイアス回路

【課題】 アイドリング電流を精度良く一定に保つ。

【解決手段】 各々ダーリントン接続したパワートランジスタQ1、Q2とQ3、Q4をコンプリメンタリ接続したSEPP回路構成の出力段1と、前記パワートランジスタQ1、Q3のベース間にバイアス電圧を印加するバイアス回路11と、前記パワートランジスタQ2、Q4のエミッタと中点間に接続された一対の電流検出抵抗R1、R2と、一対の電流検出抵抗R1、R2の両端間電圧の大きさを検出する電圧検出回路12と、電圧検出手段12の検出電圧の極小ピークに基づき極小ピークが一定となるようにバイアス回路11を制御するバイアス電圧制御回路14と、を備え、バイアス電圧から電源回路20により電圧検出回路12の動作電源を作成した。

(もっと読む)

容量性負荷の充放電回路

【課題】容量性負荷の充放電回路における省電力効果を高めること。

【解決手段】容量性負荷の充放電回路は、充放電部と、蓄電素子と、電位調整部と、経路選択部とを有する。充放電部は、容量性負荷の電位がアナログ信号の電位変化パターンに倣って変化するように容量性負荷に対する充放電を行う。蓄電素子は、電源部からの電流によって充電されるとともに容量性負荷に対する充電時の電流源となる。電位調整部は、蓄電素子が有する低電位側端子の電位を、アナログ信号の電位よりも所定量低くするように調整する。経路選択部は、容量性負荷からの電荷を電源部と蓄電素子の少なくとも一方に流す回生経路と、容量性負荷からの電荷をグランド側に流す放電経路とを、アナログ信号の電位に応じて選択する。

(もっと読む)

改良された指数関数電流発生器と方法

【課題】ImがIbleedより小さいときでさえ、比率が制御信号に指数関数的に関連する電流対を発生させる。

【解決手段】対の比率が制御信号に指数関数的に関係する電流対Ip、Imを発生する装置および方法であって、ここにIpまたはImのいずれかは最小値より大きいかまたは最大値より小さい。装置はImまたはIpの値を感知するために使用される帰還修正回路を含む。感知されたImまたはIpの値が最小値より小さいかまたは最大値より大きいとき、修正回路はブースト電流Iboostを供給する。Iboostは好ましくは所望値およびIpまたはImの差に比例するよう維持される。

(もっと読む)

増幅回路および光変調器用ドライバ回路

【課題】大振幅出力および広帯域周波数特性を確保することができ、特に光変調器のドライバICに適用可能な増幅回路を提供する。

【解決手段】増幅回路は、入力段トランジスタ11と出力段トランジスタ12とを含み、入力された信号を入力段トランジスタ11および出力段トランジスタ12で増幅して出力する多段増幅部10と、多段増幅部10の出力を、該多段増幅部における出力段トランジスタ12の入力に帰還する帰還部20と、を備える。帰還部20は、第1帰還トランジスタ21a、第2帰還トランジスタ21bおよび帰還抵抗RFを含み、多段増幅部10の出力を、第1帰還トランジスタ21a、第2帰還トランジスタ21bおよび帰還抵抗RFを介して出力段トランジスタ12の入力に帰還する。

(もっと読む)

モータドライバ回路

【課題】簡素な構成でクロスオーバー歪みを抑制することができるシングルエンドプッシュプル方式のモータドライバ回路の提供。

【解決手段】モータドライバ回路1は、入力される信号を増幅して出力する増幅回路2と、増幅回路2から出力される信号が入力されるコンプリメンタリ回路3と、増幅回路2、及びコンプリメンタリ回路3の間に介在配置される介在回路4とを備える。介在回路4は、増幅回路2から出力される信号が非反転入力端子に入力され、コンプリメンタリ回路3に対して信号を出力するオペアンプ41,42を備える。オペアンプ41は、出力端子から反転入力端子に向かう方向を順方向として負帰還部に設けられるダイオード411を備える。オペアンプ42は、出力端子から反転入力端子に向かう方向を逆方向として負帰還部に設けられるダイオード421を備える。

(もっと読む)

アクティブバラン回路

【課題】アクティブバラン回路をMMIC化が容易な小型の構成にする。

【解決手段】平衡入力の一方を増幅し180度位相が回転した信号を取り出すN形電界効果トランジスタを有する第1の増幅回路と、平衡入力の他方を増幅し同位相の信号を取り出すP形電界効果トランジスタを有する第2の増幅回路と、第1および第2の増幅回路の出力信号を合成して不平衡出力として取り出す合成回路を備えたものである。

(もっと読む)

オーディオ用増幅装置

【課題】伝送ラインに短絡が生じた場合に、オーディオアンプを過電流から保護するとともに、過電流の保護状態から自動復帰することができるオーディオ用増幅装置を提供する。

【解決手段】オーディオ信号を増幅し、スピーカが接続された伝送ラインに供給するデジタルアンプ12と、伝送ラインの短絡を検出する短絡検出部22と、オーディオ信号をデジタルアンプ12に入力する入力手段であって、短絡検出部22による検出結果に基づいて当該デジタルアンプ12へのオーディオ信号の入力をミュートさせる入力制御手段と、伝送ラインの短絡が検出されてから経過した経過時間を計測する経過時間計測部24により構成される。入力制御手段は、上記経過時間に基づいて、オーディオ信号の入力ミュート処理を終了する。

(もっと読む)

広帯域増幅回路

【課題】広帯域増幅回路の設計自由度を大きくすること。

【解決手段】この広帯域増幅回路は、入力端にRF信号が入力される第一のバイポーラトランジスタ11と、前記第一のバイポーラトランジスタ11のコレクタに接続されたトランジスタ出力回路22と、前記トランジスタ出力回路22の出力端と前記第一のバイポーラトランジスタ11のベースとの間に接続された帰還回路とを備える。帰還回路は、第一のバイポーラトランジスタ11の入力端に一端が接続された第一の抵抗R3と、トランジスタ出力回路22の出力端に一端が接続され他端が第一の抵抗R3の他端に接続された第二の抵抗R1との直列接続回路で構成され、第一の抵抗R3と第二の抵抗R1との接続点とグラウンドとの間に第三の抵抗R2を設けたものである。

(もっと読む)

半導体回路装置

【課題】差動増幅回路が形成されてなる半導体回路装置であって、回路の動作スピードと安定性を両立させることができると共に、適用回路に制限がなく、安価に製造することのできる半導体回路装置を提供する。

【解決手段】差動増幅回路100aにおける2つの入力トランジスタQ1,Q2にバイアス電流Ibを供給する電流供給トランジスタQ3pが、マルチコレクタのバイポーラトランジスタからなり、電流供給トランジスタQ3pの第1コレクタc1が、2つの入力トランジスタQ1,Q2の各エミッタに共通接続され、第1コレクタc1と電流供給トランジスタQ3pの第2コレクタc2との間で、寄生抵抗Rpが形成され、第2コレクタc2が、2つの入力トランジスタQ1,Q2に入力が無い状態で、第1コレクタc1と同電位に設定されてなる半導体回路装置100とする。

(もっと読む)

オペアンプ

【課題】入力回路によるオペアンプの動作電流のバラツキが抑えることができ、該オペアンプの出力の高精度化を図ることが可能となり、部品点数を削減することができる。

【解決手段】入力信号が入力される複数の入力回路11・12を備え、前記各入力回路11・12に接続される定電流回路15と、前記複数の入力回路11・12に入力された入力信号の中から、必要な入力信号を選択する選択手段21と、選択された入力信号が入力される差動増幅回路13とを備えるオペアンプ。

(もっと読む)

ESD保護回路

電圧過負荷保護回路、RF入力ピン用ESD保護回路、および分布増幅器用ユニット保護セルとして使用するための、改善された保護回路が提供される。好ましくは、上記保護回路は、スイッチをトリガするために使用される正閾値電圧トリガを含み、該トリガは抵抗器と直列のダイオードストリングを含み、該スイッチは単一のリバースダイオードと直列のバイポーラトランジスタを含む。あるいは、前記トリガは、単一のダイオードと単一の抵抗器とを含み、単一のリバースダイオードと直列のダーリントンペアトランジスタをトリガするために使用される。別の実施形態では、ダーリントンペアトランジスタスイッチはコンデンサによりトリガされる。分布増幅器との使用において、上記ESD保護回路は、好ましくは分布増幅器の擬似伝送線内に組み込まれる。  (もっと読む)

(もっと読む)

光電流増幅回路、及び光ピックアップ装置

【課題】 複数の受光素子からそれぞれ得られる光電流の一つ以上を選択的に増幅し、かつ小規模に実現可能な光電流増幅回路を提供する。

【解決手段】 複数の受光素子351、352と、入力及び出力の間がゲイン抵抗360で接続されている増幅回路364と、受光素子ごとに設けられ、対応する受光素子と前記増幅回路の入力との間に接続される素子選択スイッチ353、354とを備え、前記ゲイン抵抗360はオンされる素子選択スイッチを介して対応する受光素子の光電流を供給し、前記増幅回路364は前記ゲイン抵抗360に流れる光電流を電圧信号に増幅する。

(もっと読む)

半導体集積回路

【課題】電源電圧が低電圧の場合でも、入力電圧範囲を広く使用可能で、安定した利得のオペアンプを有した半導体集積回路を提供することを目的とする。

【解決手段】本実施例の半導体集積回路は、入力端子1、2にそれぞれ供給された入力信号を差動増幅する入力回路部100、入力回路部100によって増幅された信号をシングルエンド出力にするための能動負荷部101、能動負荷部101用のバイアス電流を流すための回路であるバイアス回路部102、能動負荷部101からのシングルエンド出力を増幅して出力端子3を介して外部に出力する第1の増幅部200、第1の増幅部200に接続されて外部からの電流を出力端子3を介して流入させる第2の増幅部300を備える。

(もっと読む)

FETバイアス回路

【課題】FET増幅回路の増幅用FETに、個別に調整することのないバイアス電圧を印加することができるFETバイアス回路を実現する。

【解決手段】FETバイアス回路に、ゲートが増幅用FETのゲートとソースが増幅用FETのソースとに各々接続され、バイアス電圧に対するドレイン電流が増幅用FETのドレイン電流に略比例するモニタ用FETと、モニタ用FETに流れるドレイン電流が所定の動作クラスになるようバイアス電圧をモニタ用FETに印加することにより、増幅用FETが所定の動作クラスになるバイアス電圧を印加する定バイアス回路と、を備える。

(もっと読む)

フィルタ処理を一体化して寄生静電容量が低減されたトランスインピーダンス増幅器

フィルタ処理を一体化したトランスインピーダンス増幅器(TIA)。コンデンサがTIAに集積化され、且つ電源とTIAの内部接地とに接続される。トランスインピーダンス増幅器の電源上のノイズは、電源ノイズが低減されるように、コンデンサによってフィルタ処理される。集積型コンデンサは接地ノイズも低減する。集積型コンデンサは他の回路から受け取る可能性のある共通モードノイズの影響も低減する。  (もっと読む)

(もっと読む)

高速変化耐性微分レベルシフトデバイス

【課題】高周波で作動でき、電力散逸量が少なく、共通モードの変化に対して耐性を有するレベルシフトデバイスを提供する。

【解決手段】第1電圧レベル(13)で作動する入力側(14)と、第2電圧レベル(53)で作動する出力側(54)と、入力側と出力側とを接続するレベルシフト回路(48)とを備え、入力回路は、第1電圧レベルを基準とする入力信号(14)を受信し、入力信号の変化に対応する出力信号を発生する。レベルシフト回路は、MOSFET(28)を備え、MOSFETのゲートは、入力回路の各出力に接続され、ソース−ドレインパスは、第2電圧と第1電圧の基準との間に結合されている。出力側は、微分回路トポロジー(50)を有し、入力信号の変化を対応する信号をサンプリングし、その変化の間のサンプルをホールドする第1回路(56)と、微分された形態でホールドされたサンプル信号を受信して、シングルエンド形態に変換する出力回路(54)を有している。

(もっと読む)

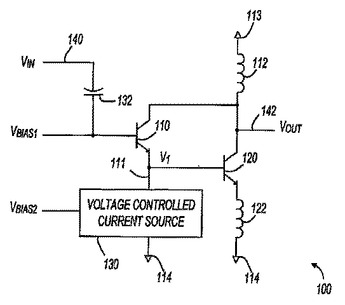

バイアスされたダーリントン・トランジスタ対、方法およびシステム

増幅器は、ダーリントン・トランジスタ対(110,120)および入力トランジスタ(110)中のバイアス電流を増加させるためのバイアスを与えるネットワークを含む。回路(100)は、入力トランジスタ(110)、第2トランジスタ(120)、無線周波数(RF)チョーク(112)、縮退インダクタ(122)、キャパシタ(132)および電圧制御電流源(130)を含む。入力トランジスタ(110)および第2トランジスタ(120)は、コレクタがノード(142)でともに結合され、入力トランジスタ(120)のエミッタがノード(111)に結合されて、ダーリントン・トランジスタ対を形成するために結合される。  (もっと読む)

(もっと読む)

1 - 20 / 20

[ Back to top ]