Fターム[5J500AQ03]の内容

Fターム[5J500AQ03]に分類される特許

141 - 160 / 202

電子デバイス

【課題】移動機のマルチバンド化への対応により2系統以上の高周波電力増幅器を搭載する必要がある場合においても、薄型で高周波特性に優れた高周波電力増幅器を低コストで提供する。

【解決手段】インピーダンス変換回路36は、モノリシックマイクロ波集積回路59及び60として構成された5系統の高周波電力増幅器の出力端子73A〜73Eから出力された高周波信号を、当該各出力端子73A〜73Eに相対するように配置された複数の入力端子77A〜77Eから入力してインピーダンス変換を行う。

(もっと読む)

電子回路及びそのための方法

電子回路は、機能モジュール(10)と条件シグナリングモジュール(20)と基準モジュール(30)と制御回路40とを備えている。条件シグナリングモジュール(20)は、機能モジュールの局所のPVT条件を指し示す指示信号(Imeas)を生成する。PVT条件とは、モジュールに関連する一連の条件であって、当該モジュールに供給される電圧、当該モジュールが占める領域内の温度、及び、当該領域に関連するプロセス条件のうち少なくとも1つを含むものである。基準モジュール(30)は、PVT条件にほぼ依存しない値を有する基準信号(Iref)を生成する。制御回路(40)は、指示信号(Imeas)と基準信号(Iref)とを比較し、機能モジュールに対する制御信号(pvt<1>,…,pvt<n>)を生成する。  (もっと読む)

(もっと読む)

増幅器

【課題】装置の小型化が可能で、かつ、コスト低減が可能な定振幅波合成形の増幅器を提供する。

【解決手段】一つの入力信号を二分配した分配器1からの一方の信号を増幅する第1の増幅器3aと、他方の信号を増幅する第2の増幅器3bと、2系統の第1、第2の増幅器3a、3bからのそれぞれの出力信号を合成器2で合成して出力する定振幅波合成形の増幅器として、第1、第2の増幅器3a、3bを、1個のパッケージに内蔵された少なくとも2個の増幅素子によって構成する。また、第1、第2の増幅器3a、3bをそれぞれ構成する前記増幅素子を、互いに密着して実装する。さらに、第1、第2の増幅器3a、3bをそれぞれ構成する前記増幅素子を、電界効果トランジスタ又はバイポーラトランジスタを用いて構成する。

(もっと読む)

高出力集積RF増幅器

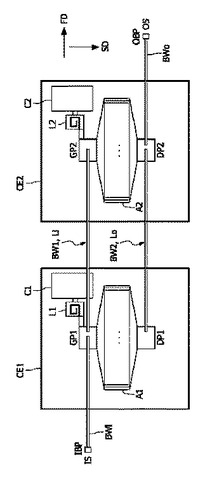

入力ボンド・パッド(IBP)と第1の方向(FD)に互いに変位された複数のセル(CE1、CE2)と出力ボンド・パッド(OBP)とをこの順序で第1の方向(FD)に備えた集積HF増幅器構造体。セル(CE1、CE2)の各々は入力パッド(GP1、GP2)とアクティブ領域(A1、A2)と出力パッド(DP1、DP2)とを有する増幅器を備える。アクティブ領域(A1、A2)は、入力パッド(GP1、GP2)と出力パッド(DP1、DP2)の間に配置され、入力パッド(GP1、GP2)とアクティブ領域(A1、A2)と出力パッド(DP1、DP2)は第1の方向(FD)に対してほぼ直角な第2の方向(SD)に互いに変位される。第1の回路網(N1)は、複数のセル(CE1、CE2)のうちの隣接するセルの入力パッド(GP1、GP2)を相互接続するための第1の相互接続手段(Li、Ci;Li1、Li2、Ci1)を備え、且つ第1の方向(FD)に延びる。第2の回路網(N2)は、複数のセル(CE1、CE2)のうちの隣接するセルの出力パッド(DP1、DP2)を相互接続するための第2の相互接続手段(Lo、Co;Lo1、Lo2、Co1)を備え、且つ第1の方向(FD)に延びる。第1の回路網(N1)及び第2の回路網(N2)は、すべての相互接続されたセル(CE1、CE2)について、出力ボンド・パッド(OBP)にて、入力ボンド・パッド(IBP)での同じ入力信号(IS)に対して等しい位相シフト及び振幅を有する出力信号(OS)を得るように構成される。特定のバイアス及び位相シフト条件において、構造体は出力バックオフでの効率が改善されたドハティ増幅器を実現する。  (もっと読む)

(もっと読む)

スイッチトキャパシタ回路

【課題】 SOI基板上に製造される差動構成のスイッチトキャパシタ回路において、一端がVssとVdd間の中間電位であるアナロググランドに接続されるスイッチに用いるトランジスタとして、スイッチオフ時のリーク電流を少なくする。

【解決手段】 SOI基板上に製造されたトランジスタであり、活性領域中に形成されたチャネル領域、ソースおよびドレインと、チャネル領域上に形成されたゲート電極と、チャネル領域に接し、かつソースおよびドレインに接しない活性領域中に形成され、チャネル領域と同一伝導型の第1の領域と、チャネル領域に接し、かつソースおよびドレインに接しない活性領域中に形成され、ソースおよびドレインと同一伝導型の第2の領域とを有し、第1の領域と第2の領域とは金属コンタクトにより電気的に相互に接続されてチャネル領域に対する電位固定作用を有するソースタイトランジスタを用いる。

(もっと読む)

伝送線変圧器を用いた電力増幅器

【課題】追加的なスイッチなしにも、出力電力の全領域における効率を増大させて動作領域を拡張させられる無線通信システム用の電力増幅器を提供する。

【解決手段】駆動増幅ユニット及び電力増幅ユニットから構成されており、前記駆動増幅ユニット及び電力増幅ユニットに整合回路及び電力結合器がそれぞれ連結されることで、前記駆動増幅ユニットが前記電力増幅ユニットを駆動するとともに、整合回路及び電力結合器を介して出力端子に出力信号を出力する電力増幅器において、前記整合回路及び電力結合器は、出力端子に連結される2次側伝送線と、前記2次側伝送線の両側に対応してそれぞれ配置されるもので、互いに異なる寄生成分を有し、一側に駆動増幅ユニットが連結され、他側に電力増幅ユニットが連結される複数個の1次側伝送線と、を含む伝送線変圧器であることを特徴とする伝送線変圧器を用いた電力増幅器を構成する。

(もっと読む)

ドハティ増幅器

集積ドハティ増幅器構造体は、入力ボンドパッド(IBP)と、出力ボンドパッド(OBP)とを備える。第1のトランジスタ(T1)は、ドハティ増幅器のピーク増幅段を形成し且つドハティ増幅器の入力信号である第1の入力信号(IS1)を受け取るための制御入力(G1)とドハティ増幅器の出力で増幅された第1の入力信号(OS1)を供給するための出力(D1)とを有する。第2のトランジスタ(T2)は、ドハティ増幅器のメイン増幅段を形成し且つ第2の入力信号(IS2)を受け取るための制御入力(G2)と増幅された第2の入力信号(OS2)を供給するための出力(D2)とを有する。第1の入力信号(IS1)と第2の入力信号(IS2)とは90度の位相オフセットを有する。第1のボンドワイヤ(BW1)は、第1のインダクタンス(L1)を形成し、第1の方向に延在するとともに、入力ボンドパッド(IBP)と第1のトランジスタ(T1)の制御入力(G1)との間に配置される。第2のボンドワイヤ(BW2)は、第2のインダクタンス(L2)を形成し、第1の方向に延在するとともに、出力ボンドパッド(OBP)と第1のトランジスタ(T1)の出力(D1)との間に配置される。第3のボンドワイヤ(BW3)は、第3のインダクタンス(L3)を形成し、第1の方向に対して略垂直な第2の方向に延在するとともに、第1のトランジスタ(T1)の出力(D1)と第2のトランジスタ(T2)の出力(D2)との間に配置される。  (もっと読む)

(もっと読む)

高出力増幅器

【課題】X帯からKu帯にわたる高周波領域で動作する大きなサイズのパワートランジスタを用いた高出力増幅器において、低インピーダンスの入力整合回路を実現すると共に実装ばらつきを低減する。

【解決手段】ソース端子とゲート端子とが複数交互に配置されたトランジスタ1と入力整合回路2とを含む高出力増幅器であって、入力整合回路2において、トランジスタ1のソース端子に対向する位置にグランドに導通したビア8を設け、トランジスタ1のゲート端子に対向する位置に信号線としての導体6を設け、ソース端子と当該ソース端子に対向する位置に設けられたビア8とをソースワイヤ12を用いて接続し、ゲート端子と当該ゲート端子に対向する位置に設けられた導体6とをゲートワイヤ13を用いて接続する。

(もっと読む)

半導体集積回路

【課題】トランジスタの個数の増加を有効に抑制しながら、電流比を大きく設定することができ、そのレイアウトパターンが占める面積の増加を抑えることができる半導体集積回路を提供すること。

【解決手段】電流経路が所定電位ノードと第1出力ノードとの間に直列接続されると共に制御電極が前記第1出力ノードに共通接続された複数の第1トランジスタと、電流経路が前記所定電位ノードと第2出力ノードとの間に並列接続されると共に制御電極が前記第1出力ノードに共通接続された複数の第2トランジスタとを備える。前記第1トランジスタおよび前記第2トランジスタの各電気的特性は互いに同等に設定される。

(もっと読む)

可変利得増幅器及びこの可変利得増幅器を備えた通信装置

【課題】広い可変利得範囲を得ることができ、さらに、増幅段トランジスタの切替時における線形性の劣化を抑制することが可能な可変利得増幅器を提供すること。

【解決手段】可変利得増幅器1は、信号入力端INに接続された増幅段トランジスタQと、この増幅段トランジスタQの出力端にカスコード接続された複数のカスコード段トランジスタTとを含み、さらに、減衰器ATを介して並列接続された複数のカスコード増幅器Ampを有する。さらに、各カスコード増幅器Ampに含まれる複数のカスコード段トランジスタTのON/OFF動作を制御するゲート電位制御回路20と、選択された1つの増幅段トランジスタQのみがONとなるように、複数の増幅段トランジスタQのON/OFF動作を制御するベース電流制御部11を備えている。

(もっと読む)

サーキュレータタイプのモノリシック装置

【解決手段】本発明は、高周波信号を送受信するためにアンテナ(2) に接続されることが意図され、サーキュレータの出力(S) に信号を供給することが可能なデュアル−インプット差動増幅器(31)と、第1、第2及び第3アクセス端子を夫々含む2つの3dB カプラー(A,B) とを備えたモノリシックサーキュレータに関し、第2端子はサーキュレータの1つの入力(E) に接続され、第3端子は増幅器の1つの入力に夫々接続され、第1端子は、アンテナとアンテナのインピーダンスに近いインピーダンスを有する負荷要素(30)とに夫々接続されることが意図されている。  (もっと読む)

(もっと読む)

通信用電力増幅器

【課題】デュアルバンド電力増幅器の最終段トランジスタにおける電流集中を、バンド間アイソレーションを劣化させることなく回避する。

【解決手段】最終段電力増幅トランジスタ(Trg3,Trd3)の単位トランジスタについて、最終出力増幅トランジスタ形成領域(PW3)内に単位トランジスタを交互にまたは取囲むように混在して配置する。また、これらの最終出力段トランジスタが結合する出力信号線の間に、インダクタンス素子(Lcc)を接続する。

(もっと読む)

定電流回路

【課題】定電流回路を構成するチップの面積縮小を図ることができる回路構成を提供する。

【解決手段】トランジスタ6のベース電流を流すための起動素子をツェナーダイオード7で構成する。そして、このツェナーダイオード7を構成する各拡散層20〜22をリーク電流が発生するような不純物濃度に設定する。このため、ツェナーダイオード7は、リーク電流分の電流を流し、かつ、ツェナーダイオード7の両端間に電位差(Vz×ツェナーダイオード7の個数)を発生させるため、抵抗と等価の役割を果たすことができる。このように、起動素子をツェナーダイオード7で構成することにより、起動素子を抵抗で構成する場合と比べて必要な面積を低減することが可能となる。したがって、定電流回路を構成するチップの面積縮小を図ることができる回路構成が可能となる。

(もっと読む)

低雑音増幅器

多数のゲインモードを有する増幅器であって、入力に接続されかつ並列に配置される複数のカスコード入力トランジスタと、入力トランジスタに接続されかつ可変インピーダンスを有するデジェネレーション段と、1つ以上の入力トランジスタのスイッチを切ってデジェネレーション段のインピーダンスを変えることによって、増幅器の異なるモードを切り替えるためのスイッチング手段とを含む増幅器。  (もっと読む)

(もっと読む)

基準電圧発生回路

【課題】デジタル回路と共に形成しても出力特性が安定している、バイポーラトランジスタ群で構成される基準電圧発生回路を作成する。

【解決手段】本発明の基準電圧発生回路は、第一導電型のコレクタ層と、上記コレクタ層の表面に形成された第一導電型のベース層と、上記ベース層の表面に形成された第一導電型のエミッタ層と、上記エミッタ層に接続された複数のエミッタ電極を含むバンドギャップリファレンス回路において、複数のエミッタ層が形成されたベース層が共通のものであることを特徴とする基準電圧発生回路である。

(もっと読む)

差動増幅器

【課題】高周波増幅回路の小形化と回路設計の容易化を図ること。

【解決手段】トランジスタQ1のエミッタ端子に接続されたコンデンサC1の他端はアースされている。同様に、トランジスタQ2のエミッタ端子に接続されたコンデンサC2の他端はアースされている。コンデンサC1とC2の容量は勿論同じである。また、トランジスタQ1のコレクタ端子は、インダクタL1を介して直流電源に接続される。同様に、トランジスタQ2のコレクタ端子は、インダクタL2を介して直流電源に接続される。図示する符号Vccは、その直流電源の給電電位(>0)を示している。トランジスタQ1,Q2のエミッタ端子は、何れもインダクタL0の同一端に接続されており、このインダクタL0の他端は、定電流路y1を介してアースされている。コンデンサC1、C2とインダクタL0によって、本差動増幅器100の共振周波数帯域が制限される。

(もっと読む)

半導体回路装置

【課題】差動増幅回路が形成されてなる半導体回路装置であって、回路の動作スピードと安定性を両立させることができると共に、適用回路に制限がなく、安価に製造することのできる半導体回路装置を提供する。

【解決手段】差動増幅回路100aにおける2つの入力トランジスタQ1,Q2にバイアス電流Ibを供給する電流供給トランジスタQ3pが、マルチコレクタのバイポーラトランジスタからなり、電流供給トランジスタQ3pの第1コレクタc1が、2つの入力トランジスタQ1,Q2の各エミッタに共通接続され、第1コレクタc1と電流供給トランジスタQ3pの第2コレクタc2との間で、寄生抵抗Rpが形成され、第2コレクタc2が、2つの入力トランジスタQ1,Q2に入力が無い状態で、第1コレクタc1と同電位に設定されてなる半導体回路装置100とする。

(もっと読む)

高周波電力増幅回路および高周波電力増幅用電子部品

【課題】増幅器としての周波数特性を劣化させることなくインピーダンス整合回路の小型化を図り、もって小型で低コストの高周波電力増幅回路およびこれを内蔵した高周波電力増幅用電子部品(RFパワーモジュール)を提供する。

【解決手段】 複数の増幅素子(11,12)が従属接続されてなる多段構成の高周波電力増幅回路において、最終段の増幅素子とそれよりも前段の増幅素子の電源電圧端子を別個に設け、最終段の増幅素子には前段の増幅素子よりも高い電源電圧を印加可能にする。また、最終段の増幅素子のサイズを前段の増幅素子と同程度まで小さくして、前段の増幅素子とのインピーダンス差が小さくなるように構成した。

(もっと読む)

カレントミラー回路、電流制御回路、および、LED駆動用半導体集積回路

【課題】 非常に高い精度のミラー比を実現できるカレントミラー回路を提供する。また、駆動電流を非常に高い精度で制御することのできるLED駆動用半導体集積回路を提供する。

【解決手段】 カレントミラー回路において、転写元の電流を流す第1電流経路(L0)と、転写先の電流を流す第2電流経路(L1)と、制御端子への入力により電流量を変化させるとともに互いの制御端子が結合された第1電流回路(M1,M2)および第2電流回路(M3,M4)と、第1電流経路(L0)と第2電流経路(L1)の接続を前記第1電流回路と前記第2電流回路とで互い違いに切り換えるスイッチ回路(SW1,SW2)と、第1および第2電流回路の制御端子の接続を切り換えるスイッチ回路(SW3,SW4)とを備え、これらスイッチ回路を所定周期で切り換えるように構成した。また、LED駆動用半導体集積回路において駆動電流を生成するために、上記のカレントミラー回路を基準電流を転写する回路として用いた。

(もっと読む)

半導体デバイス、そのバイアス抵抗調整方法、および、電子機器

【課題】信号増幅手段に対するバイアス抵抗調整を、精度を高く迅速に行う。

【解決手段】本方法は、信号増幅手段(たとえばFET)の信号入力端子(ゲート)を介してトリマブル抵抗に接続され、トリマブル抵抗の値を見積もる際の誤差となる当該信号増幅手段のインピーダンス(Rgs)を、当該FETに所定の出力経路電流(ドレイン電流Id)を流した状態で測定し、その測定値を用いてトリマブル抵抗の目標値を決定する第1ステップ(ST701〜ST714)と、第1ステップで決定された目標値が得られるように、ドレイン電流IdをFETに流さない状態でトリマブル抵抗の抵抗値を調整する第2ステップ(ST715〜ST717)と、を含む。

(もっと読む)

141 - 160 / 202

[ Back to top ]