Fターム[5J500AQ03]の内容

Fターム[5J500AQ03]に分類される特許

161 - 180 / 202

増幅回路

【課題】安定化を図りつつFETセルを均一動作して利得を向上させることのできる増幅回路を得る。

【解決手段】入力信号を複数の信号に分配して複数の分配端子12に出力する分配回路10と、分配回路10により分配された信号のそれぞれを増幅する複数のFETセル20と、複数のFETセル20により増幅されたそれぞれの信号を合成する合成回路30と、分配回路10の複数の分配端子12と複数のFETセル20との間に接続され、容量42およびインダクタ43の直列回路と、抵抗41との並列回路を有する複数の安定化回路40とを備えた増幅回路において、複数の安定化回路40のそれぞれは、接続されるFETセル20ごとに異なる素子値から構成された並列回路を有するものである。

(もっと読む)

カスコード接続回路

【課題】 利得、出力電力及び効率を劣化させることなく動作の安定性を向上させることができるカスコード接続回路を得る。

【解決手段】 2つの電解効果型トランジスタ(以下、「FET」という。)がカスコード接続されたカスコード接続回路であって、ソース端子が接地された第1のFETと、ソース端子が第1のFETのドレイン端子に接続された第2のFETと、第1のFETのソース端子と第2のFETのゲート端子との間に直列接続された第1の抵抗及び第1のコンデンサとを備え、第1の抵抗の抵抗値と第1のコンデンサの容量値との積が、動作周波数に対応する周期の0.1倍以下である。

(もっと読む)

高周波電力増幅器

【課題】マルチフィンガー型のトランジスタを用いた場合に、歪特性を改善することができる高周波電力増幅器を得る。

【解決手段】複数のトランジスタセルを電気的に並列接続したマルチフィンガー型のトランジスタと、複数のトランジスタセルのゲート電極に接続された入力側整合回路と、各トランジスタセルのゲート電極と入力側整合回路の間にそれぞれ接続された共振回路とを有し、共振回路は、トランジスタの動作周波数の2次高調波の周波数又は2次高調波の周波数を中心とした所定の範囲内で共振してゲート電極に短絡又は十分に低い負荷を与える。

(もっと読む)

直接取り付け型受信モジュールおよび試験方法

直接取り付け型光受信モジュール、および直接取り付け型光受信モジュールを試験するためのシステムおよび方法を提供する。光受信モジュールは、光検出器と、集積増幅回路を備えた集積回路と、少なくとも1つの集積コンデンサとを含むことが可能である。一実施例では、光検出器を集積回路に物理的に取り付けることが可能であり、光検出器の出力ポートを集積回路の入力ポートに電気的に結合することが可能である。別の実施例では、同調インダクタを含む再分配層を光検出器と集積回路との間に物理的に取り付けることが可能である。  (もっと読む)

(もっと読む)

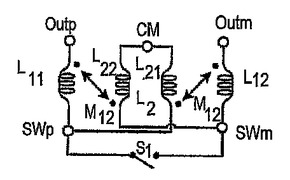

マルチバンド無線周波数動作用のインダクタ・デバイス

モノリシック平面インダクタのインダクタンスは、より小さなインダクタ部分(L11、L21、L22、L12)に分散される。より小さなインダクタ部分(L11、L21、L22、L12)は、インダクタを差動インダクタ・デバイスとして機能させるようなカスコード構成に設けられる。中間インダクタ部分(L21、L22)の間のノード(CM)はインダクタ・デバイスのコモン・モード・ポイントであり、典型的には信号接地に接続される。インダクタ部分(L12、L11)の外側端にあるノード(Outm、Outp)は差動出力部であり、例えば、デバイス自体と次段のデバイス(例えばミキサの入力段)とのインターフェースにある増幅器デバイスの出力ノードである。インダクタ部分のうちの幾つかは、1つ又はそれ以上の高周波数帯域動作のために、1つ又はそれ以上のステップにおけるコモン・モード・ポイントに関して対称的にバイパス又はショートカットされる(S1)ように配置される。スイッチング可能な対称的ショートカットにより、制御可能なインダクタンス・ステップを生成することができる。コモン・モード信号は、制御状態に関わりなく、同じインダクタンスの影響を受ける。  (もっと読む)

(もっと読む)

増幅回路

【課題】 二段増幅回路において、回路素子数を削減しながらも、必要な回路利得と周波数特性が得、コストダウンを図る。

【解決手段】 本発明の増幅回路は、入力信号を検出する検出器と、前記検出器と接続され、その出力電流を増幅するための帰還増幅回路とを備えた増幅回路であって、前記増幅回路の出力と基準電位との間に設けられた分圧用抵抗を備え、前記分圧用抵抗の一端が前記出力側に接続され、前記分圧用抵抗の分割点に前記帰還増幅回路の抵抗が接続され、前記分圧用抵抗の他端が前記帰還増幅回路の入力に接続されたことを特徴としている。

上記構成により、回路素子数を削減し、必要な回路利得と周波数特性を得られる事が出来、コストダウンもはかれる。

(もっと読む)

増幅器

常に信号の増幅動作を行うキャリア増幅器と、高電力出力時のみに動作するピーク増幅器と、キャリア増幅器とピーク増幅器の出力を合成して出力する合成器と、入力信号をキャリア増幅器側とピーク増幅器側に分配する分配器とを含んで構成される。キャリア増幅器およびピーク増幅器は1個のパッケージ1(1パッケージトランジスタ)に内蔵される。  (もっと読む)

(もっと読む)

高周波増幅器

【課題】高周波増幅器に用いる増幅トランジスタの異常発振と熱暴走とを防止して高性能動作を安定に維持できると共に小型化を図れるようにする。

【解決手段】高周波信号を増幅する増幅トランジスタ1と、一方の端子(アノード)が増幅トランジスタ1のベース端子と接続され、他方の端子(カソード)が高周波信号を受けるダイオード2Aとを有している。ダイオード2Aの抵抗成分を利用して増幅トランジスタ1の安定化が図られ、且つダイオード2AのPN接合容量により、所望の高周波信号を通過させることができる。また、ダイオード2AのPN接合容量は、MIMキャパシタと同一の面積であっても、MIMキャパシタと比べて約10倍の容量を確保できるため、高周波増幅器の小型が可能となる。

(もっと読む)

バイポーラトランジスタおよび高周波増幅回路

【課題】高周波増幅回路に悪影響を与えること無く、バイポーラトランジスタの熱暴走を防止することが可能なバイポーラトランジスタおよび高周波増幅回路の提供を目的とする。

【解決手段】直流バイアスが供給される直流バイアス(DC)端子3と、DC端子3に接続されたDC用ベース電極6と、高周波信号が供給される高周波電力(RF)端子4と、RF端子4に接続されたRF用ベース電極7と、DC用ベース電極6とRF用ベース電極7とに接続されているベース層8とを有する。

(もっと読む)

差動インダクタを用いた低雑音増幅器

低雑音増幅器は、各カスコードトランジスタ(M3,M4)へ接続されたドレインを有する一対の差動増幅器トランジスタ(M1,M2)を有する。増幅器トランジスタ(M1,M2)のゲートはRF入力信号を受信する入力差動インダクタ(L1)へ接続され、一方、増幅器トランジスタのソースはソース差動インダクタ(L2)へ接続される。カスコードトランジスタ(M3,M4)のドレインは、負荷差動インダクタ(L3)と、2つのソース・フォロワ(MO1,MO2)を有するバッファ回路(260)の入力部とへ接続される。差動増幅器のテール電流は電流ミラー(M5,M6)を介して電流源(272)によって供給される。  (もっと読む)

(もっと読む)

高周波増幅器および通信機器

【課題】半導体基板上に形成した高周波増幅器のベース端子およびエミッタ端子から基板方向への信号漏洩による雑音指数の劣化を防止する。

【解決手段】インピーダンス素子60とインピーダンス素子61はアルミニウムや銅などの低抵抗率の金属配線を使用して配線長と配線幅と配線形状を変化させ、拡散容量50は面積を変化させることにより高周波信号に対する交流的インピーダンスを可変できる。インピーダンス素子60と拡散容量50とインピーダンス素子61により高周波信号に対する交流的インピーダンスを低減し、第1のトランジスタ15のベース端子からエミッタ端子を介し外部の接地端子への信号経路を作ることでベース端子用パッド20に外部より入力した高周波信号のうち、半導体基板の絶縁膜における絶縁膜容量を介し基板裏面方向に通過しようとする信号成分を低減あるいは遮断し、基板裏面方向への信号漏洩をなくし雑音指数の劣化を防止する。

(もっと読む)

差動増幅回路及び無線通信装置

【課題】高周波特性の良好な差動増幅回路を提供する。

【解決手段】半導体チップ上に再配線層が形成されるチップサイズパッケージを備える半導体基板上に形成する差動増幅回路において、差動対をトランジスタQ1とトランジスタQ2により構成し、ペアのトランジスタQ1,Q2のエミッタを夫々別のボンディングパッド201,202及びCSP出力端子205,206に接続して接地することにより、エミッタ部での共通インピーダンスを無くすようにする。

(もっと読む)

トランジスタ回路

【課題】バイアス回路の規模拡大に伴うトランジスタの半導体基板占有面積の増大を抑え、バイアス回路の小型化を図ることを可能としたトランジスタ回路を提供する。

【解決手段】ドレイン端子(101)と、第1および第2のソース端子(107)(109)と、第1および第2のゲート端子(103)(105)と、半導体トランジスタ領域(111)を備え、前記トランジスタ領域には前記ドレイン端子(101)に接続されたドレイン電極(102)と、前記第1のソース端子(107)に接続された第1のソース電極(108)と、前記第2のソース端子(109)に接続された第2のソース電極(110)と、前記第1のゲート端子(103)に接続された第1のゲート電極(104)と、前記第2のゲート端子(105)に接続された第2のゲート電極(106)が形成されるようにした。

(もっと読む)

電力増幅器

【課題】放熱と接地の良さを維持しながら、高出力化が可能な電力増幅器を提供する。

【解決手段】バイポーラトランジスタ素子のエミッタ電極4にバンプ8が備えられて近距離接地されており、これらを複数個組み合わせて1つの構成単位としてのユニットセル7を形成することにより放熱と接地の良さを維持しながら、高出力化が可能な電力増幅器が実現する。

(もっと読む)

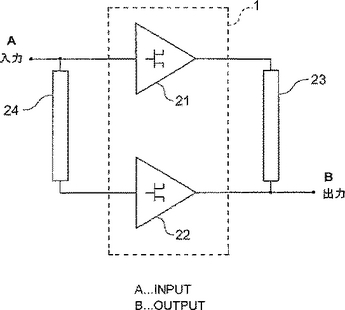

増幅器、及びそれを搭載する受信回路

【課題】 可変インダクタを利用して外部から利得を高精度で調節でき、かつ入力信号の変動に関わらず入力インピーダンスを安定に維持できる増幅器、を提供する。

【解決手段】 LNA(1)は主回路(1A)と補助回路(1B)とを含む。主回路(1A)と補助回路(1B)とは絶縁されている。主回路(1A)は、アンテナにより受信された無線周波信号(Vin)を増幅して出力する(Vout)。主インダクタ(Lm)と補助インダクタ(La)とは同軸の薄膜インダクタであり、磁気的に結合する。利得制御信号(GC)はRSSI装置により生成され、そのレベルが増幅された無線周波信号(Vout)の強度を示す。可変電流源(11)は利得制御信号(GC)に従い、補助インダクタ(La)の電流量を調節する。

(もっと読む)

チョッパ増幅回路

【課題】回路構成が簡単であって、しかも高い信頼性を有し、低電圧で動作可能なチョッパ増幅回路を提供する。

【解決手段】チョッパ変調器1は入力信号を所定の制御信号に従ってチョッパ変調してチョッパ変調信号を出力する。スイッチドオペアンプ3の増幅回路はチョッパ変調器1から出力されるチョッパ変調信号を増幅して増幅されたチョッパ変調信号を出力する。スイッチドオペアンプ3のチョッパ復調器4は増幅回路から出力される増幅されたチョッパ変調信号を、制御信号に従ってチョッパ復調して復調された出力信号を出力端子からチョッパ増幅された出力信号として出力する。チョッパ変調器5はチョッパ復調器4から出力される復調された信号を、制御信号に従ってチョッパ変調してチョッパ変調信号を増幅手段の入力端子に出力する。

(もっと読む)

高周波電力増幅回路

【課題】 出力電力を検出してフィードバック制御を行なう無線通信システムにおいて、製造ばらつきにより増幅素子の特性がばらついても安定した高周波電力増幅特性を得ることができる高周波電力増幅回路を提供する。

【解決手段】 少なくとも最終段の電力増幅用素子(211)を直列形態の2つの電界効果トランジスタにより構成し、該2つの電界効果トランジスタの一方の制御端子に増幅されるべき高周波信号を入力して共通ソース・ドレイン端子から出力信号を取り出すとともに、該出力信号を抵抗素子(Ri)を介して前記出力電力検出回路(220)の検波用トランジスタの制御端子に入力させるように構成した。

(もっと読む)

半導体装置および高周波電力増幅モジュール

【課題】 高周波電力増幅モジュールにおける電力増幅の効率を向上させるとともに、チップのレイアウト面積を縮小化する。

【解決手段】 半導体チップCHの中央部には、パワーアンプ領域38が位置している。このパワーアンプ領域38は、高周波信号を増幅するパワーアンプ32aが形成される領域であり、この領域内にセンスアンプ32bが形成されている。すなわち、パワーアンプ32aが形成される領域とセンスアンプ32bが形成される領域とがそれぞれ独立したセルではなく、同一のセル内に形成されている。

(もっと読む)

高周波複合部品及びそれを用いた携帯無線機

【課題】 小型化、軽量化を図ることができるとともに、高性能化が可能な高周波複合部品及びそれを用いた携帯無線機を提供する。

【解決手段】 高周波複合部品10は、高周波回路部の一部を構成する低雑音増幅器LNAと帯域通過フィルタBPFとからなり、入力端子IN、出力端子OUT、制御端子Vcc1,Vcc2を備える。低雑音増幅器LNAはトランジスタQ1,Q2、インダクタL1、コンデンサC1〜C3、抵抗R1〜R4で構成され、帯域通過フィルタBPFはストリップラインST1〜ST3、インダクタL2、コンデンサC4〜C8で構成される。なお、低雑音増幅器LNAと帯域通過フィルタBPFとは、マッチング用コンデンサC9を介して接続されている。

(もっと読む)

半導体装置およびその製造方法ならびに電子装置

【課題】 線型の電力増幅器において、高周波特性に影響を及ぼす帰還容量のドレイン電圧依存性を抑えて歪み特性の劣化を防ぐことができる技術を提供する。

【解決手段】 半導体基板40上にゲート絶縁膜44を介してゲート電極45を形成する。このゲート電極45のドレイン領域側の側壁を覆うようにフィールドプレート電極59aを形成する。そして、このフィールドプレート電極59aの電位をフローティング状態にする。フィールドプレート電極59aは、例えばポリシリコン膜より形成される。

(もっと読む)

161 - 180 / 202

[ Back to top ]