Fターム[5J500AQ03]の内容

Fターム[5J500AQ03]に分類される特許

61 - 80 / 202

テスト回路および光ディスク装置

【課題】受光素子を使用する増幅回路の特性の検査に加え、当該受光素子の特性の検査を行なうことを可能とする。

【解決手段】テスト回路100は、受光素子PD1の特性と同等の特性を有するダミー受光素子PD_Dを供える。カレントミラー回路110は、バイポーラトランジスタQ2を利用して、増幅回路10の特性を検査するための検査電流を、増幅回路10において生じさせる。カレントミラー回路110のバイポーラトランジスタQ1は、バイポーラトランジスタQ1内に電流を流さない状態になることにより、ダミー受光素子PD_Dの特性を検査するための電流をダミー受光素子PD_D内に生じさせる。

(もっと読む)

電流電圧変換回路

【課題】非常に低い電流値に対してもリニアリティーを持つ対数圧縮式の電流電圧変換回路を提供すること。

【解決手段】電流入力端子1と、基準電圧入力端子2と、電圧出力端子3と、P型半導体基板上に形成された演算増幅器4およびNPN型トランジスタ5とを備える。演算増幅器4の反転入力端子は電流入力端子1に、非反転入力端子は基準電圧入力端子2に、出力端子は電圧出力端子3にそれぞれ接続される。NPN型トランジスタ5のコレクタは電流入力端子1に、ベースは基準電圧入力端子2に、エミッタは電圧出力端子3にそれぞれ接続される。NPN型トランジスタ5は、エミッタに相当するN型エピタキシャル層と、N型エピタキシャル層上に選択的に形成され、ベースに相当するP型拡散層と、P型拡散層上に選択的に形成され、コレクタに相当するN型拡散層とから構成される。

(もっと読む)

広帯域増幅器

【課題】チップ面積の増大を招くことなく、低損失で広帯域な出力整合を実現する。

【解決手段】増幅対象の信号を相互に180度の位相差を有する信号に分配する180°ハイブリッド1と、180°ハイブリッド1から出力された一方の分配信号がゲート電極Gに与えられるトランジスタ3と、180°ハイブリッド1から出力された他方の分配信号がゲート電極Gに与えられ、ドレイン電極Dがトランジスタ3のドレイン電極Dと接続されているトランジスタ4とを設け、180°ハイブリッド6がトランジスタ3のドレイン電極Dから出力された信号とトランジスタ4のドレイン電極Dから出力された信号の位相を揃えて合成する。

(もっと読む)

電力合成増幅器

【課題】 電力分配器で分岐された複数の増幅回路の相互干渉を防止し、伝送線路長の短い電力合成増幅器を提供する。

【解決手段】 電力分配回路から分岐された第1増幅器4aからの高周波をインピーダンス整合する第1変成回路10aと、第1変成回路より細長の第2変成回路11aと、第2変成回路より細長の第3変成回路12aと、電力分配回路から分岐された第2増幅器4bからの高周波をインピーダンス整合する第4変成回路10bと、第4変成器より細長の第5変成回路11bと、第5変成器より細長の第6変成回路12bと、第3変成回路及び第6変成回路のそれぞれの出力側に接続された電力合成器とを設けて、第3変成回路及び第6変成回路を屈曲させると共に第1及び第2増幅器出力端から電力合成器6出力端までの伝送線路長を伝送周波数波長に略等しくするようにした。

(もっと読む)

帰還抵抗を有するフィールドプレートトランジスタ

実施形態は、これに限定されないが、ソース電極と、入力無線周波数(RF)信号を受信するゲート電極と、増幅されたRF信号を出力するドレイン電極と、を有する単位セルを含む装置とシステムを含む。フィールドプレートは前記ソース電極に連結され、帰還抵抗は前記フィールドプレートと前記ソース電極間に連結されてもよい。 (もっと読む)

半導体集積回路

【課題】 半導体集積回路の製造時に生じる抵抗素子のばらつきによる増幅器の負荷変動や温度変化による増幅特性に与える影響を軽減した半導体集積回路を提供する。

【解決手段】 増幅回路2と、半導体基板上に回路形成した抵抗素子を有するバンドギャップリファレンス電流源5からの電流を電圧変換して前記増幅回路2にバイアス電圧を供給するバイアス回路3と、バイアス回路3内に半導体接合で形成したモニタ抵抗素子5MRと、モニタ抵抗素子5MRを測定する半導体基板上に設けた測定端子6と、バンドギャップリファレンス電流源5の一部を構成し、回路電流を調整する抵抗値が異なる複数の調整抵抗素子71とを備え、モニタ抵抗素子5MRの抵抗値が所望値より低い場合は、所望値より高い調整抵抗素子を選択し、モニタ抵抗素子の抵抗値が所望値より高い場合は、所望値より低い調整抵抗素子を選択し、増幅回路2のバイアス電圧を調整する。

(もっと読む)

増幅回路及びこれを備える光ピックアップ

【課題】増幅回路の応答速度等を改善する。

【解決手段】増幅回路1は、差動増幅回路20と複数のソースフォロア回路30、複数の位相補償ブロック300、複数の帰還回路40を含む。差動増幅回路20は、入力信号と基準信号が入力されるNチャンネルMOSトランジスタ23、24を備え、スイッチ18−1−3、18−2−3により差動出力電流を取り出すべき接続点(P1、P2)を選択する。複数の帰還回路40は、スイッチ18−1−1、18−1−2により選択される。スイッチ18−1−1、18−2−1、18−1−2、18−2−2は互いに連動する。スイッチ18−1−1がオンのときには、帰還回路40−1、接続点P1、位相補償ブロック300−1、ソースフォロア回路30−1がまとめて選択される。

(もっと読む)

歪補償回路

【課題】コスト高を招くモノリシック化を行うことなく、高周波帯でも利得特性が単調に変化する歪補償回路を得ることを目的とする。

【解決手段】高周波信号hfsを2分配して、位相が180度異なる2つの分配信号ds1,ds2を出力する分配器1と、分配器1から出力された分配信号ds1,ds2を伝送する信号路5,8と、信号路5,8により伝送された分配信号ds1と分配信号ds2の位相を揃えて、その分配信号ds1と分配信号ds2を合成する合成器11とを設け、直流電源15から供給される直流電流がバイアス印加用抵抗16を介して順方向に印加されるダイオード18を信号路5,8の間に挿入する。

(もっと読む)

半導体装置

【課題】異なる系統の電力増幅回路を含む半導体装置を小型にする。

【解決手段】2つの周波数帯の高周波信号を取り扱うことが可能なデュアル方式のデジタル携帯電話機のRFパワーモジュールを構成する系統の異なる電力増幅回路2A,2Bを同一のICチップ1C内に配置した。この場合、電力増幅回路2A,2BをICチップ1Cの周辺に配置し、周辺回路3を電力増幅回路2A,2Bの間に配置させた。これにより、異なる系統の電力増幅回路2A,2Bを同一のICチップ1C内に設けて小型化が図れる上、異なる系統の電力増幅回路2A,2Bを同一のICチップ1Cに設けても電力増幅回路2A,2B間の距離が確保されるので電力増幅回路2A,2B間の結合を抑制させることができ、電力増幅回路2A,2B間でのクロストークを抑制できる。

(もっと読む)

半導体装置

【課題】マイクロ波帯及びミリ波帯において用いられる高出力且つ高利得な電力増幅器を得られるようにする。

【解決手段】マイクロストリップ線路109上には、入力整合回路102の中央部へ入力端子110から入力される高周波信号の高周波信号の伝送方向に沿って、スリット116及びスリット117が形成され、スリット117の長さより上記中央部の隣接位置のスリット116の長さが長く設定される。

(もっと読む)

増幅器及び無線機

【課題】回路面積を増大させずにインダクタンスを大きくすることができる増幅器及び無線機を提供すること。

【解決手段】増幅器が、基板と、前記基板上に配置され、入力信号を増幅して出力する第1〜第4の増幅部と、前記基板上に配線され、前記第1の増幅部の出力と前記第2の増幅部の出力、前記第2の増幅部の出力と前記第3の増幅部の出力、前記第3の増幅部の出力と前記第4の増幅部の出力、及び前記第4の増幅部の出力と前記第1の増幅部の出力とをそれぞれ接続し、少なくとも一つの蛇行部を備えた第1〜第4の誘導性線路と、前記第1〜第4の誘導性線路と磁界結合する第5の誘導性線路とを備える。

(もっと読む)

半導体装置

【課題】携帯電話機などの移動体通信機器に搭載される電力増幅器をバランスアンプから構成する場合に、バランスアンプの特性向上を図ることができる技術を提供する。

【解決手段】実施の形態の特徴の1つは、ローバンド信号用ネガティブパスに配置される受動部品と、ローバンド信号用ポジティブパスに配置される受動部品とを半導体チップCHPの中心線CL1に対して対称となる位置に配置することにある。これにより、ローバンド信号用ネガティブパスと、ローバンド信号用ポジティブパスとの対称性が高められる。この結果、ローバンド信号用ネガティブパスと、ローバンド信号用ポジティブパスとの経路差による整合ロスを充分低減することができ、ローバンド信号用バランスアンプの特性を向上することができる。

(もっと読む)

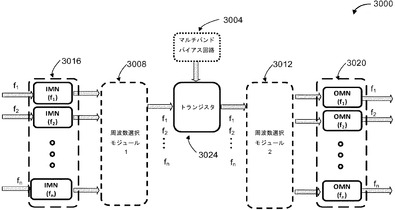

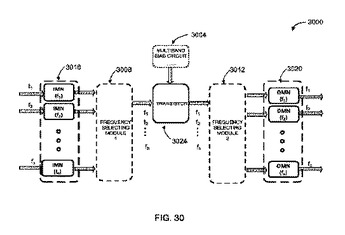

メタマテリアル電力増幅器システム

電力増幅システムならびにそのモジュールおよび構成要素が、CRLH構造に基づいて設計され、高効率および高線形性が提供される。

(もっと読む)

(もっと読む)

電力増幅器

【課題】差動信号の増幅および合成を行ない、かつ高調波を抑制することが可能な電力増幅器を提供する。

【解決手段】電力増幅器101は、差動信号である第1の入力信号および第2の入力信号を増幅する第1の増幅器11,12と、第1の増幅器11,12によって増幅された第1の入力信号および第2の入力信号を受ける第1のコイル21と、第1のコイル21と磁気的に結合され、増幅された第1の入力信号および第2の入力信号の合成信号が出力される第2のコイル22と、第2のコイル22と磁気的に結合された第3のコイル23と、第3のコイル23の両端間に接続された第1のキャパシタ41とを備え、第1のキャパシタ41の一端が接地ノードに接続されている。

(もっと読む)

無線アプリケーション用高出力半導体素子および高出力半導体素子の製造方法

無線アプリケーション用の5Wを超える電力で動作する高出力半導体素子(400)は、高出力半導体素子の活性領域(404)を含む半導体基板(402)と、高出力半導体素子の活性領域にコンタクトを提供する、半導体基板上に形成された接触領域(408)と、半導体基板の一部を覆うように形成された誘電体層(412)と、高出力半導体素子に外部接続部を提供するリード線(500、502)と、高出力半導体素子の活性領域とリード線との間の半導体基板上に形成されたインピーダンス整合回路網(510、512)であって、インピーダンス整合回路網は、誘電体層上に形成された複数の導体線(414)であって、活性領域の接触領域に高出力接続部を提供する、接触領域に結合された複数の導体線を含み、該複数の導体線はインピーダンス整合のための所定のインダクタンスを有する、インピーダンス整合回路網とを備える。  (もっと読む)

(もっと読む)

RF電力増幅装置

【課題】負荷変動によってVSWR(電圧定在波比)の値が極端に大きくなった場合でも、出力電力結合器の電子部品の溶断の危険性を軽減すること。

【解決手段】RF電力増幅装置HPA_MDは、第1と第2のRF電力増幅回路PA1、PA2、ウィルキンソン・パワー・コンバイナによって構成された出力電力結合器Out_PCを具備する。出力電力結合器Out_PCの第1と第2の入力端子にRF電力増幅回路PA1、PA2のRF増幅出力信号が供給されて、出力端子OutからRF増幅出力信号が生成される。出力電力結合器Out_PCで、第1入力端子と出力端子の間のインピーダンスと、第2入力端子と出力端子の間のインピーダンスとは略等しく設定され、第1入力端子と第2入力端子の間の抵抗R61は、例えば渦電流を生成するインダクタ等のリアクタンス素子L63によって置換されている。

(もっと読む)

集積回路装置、電気光学装置及び電子機器

【課題】駆動対象を高速かつ安定に駆動でき、さらに静電耐量の高い集積回路装置、電気光学装置及び電子機器等を提供すること。

【解決手段】集積回路装置は出力端子20に接続される駆動対象を駆動する駆動回路10と、駆動回路10の第1の出力ノードN1と出力端子20との間に設けられる第1の静電保護用抵抗素子30と、駆動回路10の第2の出力ノードN2と出力端子20との間に設けられ、その抵抗値が第1の静電保護用抵抗素子30より大きい第2の静電保護用抵抗素子31とを含み、駆動回路10は、駆動期間の前半期間では第1及び第2の静電保護用抵抗素子30、31を介して駆動対象を駆動し、駆動期間の後半期間では、第1の静電保護用抵抗素子30を介すことなく第2の静電保護用抵抗素子31を介して駆動対象を駆動する。

(もっと読む)

半導体装置

【課題】抵抗素子の抵抗値の基板電圧依存性をなくす。

【解決手段】基板領域(25A,25B)上に互いに直列に接続される抵抗素子(R1、R2)において、抵抗素子の基板領域と対応の抵抗素子の間の平均電位が逆極性でかつ大きさが等しくなるように、抵抗素子端部と対応の基板領域とをバイアス配線(27A,27B)で接続する。

(もっと読む)

利得調整回路およびD級電力増幅器

【課題】利得調整および広範囲な電圧源にも安定して適用することができる利得調整回路およびD級電力増幅回路を提供する。

【課題を解決するための手段】

利得調整回路100はアナログ入力信号が入力される信号入力端子102、アナログ信号を増幅し電圧源E1が供給される演算増幅器108、演算増幅器108の反転入力端子108aと出力端子108cとの間に接続される第1のT型抵抗回路T123を備える。信号入力端子102と反転入力端子108aとの間に利得調整するための第1の可変抵抗RV1を接続する。演算増幅器108の非反転入力端子108bにはバイアス電圧供給回路130から直流バイアス電圧が供給される。バイアス電圧供給回路130は第1の電圧生成回路132および第2のバイアス電圧生成回路138を備える。第1のバイアス電圧生成回路132は第2の電圧源E2および第2のT型抵抗回路T123aを備え、第2のバイアス電圧生成回路138は第3の電圧源E3および第2の可変抵抗RV2を備える。

(もっと読む)

安定化回路および安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路および安定化回路を備える半導体装置を提供する。

【解決手段】高周波負性抵抗発振に伴う負性抵抗を有する能動素子140の主電極に接続される抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とを備え、能動素子の負性抵抗をキャンセルすることを特徴とする安定化回路および安定化回路を備える半導体装置。

(もっと読む)

61 - 80 / 202

[ Back to top ]