Fターム[5J500AQ03]の内容

Fターム[5J500AQ03]に分類される特許

21 - 40 / 202

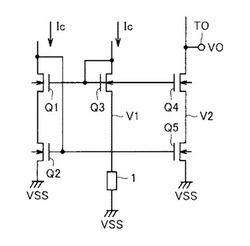

カレントミラー回路およびそれを用いた半導体装置

【課題】プロセス変動があった場合でも広い出力電圧範囲が得られるカレントミラー回路を提供する。

【解決手段】この低電圧カスコードカレントミラー回路は、NチャネルMOSトランジスタQ1〜Q5と抵抗素子1を備える。トランジスタQ3のオーバードライブ電圧Vov_Q3は、トランジスタQ4,Q5のオーバードライブ電圧Vov_Q4,Vov_Q5の和に等しい。定電流Icと抵抗素子1の抵抗値R1との積は、トランジスタQ5の飽和マージンVdsm_Q5となる。したがって、プロセス変動があった場合でも、トランジスタQ5の飽和マージンVdsm_Q5は変化しない。

(もっと読む)

高周波半導体モジュール

【課題】段間の整合状態を観測して整合回路の調整を行うことのできる高周波半導体モジュールを提供する。

【解決手段】複数の半導体増幅素子7、8を直列に接続して増幅を行う多段型の高周波半導体モジュールであって、パッケージ3内に配置される回路基板4、5,6に、半導体増幅素子7、8間の段間における高周波信号をモニタするためのモニタ回路を具備する。

(もっと読む)

集積フィルタを備えた増幅器

【課題】良好な雑音性能を有しかつ大きい干渉信号に対処できる増幅器を提供する。

【解決手段】集積フィルタを備えた増幅器320b(例えば,LNA)は利得ステージ330、フィルタ・ステージ340およびバッファ・ステージ350を含んでいてもよい。利得ステージは、入力信号に対して信号増幅を提供する。フィルタ・ステージは、入力信号に対してフィルタリングを提供する。バッファ・ステージは、フィルタ・ステージからのフィルタされた信号をバッファする。増幅器は、第2のフィルタ・ステージ360及び第2のバッファ・ステージ370をさらに含んでいてもよい。

(もっと読む)

整合回路及びこれを備えた電力増幅回路

【課題】小型化を図ることができる整合回路を提供する。

【解決手段】半導体装置1のインピーダンス整合を取るための整合回路であって、半導体装置1上に設けられた第1のボンディングパッド1A及び第2のボンディングパッド1Bと、半導体装置1の外部に設けられた外部電極1と、第1のボンディングパッド1Aと外部電極2とを接続する第1のワイヤ4Aと、第2のボンディングパッド1Bと外部電極2とを接続する第2のワイヤ4Bとによって形成されるインダクタを少なくとも1つ備える整合回路。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力整合回路と、高周波半導体チップの出力側に配置された出力整合回路と、入力整合回路に接続された高周波入力端子と、出力整合回路に接続された高周波出力端子と、高周波半導体チップに接続される平滑化キャパシタ用端子とを備え、高周波半導体チップと、入力整合回路と、出力整合回路とが1つのパッケージに収納された半導体装置。

(もっと読む)

電力増幅器用バイアス回路

【課題】差分周波数Δfが数百MHzにおいても電力増幅器用バイアス回路のリップル電圧ΔVが抑制されてバイアス回路電圧が平滑化され、マイクロ波/ミリ波/サブミリ波帯の高周波に適用可能な電力増幅器用バイアス回路を提供する。

【解決手段】電力増幅器の出力側整合伝送線路のバイアス回路接続点に接続された第1ボンディングワイヤと、第1ボンディングワイヤの終端に接続された第2ボンディングワイヤと、第1ボンディングワイヤの終端に接続されたオープンスタブ伝送線路と、第2ボンディングワイヤの終端に接続されたバイパスリザバーキャパシタとを備える電力増幅器用バイアス回路。

(もっと読む)

バイアス回路

【課題】受信雑音性能の低下をともなうことなく簡易な構成により受信用トランジスタを過入力による破壊から防ぐことのできるバイアス回路を得る。

【解決手段】過入力保護回路を有さない受信用増幅器に用いられるバイアス回路であって、受信用増幅器を構成する受信用トランジスタ2のゲート端子に接続されたゲートバイアス回路8と、受信用トランジスタ2のドレイン端子に接続されたドレインバイアス回路9とを備える。ゲートバイアス回路8は、過入力時における受信用トランジスタ2のゲート電流Igまたはゲート電圧Vgの変化を検知して変化信号を生成する変化検知手段を有する。ドレインバイアス回路9は、過入力時の変化信号に応答して、受信用トランジスタ2に対するドレイン電圧Vdを低減させる。

(もっと読む)

バンドギャップ型基準電圧発生回路

【課題】バンドギャップ型基準電圧発生回路において、高温における寄生ダイオードのリーク電流の影響を制御して、基準電圧の温度特性の向上を図る。

【解決手段】NPN型BIPトランジスタQ1の寄生ダイオードD1とは別に、i個(iは1以上の自然数)の温度特性制御ダイオードD31〜D3iをNPN型BIPトランジスタQ1のコレクタに接続する。温度特性制御ダイオードD31〜D3iは、Pチャネル型MOSトランジスタM1,M2からなるカレントミラー回路を介して、寄生ダイオードD21〜D2Kのリーク電流の増加による基準電圧Vrefへの影響をキャンセルするように作用する。

(もっと読む)

高周波回路

【課題】最小ループと2セルループのオッドモード発振を共に抑制する高周波回路を提供する。

【解決手段】半導体基板上に並列に配列された複数のトランジスタと、第1の絶縁基板上に配置され、複数のトランジスタのゲート端子電極にそれぞれ接続された複数の入力整合回路と、第1の絶縁基板上に配置され、入力整合回路に隣接して配置された入力側第4発振抑制抵抗と、入力側第4発振抑制抵抗に直列接続された入力側第1キャパシタと、隣接する入力整合回路間を繋ぐ伝送線路上の点と入力側第1キャパシタ間に接続された入力側第1インダクタとを有する入力側発振抑制回路とを備え、入力側第1インダクタのインダクタンス値をL1、入力側第1キャパシタのキャパシタンス値をC1とすると、1/{2π(L1×C1)1/2}で表される入力側第1インダクタと入力側第1キャパシタの共振周波数が、2セルループの発振周波数fosc2に等しい高周波回路。

(もっと読む)

電力増幅器

【課題】複数のトランジスタを均一に動作させ、低消費電力及び良好な歪特性を実現する。

【解決手段】高周波信号を増幅する電力増幅器100であって、上部電極120a及び下部電極120bを有し、高周波信号が入力される整合容量120と、整合容量120の下部電極120bから出力される高周波信号を増幅する複数のトランジスタ110が所定の方向に並んで配置されているトランジスタ列とを備え、トランジスタ列に隣り合う領域において、トランジスタ列の両端から略等しい距離には、接地されたビアホール170が形成され、下部電極120bは、ビアホール170を挟んで高周波信号が均等に分配されるように配置されたマイクロストリップ線路であり、複数のトランジスタ110のベース端子に接続される。

(もっと読む)

半導体装置

【課題】電流検出精度が低下することを抑制することができる半導体装置を提供する。

【解決手段】メインTr2のゲート電極およびセンスTrのゲート電極をゲート電圧を印加する共通のゲート端子と接続する。そして、センスTr3にはゲート端子からそのままゲート電位が印加されると共に、メインTr2にはセンスTr3に印加されるゲート電位が第1、第2抵抗31、32によって抵抗分割された電位が印加され、メインTr2のゲート−ソース間電圧と、センスTr3のゲート−ソース間電圧とが等しくなるようにする。

(もっと読む)

寄生振動を低減したトランジスタ増幅器

【課題】寄生振動、すなわちパラメータ発振を低減したトランジスタ増幅器を提供する。

【解決手段】複数のトランジスタセル15”を有するトランジスタデバイス12”は複数のフィルタ18”が設けられる。フィルタのそれぞれ1つは、入力ノード20”と、複数のトランジスタセルの制御電極17のうちの対応する1つとの間に結合されている。半導体によって、複数のトランジスタセルの共通活性領域が提供される。フィルタのそれぞれ1つは、導電層と、導電層上に配置された誘電層と、誘電層の上に配置された抵抗層と、抵抗層の第1の部分に電気的に接触するように配置され入力ノードを提供する導電電極と、抵抗層の第1の部分から離れた抵抗層の第2の部分と電気的に接触するコネクタであって、誘電体を通り第1の導体と電気的に接触するコネクタとを含む。

(もっと読む)

電力増幅器

【課題】チップ面積やコストを増加させることなく、リーク電流を抑制することができる電力増幅器を得る。

【解決手段】バイアス回路B1,B2は、リファレンス電圧発生回路VGから供給されたリファレンス電圧に基づいてバイアス電圧を生成し、増幅トランジスタA1,A2にバイアス電圧を供給する。インバータINVは、イネーブル電圧を昇圧して出力する。リファレンス電圧発生回路VGは、インバータINVの出力電圧に応じてON又はOFFする。インバータINVは、イネーブル端子Venと、電源端子Vcbと、トランジスタTri1と、FET抵抗Fdi2とを有する。トランジスタTri1のベースはイネーブル端子Venに接続され、コレクタは電源端子Vcbに接続され、エミッタは接地されている。FET抵抗Fdi2はトランジスタTri1のコレクタと電源端子Vcbとの間に接続され、FET抵抗Fdi2のゲート電極はオープンである。

(もっと読む)

ドハティ増幅器

【課題】耐湿性を向上させることができるドハティ増幅器を提供することを目的とする。

【解決手段】本発明のドハティ増幅器は、入力信号を2つの信号に分配する分配器と、2つの信号のうち一方が入力し、第1チップに形成される第1FET11からなるキャリアアンプ10と、2つの信号のうち他方が入力し、第1チップと異なる第2チップ200に形成される第2FET13からなるピークアンプ12と、第2チップ200に形成され、第2FET13を加熱する第3FET32と、キャリアアンプ10の出力インピーダンスを変換し、キャリアアンプ10の出力信号と合成する合成器20と、を有することを特徴とする。

(もっと読む)

高周波半導体増幅装置

【課題】発振対策を容易に講ずることができる高周波半導体増幅装置を提供すること。

【解決手段】パッケージ14内部に、半導体増幅素子11、入力整合回路基板17の表面上に形成された入力整合回路パターン15、および出力整合回路基板24の表面上に形成された出力整合回路パターン23を、パッケージ14内部に有する高周波半導体装置であって、出力整合回路基板24の表面上には、出力整合回路基板24の表面上に、出力整合回路パターン23に接続するように形成された出力信号ライン25に対して、容易に電気的に接続・切断可能な減衰器29が形成されている。

(もっと読む)

電力増幅器

【課題】入力の整合回路での損失の低減、並びに、回路の簡略化及び小型化が可能な電力増幅器を提供する。

【解決手段】電力増幅器100であって、第1金属配線である環状1次コイル121と、複数の第2金属配線である複数の直線2次コイル122とを有し、入力インピーダンスの整合をとるとともに、入力信号を複数の分配信号に分配する入力側トランスフォーマ120と、複数の分配信号の1つを増幅する1対のトランジスタ111をそれぞれが備える複数のプッシュプル増幅器110と、第3金属配線である環状2次コイル131と、複数の第4金属配線である複数の直線1次コイル132とを有し、増幅された複数の分配信号を合成するとともに、出力インピーダンスの整合をとる出力側トランスフォーマ130とを備え、1対のトランジスタ111の2つの入力端子は、第2金属配線を介して互いに接続され、2つの出力端子は、第4金属配線を介して互いに接続される。

(もっと読む)

高周波モジュールおよびその動作方法

【課題】高温通電時にはバイアスジャンプを回避し、実運用時には外部電源を製品によらず共通化し、かつ端子数を削減する。

【解決手段】半導体装置24と、入力整合回路17と、出力整合回路18と、運用時用ゲートバイアス回路70と、運用時用ゲートバイアス回路70に接続された運用時用ゲートバイアス端子41aと、入力整合回路17に接続された高周波入力端子兼高温動作時用ゲートバイアス端子21aと、出力整合回路18に接続されたドレインバイアス回路80と、ドレインバイアス回路80に接続されたドレインバイアス端子41bと、出力整合回路18に接続された高周波出力端子21bとを備え、1つのパッケージに収納された高周波モジュール1およびその動作方法。

(もっと読む)

変圧器電力合成器

【課題】複数の入力ポートと少なくとも1つの出力ポートとを備え、高い変圧器結合効率及び高い電力合成効率を達成するオンチップ変圧器電力合成器を提供する。

【解決手段】変圧器電力合成器は、複数の一次巻線導体と複数の二次巻線導体とを含む。一次巻線導体は、入力ポートにそれぞれ電気的に接続される。加えて、各一次巻線導体は対応する入力ポートのプラス端子とマイナス端子との間に電気的に接続されている。二次巻線導体は、一次巻線導体にそれぞれ磁気的に結合される。二次巻線導体は、出力ポートのプラス端子とマイナス端子との間に直列接続及び並列接続を含むトポロジー構造を持つように構成される。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

電力増幅装置

【課題】高出力と専有面積の縮小とを両立させた電力増幅装置を提供する。

【解決手段】基板上に形成された電力増幅装置300であって、全体で環状の一次インダクタ1,2と、グランドパターン4〜8と、トランジスタ対(Q1p,Q1n)および(Q2p,Q2n)と、二次インダクタ3とを備える。グランドパターン4〜8は、基板に垂直な方向から見て、環状の一次インダクタ1,2の内側の領域の一部から外側の領域に及ぶように設けられ、外側の領域の複数箇所で接地される。各一次インダクタ1,2の両端には、対応のトランジスタ対を構成する第1および第2のトランジスタの第1の主電極がそれぞれ接続される。第1および第2のトランジスタの各第2の主電極は、一次インダクタの内側の領域でグランドパターンに接続されるとともに、上記の接地された複数箇所のいずれとも電気的に導通する。

(もっと読む)

21 - 40 / 202

[ Back to top ]