Fターム[5K029EE06]の内容

直流方式デジタル伝送 (8,390) | 通信方式 (506) | ビット同期伝送 (163) | 同期信号を伝送するもの (102)

Fターム[5K029EE06]の下位に属するFターム

調歩同期伝送(スタートストップ方式) (38)

受信側から同期信号を送るもの (8)

Fターム[5K029EE06]に分類される特許

1 - 20 / 56

符号化装置及び符号化方法

【課題】データ値の変化頻度の低下を防止し、且つコマンドコードの設定を柔軟に行うことができる符号化装置を提供する。

【解決手段】4B5Bエンコーダ3は、入力される4ビットデータを、データ値「0」が、冒頭側,末尾側にそれぞれ1ビットまで、且つ全体では連続して2ビットまでとなる5ビットのデータパターンに変換し、5Nビットコマンドエンコーダ4は、5Nビットのビット列中において、データ値「0」が連続して2ビットまでとなるコマンドパターンに変換する。そして、変換されたデータ及びコマンドを、NRZIエンコーダ7によりNRZI符号に変換する

(もっと読む)

トランシーバ

【課題】サンプリングに使用するクロックとは非同期に送信データが供給されるトランシーバにおいて、送信データの信号レベルを正しくサンプリングできるようにする。

【解決手段】送信データTXDのスタートビットの開始エッジのタイミング(開始タイミング)が検出されると、バスクロックBCKに同期し、そのバスクロックBCKの1周期当たり4個のサンプリング用エッジを有するサンプリングSCKを用い、開始タイミングを起点として2個目のサンプリング用エッジのタイミングで送信データTXDをサンプリングし、以後、4個目のサンプリング用エッジのタイミング毎に、送信データTXDをサンプリング(ラッチ)する。そのサンプリングしたデータを、更に、バスクロックBCKの立ち下がりエッジでサンプリングすることによって、バスクロックBCKに同期した同期送信データdTXDを生成する。

(もっと読む)

データ転送システムおよびデータ転送方法

【課題】システム性能を低下させることなくマスタから周辺回路へデータを転送することが可能なデータ転送システムを提供することである。

【解決手段】本発明にかかるデータ転送システムは、マスタM1〜M3と、マスタから第1のバス2を介して出力された複数のデータD1〜D3を入力し第2のバス4を介して当該データを出力するバスブリッジ3と、バスブリッジ3から出力されたデータD1〜D3を保持するライトバッファWB1〜WB3および当該ライトバッファWB1〜WB3から出力されたデータD1〜D3を保持するレジスタR1〜R3を備える周辺回路5と、を備える。バスブリッジ3およびライトバッファは第1のクロックで動作し、レジスタは第1のクロックとは非同期の第2のクロックで動作し、ライトバッファとレジスタとを同期化することでライトバッファからレジスタへデータを転送する。

(もっと読む)

伝送装置、伝送方法、画像形成装置、送信装置及び受信装置

【課題】併走クロックを使用する信号伝送において、併走クロックの周波数を落とすことなく、信号の長距離伝送を行うことを可能とする。

【解決手段】送信側の通信装置1と受信側の通信装置4との間で、クロック信号と併走してデータ信号の伝送を行う伝送装置である。送信側の通信装置1は、1クロック周期の中に複数ビットのデータを入れ込み、その際、前記複数ビットの内少なくとも連続する2ビットを同一データとして持つ複数のデータ群として前記受信側の通信装置4送信する。受信側の通信装置は、受信したデータの少なくとも連続する2ビットの同一データを持つデータ群の内、2ビット目以降の何れか1ビットのデータを有効なデータとして受信する。

(もっと読む)

パラレルデータ出力制御回路及び半導体装置

【課題】常に信頼性の高いパラレルデータ出力制御が行えるをパラレルデータ出力制御回路を得る。

【解決手段】CPU12はバッファ13からのリクエストRQに応答して内蔵RAM11よりデジタルデータをバッファ13に出力する。バッファ13は複数段構成のFIFOを有し、FIFOの各段は1単位(10ビット)のデジタルデータを格納可能であり、バッファ13全体としてFIFOの構成段数単位分のデジタルデータを格納することができる。レジスタ14は出力制御クロックCK15に同期して、バッファ13内部に格納したデジタルデータを1単位ごとに取り込む。レジスタ14に格納されたデジタルデータがD/A変換用データDataとしてパラレルDAC2に出力される。WR信号出力タイマ17は出力制御クロックCK15に同期して“L”の1ショットパルスを有する書き込み制御信号WRを生成する。

(もっと読む)

電子機器、電子機器の制御方法、送信装置および受信装置

【課題】HDMI等のデジタルインタフェースにおいて大容量のデータ通信を可能にする。

【解決手段】DDCラインを構成する2本の信号ライン、つまりSDAラインおよびSCLラインを、I2C通信ラインとして用いる他に、高速データ通信ラインとしても用いる。この2本の信号ラインをI2C通信ラインとして用いる場合、ソース機器110、シンク機器120は、I2C通信部を2本の信号ラインに接続した状態となり、I2Cの双方向通信を行う。一方、この2本の信号ラインを高速データ通信ラインとして用いる場合、ソース機器110、シンク機器120は、差動高速ドライバ/レシーバを2本の信号ラインに接続した状態となり、双方向差動通信を行う。双方向差動通信を行う場合、時分割双方向通信を行うことで、全体としての伝送速度は片方向の2倍強必要とされるが、エコーキャンセラを用いた双方向構造よりも安価に実現できる可能性がある。

(もっと読む)

既存のネットワークケーブルを使用してネットワークを同期させるための方法およびシステム

【課題】既存のケーブルを使用してネットワークを同期させる。

【解決手段】ローカルエリアネットワーク102の第1のエンドシステム104のマスタ物理インタフェースデバイス131のメッセージ送信機134およびメッセージ受信機138に通信で結合された同期用送信機112と、ローカルエリアネットワークの第2のエンドシステム10)のスレーブデバイス132のメッセージ送信機136およびメッセージ受信機140に通信で結合された同期用受信機118とを含み、同期用送信機は、第1の差動ツイストペア接続108および第2の差動ツイストペア接続110を使用して、同期用受信機にタイミングメッセージを送信するように構成され、同期用送信機は、第1の差動ツイストペア接続および第2の差動ツイストペア接続を使用して、同期用受信機に同期用パルスを送信する。

(もっと読む)

半導体デバイス、画像処理装置

【課題】複数のデータ伝送路のタイミングを低コストで同期可能な半導体デバイスを提供すること。

【解決手段】送信側から受信側にデータをシリアル送信する半導体デバイス100であって、データ転送の合間に、同期判定用のコードを送信する同期判定コード送信手段301,302と、送信側と受信側に共通のクロック信号を提供するクロック信号提供手段103と、クロック信号に同期して同じデータを送信する複数の伝送路117と、受信側に提供されたクロック信号の位相を、それぞれ異なる所定量遅延させ複数の遅延クロック信号を生成するクロック生成手段110と、遅延クロック信号に同期して伝送路を介して送信されたデータを取り込む複数の受信バッファ111と、コードを予め定められた規則に基づき検証して複数の受信バッファから1つの受信バッファを、複数の遅延クロック信号から1つの遅延クロック信号をそれぞれ選択する選択手段113、115と、を有する。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

通信システム、トランシーバ、ノード

【課題】スリープモードにあるノードを個別にウェイクアップすることが可能な通信システムにおいて、スリープモードにあるノードの消費電力を増大させることなく、自ノードに対する起動用フレームを識別できるようにする。

【解決手段】起動フレーム検出部17は、レシーバ16のコンパレータCP2を介して通信路LNを監視し、フレームの先頭(開始タイミング)からドミナントが3ビット連続する箇所(境界ポイント)までの領域(起動パタン領域)に設定されたビットパタンから抽出した特徴量(第1領域および第2領域の数)が、予め設定された起動量と一致するものを起動フレームとして認識し(WA←アクティブレベル)、その起動フレームの指定パタン領域に設定されている指定パタンをデューティ信号とみなしてデコードした値が、自ECU10に割り当てられた割当パタンと一致する場合に通常モードに遷移する(WU←アクティブレベル)。

(もっと読む)

データ伝送システムにおける通信装置および通信方法

【課題】同一符号が連続しても、構成および機能を複雑化することなく、確実にクロック復元が可能となる信頼性の高いデータ伝送システムにおける通信装置および通信方法を提供する。

【解決手段】送信すべきディジタルデータから所定ビット数(Nmax)連続する同一符号を検出したときにビット反転指示信号を出力する連続同一符号検出部11と、ビット反転指示信号に対応するディジタルデータの少なくとも1ビットの値を反転させたデータを生成するデータ反転部12と、反転ビットを含むデータを送信する送信部13と、を有し、所定ビット数(Nmax)がデータ伝送システムにおける同一符号連続規定値(NCR)以下に設定される。

(もっと読む)

シリアルコントローラ及び双方向シリアルコントローラ

【課題】シリアルコントローラを提供する。

【解決手段】本シリアルコントローラは外部クロックと入力データとを受信し、反転クロックと出力データとを出力するよう適合し、インバータと、シリアル位置検出器と、同期クロック生成器と、シリアルレジスタと、半サイクル遅延ユニットとを備える。このシリアルコントローラにより、クロック列が反転された場合、データ信号と駆動クロックが同期しないという問題を回避できる。また、双方向シリアルコントローラは識別ユニットと、データ方向付けユニットとを更に備え、このシリアルコントローラは、エラー検出のための参照データとするために現在の状態を中央制御ユニットに送ることが出来る。

(もっと読む)

同期信号検出装置

【課題】回路規模を小さくできるようにした同期信号検出装置を提供する。

【解決手段】同期信号仮検出部7が、2値のハイレベルとロウレベルとを順に繰り返して受信する前に1ビット長の2のN乗倍の長さで2値のロウレベルが続いたことを条件として受信した2値のレベルを仮同期信号として検出しているため、ロウレベルが1ビット長の2のN乗倍の長さ未満のときには全て仮同期信号として見なされることがなくなり、同期信号を検出するための煩雑な計算処理を行う頻度を少なくできる。

(もっと読む)

リンギング抑制回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できるリンギング抑制回路を提供する。

【解決手段】電源と信号線12Pとの間に接続されるNチャネルMOSFET19と、信号線12Mとグランドとの間に接続されるPチャネルMOSFET20とを備え、リンギング抑制回路18は、信号線12P,12Mの電位と、それぞれに対応するNチャネルMOSFET19,PチャネルMOSFET20のゲートに付与される電位との差に応じてNチャネルMOSFET19及びPチャネルMOSFET20をオンさせて、信号線12P,12Mに発生しようとするリンギングの抑制を図る。

(もっと読む)

信号制御装置および信号制御方法

【課題】異なるトリガー点における電圧のオフセットの発生を抑止でき、回路のバラツキの影響を防止でき、精度の向上を図れる信号制御装置および信号制御方法を提供する。

【解決手段】入力信号のトリガー点が異なる複数の電圧と可変のバイアス信号とを順次間欠的に比較する比較部12と、比較部12の比較結果に応じてバイアス信号、並びに、入力信号を制御するための入力信号制御信号を生成する機能を有する制御部16と、を有し、制御部16は、バイアス電圧がトリガー点の異なる複数の電圧より小さいときはバイアス電圧の値を大きくするように制御し、バイアス電圧がトリガー点の異なる複数の電圧より大きいときはバイアス電圧の値を小さくするように制御し、バイアス電圧がトリガー点の異なる複数の電圧の間にあるときは、前のトリガー点の電圧が後のトリガー点の電圧に近づくように入力信号制御信号を生成する。

(もっと読む)

高圧インバータのセル通信制御装置およびセル通信制御方法

【課題】インバータを有するセルを複数備えた高圧インバータのセル通信制御装置において、MCUと各セル間の通信に必要とする光配線の本数を減らす。

【解決手段】 MCUの通信制御部50に、シリアル信号の送信開始タイミングから、入力ゲート指令信号の状態が変化するまでの時間を遅延時間として検出するゲート状態変化ラッチ回路55およびゲート遅延検出カウンタ56を設け、前記検出時における送信シリアル信号の、設定されたフレーム送信期間後に送信するシリアル信号の送信開始タイミングを、前記遅延時間分遅らせて更新するシリアル信号更新遅延減算カウンタ57およびシリアル信号更新開始信号出力回路58を設け、前記更新されたシリアル信号を、1本の光配線110を介して前記セルに送信するシリアル信号送信処理回路59を設け、前記セルに、前記送信されたシリアル信号から前記ゲート指令信号を再生する信号再生部100を設ける。

(もっと読む)

通信集中制御システムおよび通信集中制御方法

【課題】バスの配線数の増大を抑止しつつ、緊急を要する事態には即応的に割り込み要求を伝送することが可能な通信集中制御システムおよび通信集中制御方法を提供する。

【解決手段】マスタ装置20および複数のスレーブ装置30はフレーム同期信号に同期して双方向通信可能で、通信バス40は、データレベルを含む複数の信号レベルが設定される多値信号が伝送され、多値信号はデータレベルに加えて、ひとつの信号レベルがフレームクロックに割り当てられ、他のひとつの信号レベルが割り込みの衝突に割り当てられ、マスタ装置20は、フレームクロックとアドレス信号を通信バスに送信し、アクノレッジ信号と割り込み信号IRを通信バスから受信し、データを通信バスに対して送受信し、各スレーブ装置30はフレームクロックとアドレス信号を通信バス40から受信し、アクノレッジ信号と割り込み信号を通信バスに送信し、データをバスに対して送受信する。

(もっと読む)

信号伝送システム

【課題】安定した映像信号を送信及び再生することができる信号伝送システムを提供する。

【解決手段】信号伝送システムは、水平同期信号を差動信号に変換し、第1コンソール信号をコモンモード信号に変換し、当該差動信号及び当該コモンモード信号を1対の信号線を介して受信装置に送信する差動ドライバ34、及び受信装置からコモンモード信号に変換された第2コンソール信号を受信するコンソール信号受信回路35を有する送信装置1と、送信装置1から差動信号及びコモンモード信号を上記1対の信号線を介して受信し、当該差動信号を水平同期信号に復元する差動レシーバ54、受信されたコモンモード信号を第1コンソール信号に復元するコンソール信号受信回路56、及び第2コンソール信号をコモンモード信号に変換し、上記1対の信号線を介して送信装置1に送信する差動ドライバ34を有する受信装置2を含む。

(もっと読む)

試験測定機器及び方法

【課題】試験測定機器でビット・エラーを検出する。

【解決手段】入力手段12が入力信号を受けてデジタル化データ14を出力する。メモリ18が基準シーケンスを含むデジタル化基準データを蓄積する。パターン検出器16がデジタル化データ14から基準シーケンスを検出し、それに応じて同期信号20を発生する。メモリ制御器19の制御により、メモリ18が同期信号に応答してデジタル化基準データ22を出力する。比較器24がメモリからのデジタル化基準データ22をデジタル化データ14と比較する。

(もっと読む)

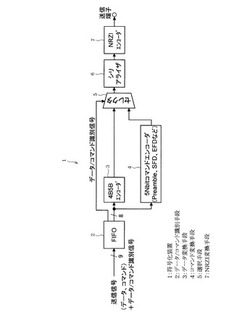

シリアル通信システム及びシリアル通信方法

【課題】MDライン及びSDラインの両方を同時にデータ送信に使用することができるシリアル通信システムを提供する。

【解決手段】本発明のシリアル通信システム1は、第1のデバイス2と第2のデバイス3とを有し、第1のデバイス2と第2のデバイス3とは、第2のデバイス3が生成したシリアルクロックに基づいて、相互通信を開始するシリアル通信システムである。第1のデバイス2から第2のデバイス3への出力が、前フェーズにおいて受信したデータの最終ビット値と反転していると、第2のデバイス3は第1のデバイス2の通信準備状態が完了状態であると判断し、相互通信を開始する。

(もっと読む)

1 - 20 / 56

[ Back to top ]