Fターム[5K029HH05]の内容

直流方式デジタル伝送 (8,390) | 受信部 (1,135) | 等化 (135)

Fターム[5K029HH05]の下位に属するFターム

量子化帰還 (4)

Fターム[5K029HH05]に分類される特許

121 - 131 / 131

エルミート最適化法を用いて通信用受信機のイコライザのフィルタ係数を計算する方法

通信用受信機のイコライザのフィルタ係数を計算する方法であって:チャネル推定入力からチャネル応答行列GとHを計算するステップ(22)と;チャネル応答行列Gの低次三角行列Lと高次三角行列Uへのコレスキー分解を実行するステップ(24)と;低次三角行列Lに対して前方置換を実行することにより列ベクトルdを計算するステップ(26)と;低次三角行列Lの列ベクトルdとエルミート転置行列LHに対して後方置換を実行することによりチャネル応答行列Gの逆行列G-1の中央列c0を計算するステップ(28)と;チャネル応答行列Gの逆行列G-1の中央列c0とチャネル応答行列Hのエルミート転置行列HHとからフィルタ係数を計算するステップ(30)と;からなる方法。  (もっと読む)

(もっと読む)

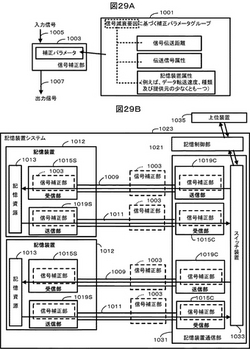

記憶装置システム及び記憶装置システム内での信号伝送方法

【課題】 複数台の記憶装置の伝送に関する信号品質の劣化を防ぐ。

【解決手段】 記憶装置システムは、搭載された複数の記憶装置にそれぞれ接続される複数の信号伝送線路と、複数の信号伝送線路を介して複数の記憶装置との間でそれぞれ信号の送受を行う複数のシステム側通信部と、複数の記憶装置と複数のシステム側通信部との間でやり取りされる信号を入力し、入力された信号を、予め設定された補正パラメータに基づいて補正し、補正後の信号を出力する1又は複数の信号補正部とを備える。補正パラメータは、記憶装置とシステム側通信部との間の信号伝送線路の長さと、信号補正部に入力される信号の波長属性と、記憶装置に関する記憶装置属性とのうちの少なくとも一つに基づいて設定された値である。

(もっと読む)

ロングおよびショート・トレースバック・トレリス復号器(LONGANDSHORTTRACEBACKTRELLISDECODERS)による判定を使用した判定帰還型等化器(DECISIONFEEDBACKEQUALIZER)

判定帰還型等化器は、第1の符号判定が比較的長い処理遅延を特徴とする判定帰還型等化器の出力から第1の符号判定を作成するステップと、第2の符号判定が比較的短い処理遅延を特徴とする判定帰還型等化器の出力から第2の符号判定を作成するステップと、第1および第2の符号判定に基づいて判定帰還型等化器のタップの重みを決定するステップとによって動作する。第1の符号判定は、ロング・トレースバック・トレリス復号器の出力から導出してもよい。第2の符号判定は、ショート・トレースバック・トレリス復号器の出力から、あるいはロング・トレースバック・トレリス復号器の比較的遅延の短い出力から導出してもよい。  (もっと読む)

(もっと読む)

等化信号の1つから生成された制御信号に応答する複数の信号の適応等化の方法及び回路

好ましい実施形態において、少なくとも2つの等化フィルタ(各々がマルチチャンネルシリアルリンクを介して送信された信号を等化するためのもの)と、フィルタ全てによって使用される等化制御信号を生成するための制御回路とを含む適応等化回路。制御回路は、フィルタの1つによって生成された等化信号に応じて制御信号を生成し、制御信号をフィルタ全てにアサートする。好ましくは、1つのフィルタは、固定パターン信号(例えばクロック信号)に応じて等化固定パターン信号を生成し、他の各フィルタはデータ信号を等化し、制御回路は等化固定パターン信号に応じて制御信号を生成する。他の実施形態において、本発明は、事前に決定された固定パターンを示す信号に応じてフィルタのための制御信号を生成するための等化フィルタ及び回路を有する適応等化回路、適応等化回路を含む受信器、このような受信器を含むシステム、及びマルチチャンネルシリアルリンクを介して受信された信号の適応等化のための方法である。 (もっと読む)

デターミニスティックジッターイコライザ

シリアルデータ通信のためのイコライザは、デターミニスティックジッターの効果を補うために設定できる。イコライザは、負荷サイクルひずみジッターと同様、受信したシリアルデータストリームに、データ依存ジッターの効果を補うために設定できる。イコライザは、以前に受信した一つ以上のシンボルの値を判断し、回復したシンボルと比較するために設定することが出来る。イコライザは、受信データストリームの一部に基づく、データ経路に遅延を取り込むために、シリアルデータ経路に位置する可変遅延器を調整することが出来る。イコライザは、回復したシンボルと、一つ以上の以前に受信したシンボルのいずれかと異なる場合に、遅延を変化するように設定することができ、回復したシンボルと、一つ以上前に受信したシンボルのいずれかと同じ場合に、遅延を一定に維持するように設定することができる。  (もっと読む)

(もっと読む)

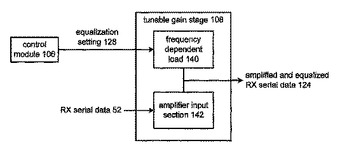

組込型等化を有するアナログフロントエンドおよびその適用

アナログフロントエンドは、制御モジュールおよび可変利得ステージを含む。制御モジュールは、アナログフロントエンドに高速シリアルデータを与えるチャネルのチャンネル応答に基づいて周波数応答設定を与えるために動作可能に結合される。可変利得ステージは周波数依存負荷および増幅器入力部を含む。周波数依存負荷は周波数応答設定に基づいて調整される。増幅器入力部は動作可能に周波数依存負荷に結合され、高速シリアルデータを受取る。増幅器入力部は周波数依存負荷と連動し、増幅され等化されたシリアルデータを生じるために、高速シリアルデータを増幅して等化する。  (もっと読む)

(もっと読む)

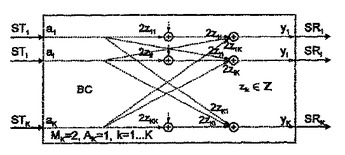

デジタルブロードキャストチャネルのための非線形事前符号化方法

ブロードキャストチャネル(BC)におけるデジタルメッセージ伝送においては、複数の加入者信号が時間及び周波数同一に中央送信器から複数の分散された、互いに協調していない受信器に伝送される。送信側の信号事前処理方法によって、全ての加入者信号及び瞬時の伝送条件の知識の下に、共通送信信号が発生され、この共通送信信号は妨害のない個別受信を可能にする。公知の非線形事前符号化方法はこの場合干渉信号を完全に抑圧し、この結果、チャネルダイバシティが利用できない。これに対して、本発明の事前符号化方法では発生する干渉信号が考慮される。モジュロ演算に基づいて、伝送チャネルは完全には等化されず、ヴァーチャルに分割され、加入者信号(STk)が周期的に継続され、最小送信電力に従って選択され、線形に事前等化され、この場合に加入者信号(STk)の間のまだ残っている残留干渉が所定の数値集合の中の特定の値をとる。数値集合はこの場合、他の加入者の干渉信号が同様にただ単にとりあえず既存の周期的継続において反映され、従って受信側ではモジュロ判定器によって除去又は必要ならば利用されうるように選択される。  (もっと読む)

(もっと読む)

帰還型フィルタリングにおいて、CCK符号化と復号とを組み合わせた判定帰還型等化器

【解決手段】判定帰還型等化器は、チップ推定をベクトルに形成するチップ推定バッファを含む。CCK復号器は、チップ推定のベクトルを復号し、CCK復号器に接続されたCCK符号化器は、チップ推定のベクトルを、有効なCCK符号ワードに再符号化する。同時に、チップスライサは、チップ推定から直接スライスされたチップを提供する。その後、更新モジュールが、有効なCCK符号ワード、及び直接スライスされたチップから、判定帰還型等化器の帰還型フィルタへの入力のために混成ベクトルを作成する。混成帰還型フィルタ入力ベクトルは、再符号化された部分のCCK符号化利得を反映しているので、推定されたチップ誤り率を減らし、判定帰還型等化器の性能を改善する。 (もっと読む)

デジタル部分応答非対称性補償

【課題】本発明は、再生されたRF信号中に強い非対称性が存在する、光記録媒体からのデータを受信し復元する方法に関する。

【解決手段】本発明によると、デジタルRF信号のデジタル部分応答非対称性補償のための方法は、再生されたビットストリームのビットクロックであるTについて、ショートTパルス(xTパルス)とロングTパルス(yTパルス)のエンベロープの測定を通してデジタルRF信号の非対称性βを検出するステップと、非対称性係数βと、xT上側及び下側エンベロープの評価を通して上側及び下側閾値を決定するステップと、デジタルRF信号の非対称性部分のみを選択して補償するステップとを含んでいる。

(もっと読む)

イコライゼーションおよびクロストーク緩和の方法および器具

マルチチャンネル通信システムにおける雑音消去の方法と器具が開示される。一つの実施例においてこのシステムは、他のチャンネルで受信されたシグナルを利用するビクティムチャンネルのFEXTを消去するように構成されている。FEXTキャンセルシグナルを発生させる場合、例えばFFEおよびDFEフィルターなどのような受信側の他のフィルターによって得られる処理の利点が利用される。その結果、処理負担の一部が他のフィルター器具によって行なわれるため、FEXTキャンセルシグナルを発生する器具の複雑性がやや単純化される。一つの構成において、プレコードFEXTフィルターが他のそれぞれのチャンネルに対応する一つ以上のプレコードFEXTキャンセルシグナルを発生する場合にプレコードFEXT消去が起こる。プレコード送信される前にFEXTをあらかじめ消去しておくため、FEXTキャンセルシグナルは送信前に他のそれぞれのチャンネルに関連するシグナルと結合される。  (もっと読む)

(もっと読む)

DUTY補正回路

【課題】 波形歪みが補正された信号を用いて復調を行うことによりビット誤り率の低いDUTY補正回路を提供する。

【解決手段】 波形の形状を観測することで、波形歪を検出することにより歪補正を行うので、受信マンチェスタ信号のDUTY比が50%を維持できない場合でも本DUTY補正回路を使用することで、補正信号は50%近傍となり、より精度の高い再生クロックを作成することができる。また、精度の高い再生クロックと波形歪みが補正された信号を用いて復調を行うことで、ビット誤り率の低い復調が可能となる。

(もっと読む)

121 - 131 / 131

[ Back to top ]