Fターム[5K029HH05]の内容

直流方式デジタル伝送 (8,390) | 受信部 (1,135) | 等化 (135)

Fターム[5K029HH05]の下位に属するFターム

量子化帰還 (4)

Fターム[5K029HH05]に分類される特許

81 - 100 / 131

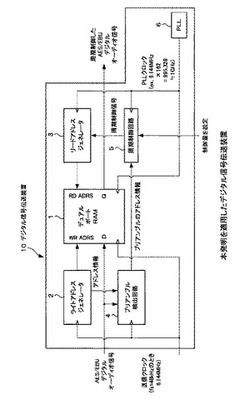

デジタル信号伝送装置,デジタル信号伝送方法及びデジタル信号伝送システム

【課題】固定クロックレートのシリアルデジタル信号の伝送時の波形周期の乱れを、ローコスト且つフレキシブルな集積化が可能なデバイスを用いて補正し、しかも伝送レート幅が広い場合にも容易に補正する。

【解決手段】シリアルデジタル信号のクロックレートよりも高速なクロックを生成するクロック生成手段6と、入力されたシリアルデジタル信号が書き込まれ、書き込まれたシリアルデジタル信号が、クロック生成手段6で生成されたクロックを読出しクロックとして読み出される記憶手段1と、記憶手段1の読出しアドレスを制御することにより、記憶手段1から読み出されるシリアルデジタル信号の波形周期を増減制御する周期制御手段5とを備える。

(もっと読む)

半導体集積回路およびイコライザの制御方法

【課題】回路規模の増大を抑制しつつ、受信したデータ信号の等化量を調整することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路100は、イコライザと、イコライザにより等化されたデータ信号の位相を検出しこのデータ信号の位相と復元クロック信号の位相とを比較し、等化されたデータ信号のビット幅が復元クロック信号の周期よりも小さいときは第1の比較信号を出力し、一方、大きいときは第2の比較信号を出力し、復元クロック信号の位相がデータ信号の位相よりも進んでいる場合には第3の比較信号を出力し、遅れている場合には第4の比較信号を出力する位相比較回路と、第3、第4の比較信号および基準クロック信号に基づいて、復元クロック信号を生成する復元クロック生成回路と、少なくとも第1、第2の比較信号に基づいて、イコライザのピーキング量を制御する制御回路と、を備える。

(もっと読む)

シリアル通信リンクのクロック・データ再生回路と使用する適応等化器

【課題】本発明は、簡単な回路で、NRZデータの異なる周波数でのジッタを効率よく除去する等化器を提供する。

【解決手段】シリアル通信リンクに使用する適応等化器システムは、そのリンクのクロック・データ再生回路の位相検出器及び再生データの周波パターンで生成されるタイミング情報を使用し、シリアル通信リンクで受信するデータが、過剰等化又は過少等化であるかを判断する。適応等化器システムの等化強度は、その判断に基づき調整される。

(もっと読む)

中継装置及び中継システム

【課題】 サーバ装置とコンソール装置間の接続距離を延長することができる中継装置を提供する。

【解決手段】 サーバ装置10に接続した送信装置30と、サーバ装置10を操作するコンソール装置20に接続した受信装置40との間に配置され、送信装置30と受信装置40との間の信号の中継を行う中継ユニット50であって、中継ユニット50を構成する中継装置51及び終端装置52は、送信装置30又は他の中継装置から受信した信号を増幅する波形調整部53を有する構成としている。

(もっと読む)

等化回路および歪軽減方法

【課題】受信信号から複数のレプリカ信号を複製し、それぞれのレプリカ信号に遅延を与え、それぞれのレプリカ信号に重み付けをして加減算し、受信信号の歪を軽減する等化回路において、少ないレプリカ信号数により補正能力を向上させる。

【解決手段】レプリカ信号間の遅延時間のうち少なくとも1つが他の遅延時間とは異なるように遅延量を与える。例えば、レプリカ信号の複製数が奇数の場合には中央のレプリカ信号の遅延時間を基準遅延時間とし、レプリカ信号の複製数が偶数の場合には中央2個のレプリカ信号の遅延時間の平均を基準遅延時間とし、その基準遅延時間と各レプリカ信号の遅延時間との差の最大値がシンボルレートの逆数の時間の0.75倍よりも大きく1.2倍以下であるようにする。

(もっと読む)

波形等化係数調整方法および回路、レシーバ回路、ならびに伝送装置

【課題】波形等化係数の調整時間を短縮することが可能な波形等化係数調整技術を提供する。

【解決手段】波形等化係数調整方法において、任意の信号列の場合のみジッタまたは振幅を測定し、波形等化係数を調整する。特に、受信信号の内、010または101信号以外の信号を用いて、符号反転時間を測定する。このような信号を用いた場合の符号反転時間は、従来の技術に比べてより急峻になるため、波形等化係数の調整時間を短縮することができる。

(もっと読む)

信号等化器

【課題】コイルを使用することなくかつ伝送線路をそのまま等化器の回路部品に使用して、GHz級の高い周波数においても優れた信号減衰を補償する信号等化器を提供する。

【解決手段】送信端と受信端の間を接続して信号を伝送する主伝送線路TL1と、前記主伝送線路の受信端側に前記受信端と並列に接続された受信側終端抵抗R2と、前記受信側終端抵抗に並列に接続された、伝送線路TL2と前記伝送線路とインピーダンス値が異なる終端抵抗R3との直列回路からなり、前記主伝送線路の受信端側に所望の特定周波数帯域での電圧振幅を他の周波数帯域より大きくする周波数特性を与える周波数特性調整用回路FR1と、を備えた。

(もっと読む)

クロックデータ復元装置

【課題】より正確にクロック信号およびデータを復元することができるクロックデータ復元装置を提供する。

【解決手段】クロックデータ復元装置1は、入力したデジタル信号に基づいてクロック信号およびデータを復元する装置であって、イコライザ部10、サンプラ部20、クロック生成部30、イコライザ制御部40および位相モニタ部50を備える。イコライザ部10、サンプラ部20およびイコライザ制御部40によるループ処理により、イコライザ部10におけるデジタル信号のレベル調整量の制御が行われるが、一方で、クロック信号CKとデジタル信号との間の位相差が所定値より大きいときには当該制御が位相モニタ部50により停止される。これにより、より正確にクロック信号およびデータが復元され得る。

(もっと読む)

非対称チャネルの存在下における非線形判定帰還型等化のための方法および装置

非線形チャネルの存在下で判定帰還型等化について使用される1つまたは複数のラッチの閾位置を決定する方法および装置が提供される。判定帰還型等化器について使用されるラッチは、入力データが第1バイナリ値からの遷移を含むだけであるように、入力データを制約すること、制約された入力データに関連する片側データ・アイの複数のサンプルを取得すること、サンプルに基づいてラッチの閾位置を決定すること、および、チャネルの非線形性に対処するために、決定されたしきい値位置を変換することによって位置決めされる。たとえば、非線形マッピング・テーブルは、距離に基づいて、測定された閾値を変換済み閾値にマッピングすることができる。  (もっと読む)

(もっと読む)

プログラマブルロジックデバイス用のデジタル適応回路網および方法

【課題】プログラマブルロジックデバイス用のデジタル適応回路網および方法を提供すること。

【解決手段】本発明は、着信データ信号の等化を制御する方法を提供する。該方法は、該データ信号の中の2つの連続する異なる値を有するビットを検出することと、該2つのビット間の該着信データ信号における遷移が、比較的遅いか、あるいは比較的早いかを決定することと、該遷移が、比較的遅い場合、該着信データ信号の該等化を増加させることとを包含する。

(もっと読む)

チャンネルの相互シンボル干渉を減らし、信号利得損失を補償する受信端

【課題】チャンネルの相互シンボル干渉ISIを減らし、信号利得損失を補償する受信端を提供する。

【解決手段】チャンネルを通過した信号を入力するハイパスフィルタと、第1及び第2制御信号に応答してハイパスフィルタの出力と第1電源電圧とを比較して第1及び第2出力信号を発生させるシュミットトリガーとを備えるシングルエンディド信号方式のチャンネルに連結される受信端である。制御部は、シュミットトリガーの第1及び第2トリガー電圧のレベルをシフトさせるために、第1及び第2制御信号を発生させる。増幅部は、シュミットトリガーの第1及び第2出力信号を入力して受信端の出力信号を発生させる。これにより、受信端は、ハイパスフィルタと第1及び第2制御信号によって制御されるシュミットトリガーとによって、データ伝送チャンネルのISIと信号利得損失とを補償する。

(もっと読む)

信号調整方法及びアダプティブイコライザ

【課題】イコライザに適用される補償量をその媒体に起因する減衰レベルにできるだけ合致させ、信号の出力特性を、信号の通信に使用される特定の通信経路と一貫して独立に維持すること。

【解決手段】周波数依存性歪に対する損失補償及びDCオフセット歪に対する補償の少なくとも一方を、該歪が生じる前又は後の信号に適用し、出力信号を生成する。各データ値は出力信号のサンプリングに基づく高い値又は低い値を有し、誤差値は歪の残留を示す。本方法は、1つ以上のフィルタパターンを一群の複数のフィルタから選択する。選択されたフィルタパターンに対応するデータ値の1つ以上のパターンについて、出力信号を監視する。本方法は、1つ以上の選択されたフィルタパターンの1つに対応する出力信号中のデータ値のパターンを検出する。本方法は、誤差値に基づいて、データ信号に適用されるオフセット補償及び損失補償の少なくとも一方を調整する。

(もっと読む)

等化回路

【課題】等化回路を構成する各素子の帯域特性が有限である等化回路において、等化特性を最大限に引き出す。

【解決手段】入力信号を複製して重み付けを行い、複製されて重み付けされた信号を元の入力信号に重ね合わせることで信号波形を等化する回路において、複製された信号の帯域を制限し、複製されて重み付けされた信号を元の入力信号から減算する。

(もっと読む)

信号調整方法及び受信機

【課題】イコライザに適用される補償量をその媒体に起因する減衰レベルにできるだけ合致させ、信号の出力特性を、信号の通信に使用される特定の通信経路と一貫して独立に維持すること。

【解決手段】本発明の一実施例による信号を調整する方法は、入力データ信号を受信するステップと、入力データ信号にオフセット補償を適用し、出力信号を生成するステップとを有する。本方法は、クロック信号を利用して出力信号をサンプリングし、複数の境界値を生成するステップも含み、該各々の値は出力信号のサンプリングに基づく高値又は低値を有する。本方法は、境界値の高値又は低値に少なくとも基づいて、入力データ信号に対するオフセット補償量を調整するステップを更に含む。

(もっと読む)

ディジタル伝送システムおよびディジタル伝送方法

【課題】波形劣化要因の状況が高速ないし低速(長周期)で変動する伝送路どちらに対しても対応可能であり、伝送品質劣化を抑圧し、安定した通信を可能にする。

【解決手段】伝送キャリアには光を使用し、変調光を偏波スクランブルし、伝送路としては光ファイバを使用し、等化特性を予め固定して設定したトランスバーサル型等化回路を有する受信装置を用いて偏波スクランブルされた変調光を受信して復調する。また、伝送路の途中に一つないし複数の偏波スクランブル回路を挿入して変調光を偏波スクランブルすることもできる。この場合には、送信側における偏波スクランブルに代えて伝送路の途中に挿入された偏波スクランブル回路によって変調光を偏波スクランブルすることもできる。

(もっと読む)

信号調整方法及び受信機

【課題】イコライザに適用される補償量をその媒体に起因する減衰レベルにできるだけ合致させ、信号の出力特性を、信号の通信に使用される特定の通信経路と一貫して独立に維持すること。

【解決手段】本発明の一実施例による信号を調整する方法は、入力データ信号を受信する。本方法は、入力データ信号にオフセット補償を適用し、出力信号を生成する。本方法は、クロック信号を利用して出力信号をサンプリングし、複数のデータ値及び境界値を生成し、各値は出力信号のサンプリングに基づく高い値又は低い値を有する。本方法は、2つの連続するデータ値間の値の遷移を検出し、該2つの連続するデータ値間でサンプリングされた境界値を判定する。本方法は、境界値の高い又は低い値に少なくとも基づいて、入力データ信号に適用されるオフセット補償量を調整する。

(もっと読む)

信号品質最適化装置及び信号品質最適化システム

【課題】高速なシリアル伝送における信号の品質を最適化する装置及びシステムを提供する。

【解決手段】受信部1は、受信データを入力するとともに、前記受信データの補正を指示する調整制御信号を入力した場合には前記調整制御信号に従って前記受信データを補正して出力し、前記調整制御信号を入力しない場合には前記受信データを補正せずに出力するイコライザ11と、

イコライザ11が出力したイコライザ出力データを入力し、入力したイコライザ出力データのBERを計測し、計測したBERの計測結果に基づき前記調整制御信号を生成し、生成した前記調整制御信号をイコライザ11に出力する一連の動作を、イコライザ11から入力するイコライザ出力データのBERが最低になるまで繰り返すBER計測機能部13とを備えた。

(もっと読む)

直流成分除去フィルタ、方法およびプログラム

【課題】 回路規模の削減および処理内容の簡素化が可能な直流成分除去フィルタ、方法およびプログラムを提供すること。

【解決手段】 直流成分除去フィルタ100は、入力データに対してN個の移動平均を計算する遅延回路110、112、加算器120、122、D型フリップフロップ130、係数乗算器132からなる移動平均演算手段と、移動平均の計算対象となっているN個の入力データの中から中央の入力データを取り出してこの入力データの値から移動平均値を減算する加算器124からなる減算手段とを備えている。

(もっと読む)

シリアル転送用インターフェース

【課題】環境の変化やLSIプロセスによる特性のばらつきが生じる場合であっても、安定で高品質な信号伝送を実現するシリアル転送用インターフェースを提供する。

【解決手段】課題を解決するために、シリアル転送用インターフェース10に、信号波形のひずみを補正する信号波形補正部11と、信号波形を同期クロックにあわせてラッチして後段回路に出力するラッチ部12と、信号波形補正部11のフィルタ特性を所定に範囲で変更するフィルタ特性調整部13と、所望の位相を有する同期クロックを生成するクロック生成部14と、テストパターンの検出やフィルタ特性調整部13及びクロック生成部14の制御を行うパターン判定部15と、を少なくとも備える。

(もっと読む)

制御システム

【課題】線間の容量及びデバイスの容量により信号波形のレベルの低下及び積分値が低下しても正しく通信を行うことができ、コントローラから1対多の通信で複数のデバイスを制御する場合にも制御線の数を増やす必要がない。

【解決手段】本発明の制御システムは、複数のモジュール2−1、2−2、・・・2−nを同一の状態に制御するためのデバイス1の制御に関する信号を予め設定された閾値に基づいて整形する波形整形ブロックを、複数のモジュール2−1、2−2、・・・2−nのうちのいずれかに設け、波形整形ブロックにより整形されたデバイス1の制御に関する信号を順次次段に送出するものである。

(もっと読む)

81 - 100 / 131

[ Back to top ]