Fターム[5K029HH27]の内容

直流方式デジタル伝送 (8,390) | 受信部 (1,135) | 送信部との同期;同期信号検出 (111) | クロック系列を選択するもの (20)

Fターム[5K029HH27]に分類される特許

1 - 20 / 20

通信システム及びそのデバイス

【課題】1本の信号線を用いて双方向のシリアル通信を行う通信システム及びそのデバイスを提供することを目的とする。

【解決手段】第1デバイス11と第2デバイス12間を1本の信号線で接続し、互いにレベルの異なる第1レベルと第2レベル、及び前記第1レベルと第2レベルの中間レベルを用いてシリアル通信を行う通信システムであって、第1デバイスは、第1レベルと中間レベルを繰り返すことで第2デバイスにクロックを送信し、第2デバイスは、受信したクロックの中間レベルの期間に第2レベルを出力するか否かで第1デバイスに情報を送信し、第1デバイスは、第2デバイスが情報を送信していない場合に、クロックの中間レベルの期間に第2レベルを出力するか否かで前記第2デバイス12に情報を送信する。

(もっと読む)

半導体デバイス、画像処理装置

【課題】複数のデータ伝送路のタイミングを低コストで同期可能な半導体デバイスを提供すること。

【解決手段】送信側から受信側にデータをシリアル送信する半導体デバイス100であって、データ転送の合間に、同期判定用のコードを送信する同期判定コード送信手段301,302と、送信側と受信側に共通のクロック信号を提供するクロック信号提供手段103と、クロック信号に同期して同じデータを送信する複数の伝送路117と、受信側に提供されたクロック信号の位相を、それぞれ異なる所定量遅延させ複数の遅延クロック信号を生成するクロック生成手段110と、遅延クロック信号に同期して伝送路を介して送信されたデータを取り込む複数の受信バッファ111と、コードを予め定められた規則に基づき検証して複数の受信バッファから1つの受信バッファを、複数の遅延クロック信号から1つの遅延クロック信号をそれぞれ選択する選択手段113、115と、を有する。

(もっと読む)

受信回路

【課題】 LSIの製造ばらつき、トランジスタのランダムばらつき、電源ノイズ、信号ノイズによって、送信回路の基準信号と受信回路の基準信号が固定的にずれたり、時間的に変動したりする場合でも期待通りの送受信を行うことができる通信回路を提供する。

【解決手段】 シリアル信号を受信するが、受信信号にあらわれる規則的な有効データ期間のずれに対して、受信回路がデータを取り込む契機となるクロック信号を送信・受信回路接続時、電源投入時または通常動作時に最適化することでエラーレートが最小となる受信回路を提供することができる。

(もっと読む)

半導体装置

【課題】動作用クロックの周波数にかかわらず、所要のビットレートに近いビットレートでシリアル通信を行えるようにする。

【解決手段】半導体装置は、所定の動作用クロックに従って動作するシリアルコミュニケーションインタフェース(109)を含む。上記シリアルコミュニケーションインタフェースに、上記動作用クロックをカウントし、それに基づいて、上記単位転送時間を規定するための基本クロックを生成するボーレートジェネレータ(202)と、生成された基本クロックに従って送受信制御を行うための送受信コントローラ(201)とを設ける。さらに上記シリアルコミュニケーションインタフェースに、上記動作用クロックの上記ボーレートジェネレータへの供給を部分的にマスクすることで所望のビットレートを実現可能なビットレートモジュレータ(203)を設けることで、所要のビットレートに近いビットレートでのシリアル通信を実現する。

(もっと読む)

半導体集積回路装置

【課題】外部のデバイスに接続される回路とLSI内部の回路との間におけるタイミング設計を不要とすること。

【解決手段】半導体集積回路装置は、外部デバイスに対して接続されるインタフェース回路であって第1のクロック信号が供給される第1の回路と、第1のクロック信号を分周した第2のクロック信号が供給される第2の回路と、第2のクロック信号を第1のクロック信号に基いて遅延させた送受信タイミング信号を生成するタイミング生成回路と、第2の回路から受信した信号を第1のクロック信号に同期してサンプリングする複数段のシフトレジスタと該複数段のシフトレジスタに対する入出力信号に含まれるハイレベルの信号とロウレベルの信号の多数決を送受信タイミング信号に同期して行うとともに多数決により決定された信号を第1の回路に出力する多数決回路とを有する第1の位相調整回路とを備えている。

(もっと読む)

送信機および通信システム

【課題】周波数の変化に対応でき、且つクロストークに起因するジッターの低減を図ることができる送信機、および通信システムを提供する。

【解決手段】送信機2は、発振回路4と、送信部5とを備える。発振回路4は、基準クロックCKrefを入力して、同一の周期を有すると共に位相が互いに異なるN相(Nは2以上の整数)のクロックCK1〜CKNを生成して出力する。送信部5は、発振回路4から出力されたクロックCK1〜CKNを入力して、このクロックCKn(nは1以上N以下の各整数)にシリアルデータ信号Snを同期させて高速シリアル伝送線路Lnを介して受信機3に送信する。

(もっと読む)

半導体装置及びデータ処理システム

【課題】電力消費を抑えて長周期ジッタに起因するビットエラーの発生を抑制することができるシリアル受信回路を提供する。

【解決手段】クロック信号(CK3)に同期してシリアル信号を受信するシリアル受信回路(2)は、前記クロック信号に対して位相をずらした複数相のサンプリング位相(CLK(1)〜CLK(N))に同期して前記シリアル信号をサンプリングし、サンプリングした信号に基づいて前記シリアル信号の位相変動によるサンプリング結果への影響が少ないサンプリング位相を最適位相と判別して当該最適位相によりサンプリングした信号を受信データとする受信動作を行い、前記最適位相の判別動作として、第1モード(初期位相検出)と、前記第1モードで判別された最適位相の最適性を前記サンプリング数を減らしたサンプリング結果に基づいて判別する第2モード(位相追跡)と、を有する。

(もっと読む)

データ送受信方法

【課題】同期式連続データ伝送の信頼性を確保すると共に容易に設計することができるデータ送受信方法を提供する。

【解決手段】データ送信装置11は、通信開始時にテストデータをデータ受信装置12に送信する。データ受信装置12は、システムクロックを数倍に逓倍した内部クロックによりテストデータをサンプリングしてキャプチャ回路23に取り込み、データ取り込みタイミング制御部24において上記取り込みデータから最適のデータ取り込みタイミングを選択して設定する。データ受信装置12は、通常のデータを取り込む際は、データ取り込みタイミング制御部24において設定された最適のデータ取り込みタイミングにて受信データの取り込みを行う。

(もっと読む)

クロック抽出回路

【課題】エラーが発生する前にエラー発生の予兆を知る。

【解決手段】データ入力信号Dinからデータ入力信号Dinに係るクロック信号CK1を再生するクロック再生回路11と、再生されたクロック信号CK1に同期すると共に再生されたクロック信号CK1に対して一定の位相差を有する1または2以上のサンプリングクロック信号CK2、CK3を生成するサンプリングクロック生成回路12と、1または2以上のサンプリングクロック信号CK2、CK3および再生されたクロック信号CK1によってそれぞれデータ入力信号Dinをサンプルホールドするサンプルホールド回路13と、サンプルホールド回路13のそれぞれのサンプリング結果の論理値の全てが同一ではない場合にエラー予兆信号Epを出力するエラー判定回路14と、を備える。

(もっと読む)

データ受信装置

【課題】シリアルデータの各データにデータ幅の不均等や位相差があっても、サンプリングミスを防止することのできるデータ受信装置を提供する。

【解決手段】データ受信装置1は、多相クロック生成部11が、入力されたクロック信号CKから相互の位相差がT/7である7個のクロックC1〜C7を生成し、位相調整部21、22、23が、位相制御信号A、B、Cによる設定に応じてクロックC1〜C7の個々のクロックの位相を調整して、サンプリングクロックCA1〜CA7、CB1〜CB7、CC1〜CC7として出力し、シリアルパラレル変換部31、32、33が、サンプリングクロックCA1〜CA7、CB1〜CB7、CC1〜CC7により、入力されたシリアルデータA、B、Cをそれぞれサンプリングし、7ビットのパラレルデータA、B、Cに変換する。

(もっと読む)

受信装置、受信方法

【課題】回路規模の増大を抑える受信装置、受信方法を提供する。

【解決手段】複数の伝送路を介して送信装置に接続されることができる受信装置であって、複数の伝送路のうち所定の伝送路である第1伝送路からの信号に基づいて第1クロックを生成する第1クロック生成部と、第1クロックのタイミングに基づいて第1伝送路からの信号を復調する第1復調部と、複数の伝送路のうち第1伝送路と異なる伝送路である第2伝送路からの信号の位相に基づいて、第1クロックの位相を調整して第2クロックを生成する第2クロック生成部と、第2クロックのタイミングに基づいて第2伝送路からの信号を復調する第2復調部とを備えた。

(もっと読む)

半導体装置

【課題】 シリアルデータの高速化にともなう受信性能の低下および連続同符合データ受信によるクロックデータリカバリー回路の精度低下を防止し、尚且つ消費電力の低いクロックデータリカバリー回路を提供する。

【解決手段】 シリアルデータを受信するSerDes回路101と、並走クロック信号を受信する参照SerDes回路102とを有し、SerDes回路101は、参照SerDes回路102の生成した位相制御信号P_CSを用いて位相制御された再生クロックにより受信したシリアルデータの直列並列変換を行う。

(もっと読む)

位相補正方法及び位相補正装置

【課題】 大容量のシリアルデータ信号を比較的短い時間で転送でき、且つ、ジッタの影響を十分に抑えることができる位相補正方法及び位相補正装置を提供する。

【解決手段】 IrDA規格のFIRモードの赤外線通信可能な通信制御システムにおいて、受信したシリアルデータ信号をサンプリングタイミングに同期してサンプリングし、サンプリングで検出された補正対象パルス信号が、直前に検出された基準パルス信号の検出タイミングを基準とした2つのパルス開始タイミングの2等分点で検出された場合に、直前のパルス信号とのパルス間隔を求め、パルス間隔が第1基準間隔より短い場合は、補正対象パルス信号が直前の最も近いパルス開始タイミングのパルス信号であると判定し、パルス間隔が第2基準間隔より長い場合は、補正対象パルス信号が後の最も近いパルス開始タイミングのパルス信号であると判定する。

(もっと読む)

省電力のクロッキング技術

【課題】電力消費が低減したクロック信号を提供するための方法及びシステムを提供すること。

【解決手段】ハイブリッド・クロック・システムと呼ばれる、電力消費が減少したクロック信号を提供するための方法及びシステムが提供される。ハイブリッド・クロック・システムは、高速データ転送のためにPLLを用いるが、より少ない電力を消費しながらデータを転送するための省電力モードを提供する。通常モードにおいて、ハイブリッド・クロック・システムは、PLLを駆動する、低周波数で動作する基準クロックを含む。PLLは、基準クロックの周波数をずっと高い周波数に逓倍し、基準クロックを直接データ転送回路に与える。省電力モードにおいて、ハイブリッド・クロック・システムは、PLLをオフにし、基準クロックを直接データ転送回路に接続する。

(もっと読む)

シリアルクロック及びデータリカバリのための信号インタリービング

【課題】シリアルデータストリームからタイミング情報及びデータを回復させるクロック及びデータリカバリ(CRD)システム及び方法を提供する。

【解決手段】CDRシステム(100)は回復状態のクロック/データ信号を生じさせるサンプリング回路(105)及びインタリービングフィードバックネットワーク(110)を有する。このネットワークは、回復信号に基づき制御信号を生じさせる論理回路(115)、制御信号に基づき大域クロック信号の4つの位相から選択を行う第1マルチプレクサ(120)、選択大域クロック信号に基づき遅延信号を生じさせる第2マルチプレクサに結合されている第1遅延セル組を含む第1遅延ロックループ(130)及び1組の移相フィードバック信号を生じさせる第2遅延セル組を含む第2遅延ロックループ(135)を有する。

(もっと読む)

クロックアンドデータリカバリ回路及びSERDES回路

【課題】クロックアンドデータリカバリ回路の動作余裕度の大きさを測定可能とするSERDES回路の提供。

【解決手段】シリアルデータサンプリング回路(101)と、クロックとデータの位相関係を検出する位相比較器(102)と、位相比較結果(UP/DOWN)に基づき位相制御信号を出力する位相制御器(103)と、互いに異なる位相の複数のクロック信号よりなる多相クロックを受け、位相制御信号に基づき位相を補間したクロック信号をデータサンプリング回路(101)に供給する位相補間器(104)とがループを構成する。この位相制御器(103)は、位相制御信号とは別の位相制御信号Aを生成して別の位相補間器(105)に供給し、多相クロックを受け位相制御信号Aに対応して補間したクロック信号に基づき入力データをサンプルする別のデータサンプリング回路(106)を備え、好ましくは、データをサンプルするための閾値レベルが可変に設定される。

(もっと読む)

受信装置

【課題】 クロックの同期を行うことなく高速のシリアル通信で高い通信効率を維持しながら通信を行うことが可能な受信装置を実現する。

【解決手段】 シリアル伝送路を用いてパケット通信を行う受信装置において、シリアル伝送路を伝播する伝送信号を異なる位相のクロック信号のタイミングで取り込んで受信データを生成する複数の受信回路と、これら受信回路でそれぞれ生成された受信データの正否をそれぞれ判定する複数の判定回路と、これら判定回路において正しいと判定された受信データを選択する選択回路とを設ける。

(もっと読む)

調歩同期通信用受信回路

【課題】高速のビットデータを受信することができ、かつ、受信データを正確に再現することができる調歩同期受信回路を提供する。

【解決手段】受信シリアルデータ57のビットレートと同等のスピードで位相が等間隔にずれた複数のクロック0〜nを生成し、この各クロックで受信シリアルデータをサンプリングしそのデータを、複数のレジスタ回路52_0〜52_nに保持する。複数のクロックのうち、受信シリアルデータを最適な位置でサンプリングするクロックを検出し、そのクロックでサンプリングされたデータを保持するレジスタ回路からのデータを出力させる。このような構成では、ビットレートの効率が大幅に向上し、また、各クロックでサンプリングした受信データから最適なデータを選択するようにしたので、クロックの切替で発生するノイズ等の影響を受けることが無く、受信データを正確に再現することが可能となる。

(もっと読む)

半導体装置

【課題】 本発明は、搬送波からパルス幅が一定なクロック信号を生成する半導体装置を提供することを課題とする。また、パルス幅が一定なクロック信号を用いて、搬送波からデータを正確に取得することができる半導体装置を提供することを課題とする。さらに、PLL回路と比較して、回路構成が簡単であり、その規模が小さく、さらに消費電力が小さい半導体装置を提供することを課題とする。

【解決手段】 本発明は、100%変調を含む搬送波を分周した信号をそのままクロック信号として用いず、100%変調を含む搬送波を分周した信号と復調信号とを用いてクロック信号を生成する補正回路を有する。上記の補正回路を有する本発明は、パルス幅が一定なクロック信号を生成することができる。

(もっと読む)

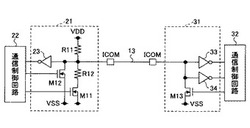

データ転送方式

【課題】commonとなるGNDの弱い状態(GND間にインピーダンスの発生するような)下において発生していたクロストークやグランドバウンスによる論理反転・発振等を回避することができるデータ転送方式を提供すること。

【解決手段】送信側領域と受信側領域との領域を持ち、送信側領域中には調整クロック制御手段、同期データラッチ、調整クロック・データラッチを具備し、受信側領域中には調整クロック制御手段、同期データラッチ、調整クロック・データラッチを具備し、前記調整クロック制御手段に対して制御パラメータを設定する調整クロック制御指示手段をシステム中に具備する。

(もっと読む)

1 - 20 / 20

[ Back to top ]