Fターム[5K029KK22]の内容

直流方式デジタル伝送 (8,390) | 監視;試験 (418) | 測定値、検出値 (264) | 時間;位相 (92)

Fターム[5K029KK22]の下位に属するFターム

ジッタ (57)

Fターム[5K029KK22]に分類される特許

1 - 20 / 35

電子装置

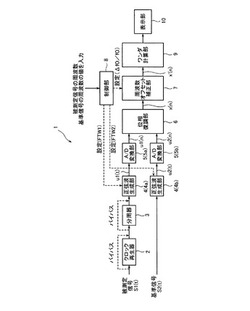

ワンダ測定装置及びワンダ測定方法

【課題】簡単な回路構成で高精度なワンダ測定が行える。

【解決手段】正弦波生成部4a,4bは、クロック信号からなる被測定信号と基準信号とを動作クロックとしてそれぞれ正弦波電圧信号u1(t),u2(t)を出力する。位相復調部6は、2つの正弦波電圧信号u1(t),u2(t)を一定周期でサンプリングして得られる系列u1(n),u2(n)間の瞬時位相の差に基づく時間差系列x(n)を出力する。制御部8は、予め設定される被測定信号の公称周波数と基準信号の公称周波数とに基づき、規定の出力周波数f0に最も近づく周波数チューニング・ワードFTW1,FTW2を1組の正弦波生成部4a,4bに設定して2つの正弦波電圧信号u1(t),u2(t)の出力周波数を制御し、回路雑音に起因する測定誤差を抑圧する。

(もっと読む)

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

回路シミュレータプログラム,装置およびアイパターン生成方法

【課題】アイパターンを高速かつ高精度に生成する。

【解決手段】対象回路に立上りステップ信号を入力した際の立上りステップ応答のシミュレーションと前記対象回路に立下がりステップ信号を入力した際の立下がりステップ応答のシミュレーションとを実行し、前記立上りステップ応答のシミュレーションおよび前記立下がりステップ応答のシミュレーションの結果を解析させ、その解析結果に基づき、前記アイパターンのアイ内の上側形状を規定する上側テストパターンとアイパターンのアイ内の下側形状を規定する下側テストパターンとを生成し、前記対象回路に前記上側テストパターンおよび前記下側テストパターンを入力した際の応答のシミュレーションを実行する。

(もっと読む)

差動信号伝送回路

【課題】スキューを低コストで低減した差動信号伝送回路を提供する。

【解決手段】差動信号伝送回路1は、第1の接続部6Aおよび第2の接続部6Bを有し、差動信号を送信する送信回路5と、第3の接続部9Aおよび第4の接続部9Bを有し、差動信号を受信する受信回路8と、一端が第1の接続部に接続され、差動信号の対をなす一方の信号を伝播する第1の信号線路11Aと、一端が第2の接続部に接続され、差動信号の対をなす他方の信号を伝播するとともに第1の信号線路より電気長が長い第2の信号線路11Bと、第1の信号線路の他端と第3の接続部とに接続された受信側調節配線10Aと、を備え、第1の接続部から第1の信号線路および受信側調節配線を介して第3の接続部までの電気長と、第2の接続部から第2の信号線路を介して第4の接続部までの電気長との差に対応するスキューが、許容される最大スキュー以下となるように調節されている。

(もっと読む)

可変シンボル間干渉発生装置及びデータ生成方法

【課題】データ信号に与えるシンボル間干渉量を連続的に且つ正確に調整できるようにする。

【解決手段】データ信号を周波数応答可変のプログラマブル・フィルタ1010と、PCB配線、一定長のケーブル、ディスクリート・フィルタなどの固定周波数応答を有する固定フィルタ1015を通すことによって、データ信号に与えるシンボル間干渉の量を連続的に調整する。プログラマブル・フィルタ1010は、そのパラメータを調整することで、その挿入利得又は挿入損失を調整でき、これによって、シンボル間干渉量を連続的に可変できると共に正確に調整できる。

(もっと読む)

送信回路

【課題】出力するシリアルデータのビット位置を容易に特定することが可能な送信回路を得ること。

【解決手段】本発明にかかる送信回路は、シリアルクロックと当該シリアルクロックに同期したシリアルデータとを出力する送信回路1aであって、シリアルデータのビット位置を特定するためのパルス信号を、所定の間隔で生成し出力するシリアルデータ計数部3a、を備え、その回数を数えることにより、シリアルデータのビット位置を容易に特定可能な構成とした。

(もっと読む)

情報受信制御装置、情報受信制御方法、情報受信制御プログラムおよび記録媒体

【課題】調歩同期式のシリアル通信における通信データのサンプリングタイミングを簡単な回路構成によって制御することで通信データ単位でのサンプリング誤差の累積を防止し、通信データの受信エラーの発生を抑止することができるようにした情報受信制御装置、情報受信制御方法、情報受信制御プログラムおよび記録媒体を提供する。

【解決手段】調歩同期式のシリアル通信に用いられるビット単位の通信データの受信の際に、「基準クロックを分周したカウンタークロック」のカウンタークロック数に対する、「基準クロックから算出される分周値をもとにハード特性を考慮した特性分周値」を計算する。分周値と特性分周値を用いて算出されるそれぞれのカウンタークロックに基づく誤差からビット単位での誤差量を算出し、その誤差量をもとにカウンタークロック数の計数を行う際の初期値を決定する。

(もっと読む)

信号断検出回路、信号断検出方法及び光受信器

【課題】異なるビットレートの信号を時分割で受信した場合においても、ビットレートに関係なく信号断検出時のビットエラーレートを等しくし得る信号断検出回路を提供する。

【解決手段】信号断検出回路1は、複数のビットレートのそれぞれに固有の光受信レベルの閾値(201,601)を用い、信号入力部10の出力信号102に含まれる当該各ビットレートの信号についてその有無を検出する信号検出部(20,60)と、信号入力部10の出力信号102が複数のビットレートのいずれに属するかを判別するビットレート判別部70と、ビットレート判別部70で判別されたビットレートについて信号検出部(20,60)が信号の無を検出した場合に、信号断を示す信号(ローレベル電圧のLOS信号804)を出力する信号断アラーム生成部80と、を備えたことを特徴とする。

(もっと読む)

通信機器およびそのプログラム

【課題】より安全にネットワークに接続することができる通信機器を実現する。

【解決手段】本発明に係るプログラマブル表示器1は、トークンを利用して通信を行うプロフィバスネットワーク2に接続される通信機器であって、プロフィバスネットワーク2からデータを受信する通信受信部31と、プロフィバスネットワーク2にデータを送信する通信送信部38と、通信受信部31が受信したデータのボーレートを検出する受信ボーレート検出部32と、受信ボーレート検出部32によって検出された検出ボーレートと、プログラマブル表示器1に設定された設定ボーレートとを比較するボーレート比較部34とを備え、通信送信部38は、上記検出ボーレートと上記設定ボーレートとが異なる場合、トークンの発信を行わない。

(もっと読む)

通信装置および通信装置の製造方法

【課題】通信回路に供給されるシステムクロックの異常検出の確実性を高めることができる通信装置を提供する。

【解決手段】CMOS回路を有するシステムクロック生成回路3は、周波数f1を持つシステムクロックSCKを生成する。CMOS回路を有する監視クロック生成回路4は、周波数f1より低い周波数f2を持つ監視クロックWCKを生成する。通信制御回路5は、システムクロックSCKの供給を受けて動作し、バス通信線2を通じて外部機器との通信を行う。クロック監視回路7は、システムクロックSCKの周波数と監視クロックWCKの周波数との相対関係を監視する。クロック監視回路7は、その相対関係が変化するとシステムクロックSCKが異常であると判断し、異常検出信号Saを出力する。通信I/F回路6は、異常検出信号Saが出力されるとバス通信線2を開放する。

(もっと読む)

テスト信号による通信路の劣化部位の判定機能を有する送受信システム

【課題】通信不良が発生する前に、通信路の送信部、通信線、受信部の中から劣化部位を安定して判定することが可能なシステムを提供する。

【解決手段】処理部12のテスト用データ生成回路122で生成されたデータはシリアルデータとして送信部14に送られ、送信部14からシリアルデータとして外部装置にシリアル通信される。受信部16は、外部装置からのシリアル通信によるシリアルデータを受信し、受信したシリアルデータは、処理部12の位相検出回路123において位相データを取得する。取得された位相データは、劣化判定回路120に送られる。劣化判定回路120で位相データの劣化判定を行ない、劣化判定の結果得られた劣化判定情報を劣化判定情報保持回路121に送る。劣化判定情報保持回路121は劣化判定情報を記憶する。表示手段18は、劣化判定情報保持回路121で記憶された劣化判定情報は表示手段18に表示される。

(もっと読む)

信号受信装置及び信号処理方法

【課題】簡易な構成で、PPM信号を確実に再生するために正確にPPM信号をサンプリングできる信号受信装置を提供する。

【解決手段】パルス位置変調信号のうち検出対象区間から任意のHパルスの立ち上がりまたは立ち下がりエッジを開始点として設定する第1の設定手段と、前記検出対象区間における複数のHパルスの間隔に基づいてサンプリング周期を算出する算出手段と、前記検出対象区間について、前記開始点から前記サンプリング周期の倍数を基準点とし、前記基準点からの前記複数のHパルスの発生位置を検出する検出手段と、前記複数のHパルスの発生位置についてヒストグラムを生成する生成手段と、前記基準点に前記ヒストグラムでピークとなる値を加えた位置を前記パルス位置変調信号における再生対象信号区間のサンプリング点と決定する決定手段と、前記サンプリング点に基づいて前記再生対象信号区間を再生する再生手段とを有する。

(もっと読む)

ボーレートエラー検出回路、ボーレートエラー検出方法

【課題】シリアル通信におけるシンクフィールドの異常波形を検出すること。

【解決手段】ボーレートエラー検出回路は、エッジディテクタと、スタートビットサンプリング回路と、異常波形検出回路とを備える。エッジディテクタは、シリアル通信のボーレートを調整するためのシンクフィールドを受け取り、シンクフィールド中のエッジに応答してエッジ検出信号を生成する。スタートビットサンプリング回路は、エッジ検出信号及び内部クロック信号に基づいてシンクフィールドのスタートビットのビット幅を計測し、計測されたビット幅を期待値として示す期待値信号を生成する。異常波形検出回路は、エッジ検出信号及び内部クロック信号に基づいてスタートビット以降のエッジ間の幅を計測し、エッジ間幅と期待値信号で示される期待値との間の誤差が所定の許容誤差範囲を超える場合に異常波形検出信号を生成する。

(もっと読む)

受信装置

【課題】プリアンブルを用いた符号のサンプリングをより適切に行う技術を提供する。

【解決手段】符号を含む信号を受信しこの信号からエッジを検出する信号エッジ検出部と、検出された前記エッジの立上り時又は立下り時から前記信号のパルス幅検出の基準点を検出する基準点検出部と、前記エッジの立上り時又は立下り時と前記基準点からパルス幅を検出するパルス幅検出部と、前記パルス幅のヒストグラムを生成し、このヒストグラムの分析結果から前記符号のサンプリング点を判定するサンプリング点判定部と、を有しこの判定結果に基づいて前記符号のサンプリングを実施することを特徴とする受信装置。

(もっと読む)

非対称な遅延に関して通信システムを診断する方法及び装置

本発明は、非対称な遅延に関して通信システムを診断するための方法及び装置に関し、非対称な遅延は、少なくとも1つの閾値と比較される。 (もっと読む)

インターホンシステム

【課題】複数の子機及び親機が分岐器を介して共通の伝送線路に分岐接続されるシステム構成においても伝送効率を低下させずに衝突を回避して音声を多重伝送することを可能とする。

【解決手段】通話を開始するイベントが発生したら中継装置Rの信号処理部44が送信開始コマンドを送信して複数の子機S1,S2及び複数の親機M1,M2にそれぞれ順番に送信権を与える。故に、複数の子機S1,S2及び複数の親機M1,M2から送信されるパケットの衝突を回避しつつ子機S1と親機M1並びに子機S2と親機M2の複数組が同時に通話することができる。その結果、複数の子機S1,S2及び親機M1,M2が分岐器Bを介して共通の伝送線路Ls1,Ls2に分岐接続されるシステム構成においても伝送効率を低下させずに衝突を回避して音声と映像を多重伝送することが可能となる。

(もっと読む)

パルスエッジシフトの復調方法および復調器

【課題】新たな変調方式を提供する。

【解決手段】可変遅延回路312は、所定の周波数のキャリア信号SCを遅延させて被変調信号SESMを出力する。遅延設定部314は、可変遅延回路312の遅延時間を、変調すべきデータ信号SBBに応じて設定する。遅延設定部314は、データ信号SBBの各シンボルAを、キャリア信号SCのポジティブエッジおよびネガティブエッジのいずれかに割り当て、キャリア信号SCのあるポジティブエッジが可変遅延回路312を通過するタイミングにおける可変遅延回路312の遅延時間を、当該ポジティブエッジに割り当てられたデータ信号SBBのシンボル値Aに応じて設定する。またキャリア信号SCのあるネガティブエッジが可変遅延回路312を通過するタイミングにおける可変遅延回路312の遅延時間を、当該ネガティブエッジに割り当てられたデータ信号SBBのシンボル値に応じて設定する。

(もっと読む)

集積回路装置およびその製造方法

【課題】磁気結合を用いて高速応答性を向上しながら耐ノイズ性能を向上できるようにする。

【解決手段】入力信号となるデジタル信号が「L」→「H」または「H」→「L」となるタイミングから所定期間tb以外にコイル8の誘起電圧のデジタル信号の検出出力変化がある場合(15)には、異常信号として診断信号電圧を入力信号補正回路に出力し、この場合には、入力信号補正回路は補正用のパルス信号Yを入力信号に重畳してコイル6に印加する。すると、出力端子OUTに出力されるデジタル信号が補正されるようになり、正常なデジタル信号を出力端子OUTから出力できる。

(もっと読む)

情報処理装置、信号伝送回路及び信号伝送方法

【課題】 差動信号の位相差(遅延)を検出する回路が差動信号の伝送路に接続されていると、伝送路への付加容量が増大し、差動信号の波形劣化が大きくなるという問題がある。

【解決手段】 上記課題を解決するため、本発明は、受信回路に信号を送信する送信回路を含み、送信回路は、第1の周期でハイレベルとローレベルを繰り返す差動信号を、遅延量を変化させて受信回路に送信する信号送出部と、差動信号の差動電位差が基準値以上である間における、第1の周期の整数倍の時間間隔との差分が所定の時間間隔となる第2の周期の標本化信号による差動信号の標本化回数と、所定の時間間隔とにより、差動信号の差動電位差が基準値以上となっている期間を示すレベル確定期間を遅延量の変化に応じて算出する算出部と、差動信号の遅延量の変化に対応した前記レベル確定期間のそれぞれのうちで最も大きいものを検出する検出部とを含むことを特徴とする。

(もっと読む)

1 - 20 / 35

[ Back to top ]