Fターム[5K047AA12]の内容

デジタル伝送方式における同期 (12,489) | 目的、効果 (2,701) | 信頼性向上 (599) | 誤動作防止 (174)

Fターム[5K047AA12]に分類される特許

1 - 20 / 174

ネットワーク接続装置、通信システム及び通信方法

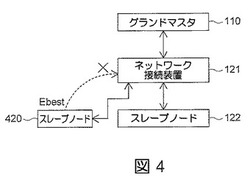

【課題】通信ネットワークにおいて、ネットワーク接続装置は、グランドマスタのタイミング情報を受け入れて、スレーブノードとタイミング同期するように要求することにより、安全なタイミング同期を提供する。

【解決手段】グランドマスタ110及びネットワーク接続装置121は、グランドマスタ110とネットワーク接続装置121との間のマスタ−スレーブ関係を決定するためのベスト・マスタ・クロック(BMC)アルゴリズムをサポートし、少なくとも1つのスレーブノード122がBMCアルゴリズムを支持しないときは、ネットワーク接続装置121は前記少なくとも1つのスレーブノード122を、BMCアルゴリズムを用いないで強制的にスレーブとする。

(もっと読む)

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

シリアル・ストリームにおける堅牢な制御及び描写方法

【課題】シリアル・ストリームにおける堅牢な制御及び描写方法を提供する。

【解決手段】{k1‐k2‐k2‐k1}で示される形態をとるコントロール記号は、mビットのデータ・ワードを含むシリアル・ストリーム内に挿入される。k1およびk2は、それぞれ、mビットのデータ・ワードとは異なるあらかじめ定義されたmビットのコントロール・ワードである。k1とk2の間におけるハミング距離は、少なくとも2である。この種のコントロール記号は、当該記号または当該記号の直前または直後に続くデータ・ワード内に1ビット誤りが存在する際、堅牢に検出され得る。mビットのワードは、8B/10Bエンコードされたデータ、または定められたコントロール・ワードでもよい。コントロール記号は、データの描写、ストリームの同期、送信機/受信機の同期、またはそのほかの制御の合図を行うために使用できる。

(もっと読む)

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

同期化回路及び同期化方法

【課題】短時間に受信側クロックで位相を同期化すること。

【解決手段】受信したデータを同期化する同期化回路10は、位相差判定回路15と第1のFF11と第2のFF12とを有する。位相差判定回路15は、同期化回路10と接続された他装置から受信したデータを同期化回路の内部クロックの位相で受付けた場合、データを安定に捉えられるか否かを判定する。第1のFF11は、位相差判定回路15によってデータを内部クロックの位相で安定に捉えられると判定された場合、データと内部クロックとを受付け、データを内部クロックの位相で捉えて同期化する。第2のFF12は、位相差判定回路15によってデータを内部クロックの位相で安定に捉えられないと判定された場合、データと位相が反転された内部クロックとを受付け、データを位相が反転された内部クロックの位相で捉えて同期化する。

(もっと読む)

受信装置、受信方法、およびプログラム

【課題】データの欠損によるタイミングの変化に迅速に対応することができるようにする。

【解決手段】受信装置は、同期回路14と等化回路15を備える。同期回路14の検出器33は、受信信号のデータの欠損を検出し、検出結果を等化回路15の等化器42に供給する。等化器42は、データの欠損の検出結果に基づいて、データの欠損量だけ処理タイミングを調整する。この開示の技術は、例えば、データの欠損が生じ得る受信信号を受信する受信装置に適用できる。

(もっと読む)

データ受信装置及びデータ送信装置

【課題】後段の誤動作を抑制するデータ受信装置及びデータ送信装置を提供する。

【解決手段】物理層回路とMAC層との間でデータが非同期転送される。データは1バイト単位で処理される。検出回路は変換モジュールが送信したデータの第1のパケットと第2のパケットとの間隔が規格最小値より短いことを検出する。第2のパケットは第1のパケットに続く。無効化回路は間隔が規格最小値より短いことが検出回路に検出された場合に第2のパケットの先頭から1バイトの自然数倍分のデータを無効化する。無効化は、間隔が規格最小値以上となるように行われる。

(もっと読む)

光送受信システム及び光受信装置

【課題】本願発明は、伝送路でビットエラーが生じても、フレーム同期はずれ状態に移行しにくいフレーム同期技術を提供することを目的とする。

【解決手段】上記課題を解決するために、本願発明では、受信した光信号を電気信号に変換した後、電気信号のエラー訂正をし、フレーム同期が確立された後は、エラー訂正された電気信号の中から、許容値を超えたビットエラーを有する同期ワードの連続をカウントして規定数に達したときにフレーム同期はずれと判定する。

(もっと読む)

データ受信装置、データ受信方法及びプログラム

【課題】トレーニング中の初期化シンボルの一部が破損していた場合であっても、受信データを正常にデコードする。

【解決手段】受信装置は、初期化信号を生成する初期化信号生成部9と、初期化信号により初期化されるデスクランブラにより受信データをデスクランブルするデスクランブル回路10とを有する。受信データは、高速シリアル通信の接続を確立するための、1以上のTSnオーダーセットを含むトレーニング用データセットを有し、TSnオーダーセットは、1以上のCOMシンボルと1以上のCOMシンボル以外のデータとからなる。初期化信号生成部9は、トレーニング用データセットに含まれる最終のTSnオーダーセットを構成するCOMシンボルのうち少なくとも最終のCOMシンボルがデスクランブル回路10に入力される初期化最終タイミングでデスクランブル回路10を初期化する初期化信号を生成する。

(もっと読む)

位相調整装置およびカメラ

【課題】 より簡易な構成で、データとクロックとの位相の関係を適切に調整するための手段を提供する。

【解決手段】 位相調整装置は、第1データ取得部と、第2データ取得部と、判定部と、位相調整部とを備える。第1データ取得部は、入力されるシリアル転送データの基準位相での第1出力と、第1出力に対して第1遅延量による位相差を付与した第2出力とをそれぞれ取得する。第2データ取得部は、第1遅延量よりも大きな第2遅延量による位相差を第1出力に対して付与した第3出力と、第3出力に対して第1遅延量による位相差を付与した第4出力とをそれぞれ取得する。判定部は、第1データ取得部および第2データ取得部の各出力について、シリアル転送データに含まれる検出対象のデータ列が検出できたか否かをそれぞれ判定する。位相調整部は、判定部での判定結果に基づいて、出力されるシリアル転送データに付与する遅延量を調整する。

(もっと読む)

情報受信制御装置、情報受信制御方法、情報受信制御プログラムおよび記録媒体

【課題】調歩同期式のシリアル通信における通信データのサンプリングタイミングを簡単な回路構成によって制御することで通信データ単位でのサンプリング誤差の累積を防止し、通信データの受信エラーの発生を抑止することができるようにした情報受信制御装置、情報受信制御方法、情報受信制御プログラムおよび記録媒体を提供する。

【解決手段】調歩同期式のシリアル通信に用いられるビット単位の通信データの受信の際に、「基準クロックを分周したカウンタークロック」のカウンタークロック数に対する、「基準クロックから算出される分周値をもとにハード特性を考慮した特性分周値」を計算する。分周値と特性分周値を用いて算出されるそれぞれのカウンタークロックに基づく誤差からビット単位での誤差量を算出し、その誤差量をもとにカウンタークロック数の計数を行う際の初期値を決定する。

(もっと読む)

データ受信装置、データ送信装置、制御方法

【課題】 データ受信装置がデータ送信装置から受信するデータと、データ受信装置がデータ送信装置へ出力するクロックとの間で1サイクル以上の遅延がある場合、データ受信装置がデータ送信装置から供給されるデータを取りこぼしてしまう可能性がある。

【解決手段】 データ送信装置へコマンドを送信する際に、コマンドの送信終了タイミングと、送信装置からの前記コマンドに対応するデータの受信開始タイミングとの間のサイクル数をカウントする。

(もっと読む)

無線装置

【課題】無線伝搬路状態に応じて最適なフレームタイミングの検出動作を実行する。

【解決手段】無線装置2は,受信信号IQと受信信号IQの無線フレームに含まれる同期パターンのレプリカとの相関値を示す相関値プロファイルを求め,平均化した相関値プロファイルを平均化し,相関値プロファイルに基づき,フレーム同期タイミングを検出する検出回路50を有し,検出回路50は,ゲインに応じて,平均化する相関値プロファイルの数を増減する。

(もっと読む)

ノードシステムおよび監視ノード

【課題】クロック周波数に対応するサイクル長分布を求め、同期外れを抑制すること。

【解決手段】監視ノードが、サイクルマイクロチック数を増加または減少させながらフレームを送出し、第1および第2のノードが送出するフレームの受信が停止した時のサイクルマイクロチック数からレート補正限界値を減じまたは加えて、還元サイクルマイクロチック数を求める。

(もっと読む)

シリアル通信装置及びその制御方法

【課題】内部回路との間で所定の同期クロックを用いて通信を行う送受信回路と、入力される基準クロックに基づいて上記同期クロックを発生するPLL回路とを備えたインターフェース回路を備えたシリアル通信装置において、インターフェース回路及び内部回路の誤動作を防止する

【解決手段】遅延回路5は、基準クロックREFCLKの周波数が100MHzで安定した後に発生されるリセット信号PERST#を、所定の遅延時間Δtだけ遅延させて内部リセット信号PERST2を発生し、リンクコントローラ31に出力する。PHY回路2は、リセット信号PERST#に応答してリセットされ、リンクコントローラ31は、内部リセット信号PERST2に応答してリセットされる。また、遅延時間Δtは、PLL回路23の回路仕様に基づいて予め計算されたロックアップ時間より長く設定される。

(もっと読む)

基地局制御装置、無線通信システム、およびタイミング補正方法

【課題】基地局制御装置から基地局へのフレームのタイミング補正における二重補正の発生を抑制する。

【解決手段】本発明の基地局制御装置はデータ受信部とデータ送信部と伝送遅延算出部とガードタイム算出/判定部を有している。データ受信部は、基地局装置からのデータを受信する。データ送信部は、データ受信部で受信される基地局装置からのタイミング補正の要求に応じて補正したタイミングで、基地局装置にデータを送信する。伝送遅延算出部は、自装置から基地局装置までの伝送遅延時間と基地局装置から自装置までの伝送遅延時間とを含む往復伝送遅延時間を算出する。ガードタイム算出/判定部は、往復伝送遅延時間と、基地局装置から要求されたタイミング補正におけるタイミング補正量とに基づいてガードタイムを算出し、そのガードタイムの間に基地局装置から受信されるタイミング補正の要求を破棄する。

(もっと読む)

受信回路

【課題】 多相クロック信号を用いてデータを受信する受信回路において、多相クロック信号の位相歪みを抑制すること。

【解決手段】 本受信回路30は、位相コードに基づき、多相クロック入力信号から任意の位相の多相クロック出力信号を生成する位相インターポレータ40と、位相コードに変動を与える位相変動回路52と、位相コードの変動に対する多相クロック出力信号の変動を検出する位相検出回路46と、位相検出回路46の検出結果に基づき、位相インターポレータ40の位相歪みを推定する歪み推定回路52と、歪み推定回路52の推定結果に基づき、位相歪みを補正する補正回路52と、を備える。

(もっと読む)

無線通信装置

【課題】誤同期の直後であっても正規の無線信号を正しく受信することができる無線通信装置を提供する。

【解決手段】演算処理ブロック1の命令デコード部29が、同期検出部27がフレーム同期検出信号の出力を開始してから当該フレーム同期検出信号の出力を停止するまでの間に受信データ出力命令を受け取らなかった場合、同期検出部27が次回のフレーム同期検出信号の出力を開始するまでの間に演算処理ブロック1の中央演算処理部10から受信データ出力命令が出力されても、受信データバッファ25に蓄積されている受信データを出力させないようにしている。その結果、誤同期の直後であっても正規の無線信号を正しく受信することができる。

(もっと読む)

通信回路及びそれを用いた車両用通信装置

【課題】ノイズの影響を受けにくく、情報の伝送開始が確実に認識されて短時間に通信をすることができる通信回路、及びそれを用いた車両用通信装置を提供する。

【解決手段】通信回路の送信部1は、スタートビットsb及び情報ビット列ibを順次送出するビット列生成回路31と、スタートビットにより第1搬送波を変調して第1高周波信号r1を生成する第1変調回路41と、情報ビット列により第2搬送波を変調して第2高周波信号r2を生成する第2変調回路43と、第1高周波信号及び第2高周波信号を送信する送信回路51とを備える。受信部2は、送信された信号を受信する受信回路61と、第1搬送波の信号を検波してスタートビットを復調する第1検波回路71と、第2搬送波の信号を検波して情報ビット列を復調する第2検波回路72と、スタートビットにより同期され、情報ビット列を読み取る検出回路81と、を備える。

(もっと読む)

データ受信回路

【課題】高速で高精度のデータ受信を可能にするデータ受信回路の提供を図る。

【解決手段】入力データDataを受け取って遅延した遅延データを出力する可変遅延回路2と、データ取り込みクロックCLK1に従って前記遅延データを取得するデータ取得用フリップフロップ31と、クロック信号CLKを受け取ってフラクショナルクロックを出力するフラクショナルPLL回路1と、前記フラクショナルクロックCLK2に従って前記遅延データの位相検出を行う位相検出用フリップフロップ32と、該位相検出用フリップフロップの出力信号および前記データ取得用フリップフロップの出力信号から前記可変遅延回路における遅延量を制御して位相調整を行う位相調整回路4と、を有する。

(もっと読む)

1 - 20 / 174

[ Back to top ]