Fターム[5K047GG02]の内容

デジタル伝送方式における同期 (12,489) | 網同期;クロック、ビット同期 (2,470) | クロックの伝送 (1,938) | クロックの発生、供給 (183)

Fターム[5K047GG02]の下位に属するFターム

伝送信号に対応させて別ラインで供給 (123)

Fターム[5K047GG02]に分類される特許

41 - 60 / 60

非同期送受信回路

【課題】CPU等の負荷を軽減することができ、かつ緊急処理に対応可能なUARTを提供する。

【解決手段】開始ビット検出部1、タイミング制御部2、シフトレジスタ3及び終了ビット検出部4による直列・並列変換手段で、調歩同期方式の入力信号INを文字単位の並列データに変換し、この並列データをFIFOバッファ6に格納すると共に、特殊コード検出器8で予め設定した特殊符号であるか否かを判定する。特殊符号の場合、検出信号DETに基づいて、割り込み制御部7AからCPUへ割り込み要求信号INTが出力される。CPUは、識別レジスタ7aを参照し、メッセージの区切りであれば読み出し信号RDでFIFOバッファ6の並列データを読み出す。また、緊急処理の要求であれば直ちに緊急処理を行うことができる。

(もっと読む)

局側光網終端装置、加入者側光網終端装置、および光通信システム

【課題】既存の光通信システムでのサービス提供をそのまま継続させながら、他の通信速度のサービスをも低コストで実現可能とする。

【解決手段】OLTは、プリアンブルパターンの送出時間を通信速度に応じて変更する。すなわち、プリアンブルパターンの送出時間を通信速度に応じたものとすることにより、それぞれの通信速度に最適な長さのプリアンブルパターンを送出する。こうして異なる通信速度の光信号を同一の光波長により送受信できるようにすることにより、光信号の送受信を行うための光モジュールを1つで済ませることができる。

(もっと読む)

半導体集積回路

【課題】クロック信号のスペクトラムを拡散することによって電磁放射ノイズを低減する方式を採用した半導体集積回路において、電磁放射ノイズのピーク成分をさらに効果的に低減する。

【解決手段】この半導体集積回路は、クロック信号を周波数変調することによって電磁放射ノイズを低減する半導体集積回路であって、所定の周波数を有するクロック信号を周波数変調することにより、第1の変調幅を有する第1の変調クロック信号を生成する第1の変調回路10と、第1の変調クロック信号をさらに周波数変調することにより、第1の変調幅よりも大きい第2の変調幅を有する第2の変調クロック信号を生成する第2の変調回路20とを具備する。

(もっと読む)

シリアルデータ転送システムおよびシリアルデータ転送方法

【課題】 シリアル転送においてスレーブデバイスの転送速度を考慮不要とする。

【解決手段】 マスタデバイス10とスレーブデバイス21〜2Nの間が各1本の転送クロックCとシリアルデータ信号Dとクロックウエイト信号Wで接続される。転送クロックはマスタデバイスから送出され各スレーブデバイスに送出され、シリアルデータ信号はマスタデバイスと各スレーブデバイスとの間で転送クロックに同期してビットシリアルにデータを送受信する。クロックウエイト信号w1〜wNは各スレーブデバイスにおいて次の転送準備が完了していない場合に転送クロックの反転時を延長させるためにオープンドレイン接続で送出され、プルアップ抵抗Rに接続されて一つのクロックウエイト信号Wに集約されマスタデバイスに入力する。

(もっと読む)

非同期クロック利用の分散処理同期システム、マスターシステム及びクロック同期制御方法

【課題】 分散処理システムにおいて、システム全体にクロック専用線によりクロック配信を行うと、クロック配線数が増大する。

【解決手段】 マスターシステムが同期用フレーム送信要求をクライアントシステムに同時に配信し、クライアントシステムは同期用フレーム送信要求に従い、マスターシステムへ送信する同期用フレーム長を可変とすることによりクロックずれが吸収し、システム全体で同期確立を可能とする。また、同期用フレーム送信要求及び、同期用フレームの転送に、データの送受信制御を行う制御線を用いることにより、クロック専用線を配置する必要性を無くす。

(もっと読む)

電子装置、フレーム同期の方法、および移動体装置

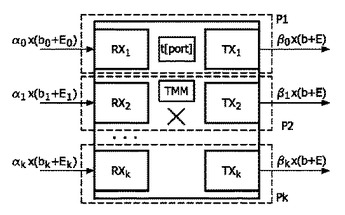

電子装置には、各々がいくつかのタイム・スロット(SL)に分割されているフレーム(FR)に基づいて、少なくとも一次データおよび二次データ(ISOC,BE)を通信するための複数の機能ユニット(1〜10)と、少なくとも1つの第1のクロック・ドメインのうちの複数の機能ユニット(1〜10)のうちの1つから少なくとも一次データおよび二次データ(ISOC,BE)を受信するための関連する受信機ポート・ユニット(RX1,RX2,…,RXk)、および少なくとも1つの第2のクロック・ドメインのうちの複数の機能ユニット(1〜10)のうちの別の1つに少なくとも一次データおよび二次データ(ISOC,BE)を送信するための関連する送信機ポート・ユニット(TX1,TX2,…,TXk)を有する少なくとも1つのポート(P1,P2,…,Pk)を有する、機能ユニット(1〜10)を結合するための少なくとも1つのネットワーク・ノード(S1〜S4)が設けられる。少なくとも1つの第2のクロック・ドメインは、少なくとも1つの第1のクロック・ドメインと異なる。時間表示レジスタ(t[port])は、少なくとも1つのポート(P1,P2,…,Pk)のうちの1つに関連する受信機ポート・ユニット(RX1,RX2,…,RXk)を経由して受信されているフレーム、および少なくとも1つのポート(P1,P2,…,Pk)のうちの1つに関連する送信機ポート・ユニット(TX1,TX2,…,TXk)を経由して送信されているフレームの相対的な時間位置に関する情報を記憶するために提供され、時間表示レジスタ(t[port])は少なくとも1つのポート(P1,P2,…,Pk)のうちの1つに関連する受信機ポート・ユニット(RX1,RX2,…,RXk)を経由して受信されている少なくとも一次データおよび/または二次データ(ISOC,BE)に従って更新される。タイマ管理手段(TMM)は少なくとも1つの第1のクロック・ドメインのうちの少なくとも1つのポート(P1,P2,…,Pk)のうちの1つに関連する受信機ポート(RX1,RX2,…,RXk)を経由して受信された一次データおよび二次データ(ISOC,BE)を少なくとも監視するため、および時間表示レジスタの値が予定の閾値を超える場合、少なくとも1つの第2のクロック・ドメインのうちの少なくとも1つのポート(P1,P2,…,Pk)のうちの1つに関連する送信機ポート・ユニット(TX1,TX2,…,TXk)を経由して、少なくとも一次データ(ISOC)の伝送を休止するために提供される。  (もっと読む)

(もっと読む)

ネットワークを介した時間同期化システムおよび方法

【課題】ネットワークを介した時間同期化の手法を提案する。

【解決手段】ネットワーク内の受信側装置13に、同期化可能なクロックを備え、同じ瞬間(または比較的同じ瞬間)に該クロックのすべてによって受信される「インパルス」信号を定期的に送る。インパルス信号は、すべてのクロックにほぼ同時に到達する。送信側装置は、該同期化インパルス信号を受信すると、該送信側装置のエポックタイムスタンプを運ぶデータのパケットを、受信側装置に送信する。該データパケットは、ネットワークを介して該受信側装置へと進み、該受信側装置は、該タイムスタンプを使用して、受信側装置のエポックタイムと送信側装置のエポックタイムとの間の差を計算する。

(もっと読む)

パラレル−シリアル変換回路およびパラレル−シリアル変換方法

【課題】 低周波数のクロックで高速なパラレル−シリアル変換が可能なパラレル−シリアル変換回路およびパラレル−シリアル変換方法を提供することを目的とする。

【解決手段】nビットのパラレルデータをシリアルデータに変換するパラレル−シリアル変換回路であって、パラレルデータを入力する入力部2と、パラレルデータの入力周波数と同じ周波数で、パラレルデータの周期をn等分した位相差を持つn相のデータクロック群を生成するクロック生成部1と、パラレルデータの各ビットをn相のデータクロック群の各位相に同期させ、同期データ群として出力する同期部3と、同期データ群からデータクロック群の状態に対応する同期データを選択し、シリアルデータとして出力する信号選択部4とを備えることにより上記課題を解決する。

(もっと読む)

ネットワーク上のマルチチャネルスピーカの同期

サーバが,あるオーディオ信号に対応する少なくとも1つのオーディオデータストリームをネットワーク内の2以上のスピーカに配信するようになっている。各スピーカは,前記オーディオデータから前記オーディオ信号を再生するためにそれぞれクロックを有する。各スピーカについて,前記サーバは前記スピーカクロックの実時間レートに対する相対レートを測定し,あるスピーカに与えられる各データストリームについて,前記サーバは前記相対レートによって変更すべき前記オーディオ信号のそれぞれのサンプルを,それぞれの相対レートから決定する。前記ストリームはそれによって変更され,ネットワーク内に送信される。  (もっと読む)

(もっと読む)

クロック生成装置およびクロック生成方法

【課題】デジタル放送受信時は受信したデータストリームの基準時刻情報に随従したシステムクロックを正確に生成し、ディスク再生時には低ジッター、高ピュリティでかつ周波数変動の極小なシステムクロックを提供する。

【解決手段】データストリーム(MPEG2−TS)からの時刻基準情報(PCR)に同期した同期クロック(CK1)を生成する第1PLL回路(PLL1)と、固定クロック(CK3)を生成する発振器(VXO)と、クロック切替信号を出力する制御部(25)と、前記クロック切替信号によって、前記同期クロックと前記固定クロックを切り替え選択し、選択されたクロックをシステムクロックとして出力するクロック切替部(21g)とを備える。

(もっと読む)

周波数補正機能付きクロック供給装置

【課題】基準クロックが断たれても、VCOのクロック周波数の経年変化特性を補正して高精度の自走クロックを実現出来る周波数補正機能付きクロック供給装置を提供する。

【解決手段】基準クロックが取得出来ている時、CPU106は位相比較器2より出力される位相誤差情報より、予め計時手段110で通知される周期毎にVCO104のクロック周波数の経年変化特性による位相誤差情報を予測して算出し、その位相誤差を補正する制御電圧値を自走DA設定メモリ109に記憶する。基準クロックが断たれると、CPU106は位相比較器102の出力である位相誤差情報を参照せず、代わりに計時手段110で通知される周期毎に、対応する位相誤差情報を補正する制御電圧値を自走DA設定メモリ109より読み出してDA変換器105に設定することで、VCO104のクロック周波数の経年変化特性を補正して高精度の自走クロックを実現する事が可能である。

(もっと読む)

データ伝送

【課題】通信リンクを介して、送信ノードと受信ノードとの間で通信を行うデータ通信システムの提供。

【解決手段】送信ノードは、通信リンクの各伝送パスを介して、少なくとも2つのストリーミングデータ信号からのデータを送信するデータ送信手段と、通信リンクを介して、少なくとも2つのベースクロック信号のタイミング情報を送信するタイミング送信手段と、各伝送パスと、対応するベースクロック信号の1つとの間の各関係を特定し、伝送パスをいずれかのベースクロック信号に関連付けるコンフィグレーションデータを送信する。受信ノードは、通信リンクの伝送パスからデータを受信するデータ受信手段と、コンフィグレーションデータに応じてベースクロック信号のタイミング情報を処理し、各伝送パスに対応する各サンプリングクロックを生成する処理手段と、サンプリングクロックを各伝送パスからのデータに関連付け、ストリーミングデータ信号を再生する。

(もっと読む)

シリアル信号送信装置、シリアル信号受信装置、シリアル伝送装置、シリアル伝送方法

【課題】 信号線数を削減するとともに、ノイズや静電気等の外乱に対する信頼性の高いシリアル伝送装置を提供する。

【解決手段】 データ信号またはコマンド信号の送信側回路2から受信側回路3への伝送を開始する前に、データ信号およびコマンド信号を伝送する信号線14Pおよび14Nを用いて、データ信号およびコマンド信号と同じデータ長で、かつ、スタートビットとストップビットとが異なる値からなる同期パターンを伝送する。そして、受信側回路3では、PLL12が、出力信号PLL_OUTの位相を、受信器10Rによって受信した同期パターンに基づいて制御することにより、出力信号PLL_OUTの位相を上記データ信号およびコマンド信号の位相に同期させる。

(もっと読む)

時刻同期方法、通信装置および時刻同期システム

【課題】 時刻同期信号を受信するために長い時間待機する必要なく、そのため消費電力量を低く抑える。

【解決手段】 リファレンス端末B11は、時刻同期周期T27で、送信時間T28の時刻同期信号S13を連続的に複数配信する。周辺端末B15〜B18は、最大でも時刻同期信号の送信時間T28の2倍の期間をセンシングすることで、時刻同期信号S13を受信する。リファレンス端末B11が時刻同期信号を連続配信する回数の最適値は、クロック精度や時刻同期周期T27、時刻同期信号S13の送信時間T28に基づいて決定する。

(もっと読む)

同期方法及びデジタル電子回路及び誘導結合によって給電される回路

【課題】低電力で所要面積が小さく、応用範囲の広い、同期方法と同期回路を提供する。

【解決手段】クロック信号発生しかつデジタルデータストリームに同期させる同期方法には、発振器を用いてクロック信号を発生すること、前記データストリームの一部において遷移を特定すること、および、該特定に応じて、制御回路を用いて前記発振器の状態を変更することにより、前記クロック信号の遷移を、前記データストリームにおいて特定された前記遷移と同期させることが含まれる。そして、前記クロック信号は、前記発振器が前記データのレートより高い周波数で動作している場合も低い周波数で動作している場合のいずれの場合にも、前記データストリームに同期させられる。

(もっと読む)

通信システム、基地局装置、基準クロック生成回路および同期方法

【課題】各装置間で有線回線を設けることなく、各装置間で同期を取るための技術を提供する。

【解決手段】AC電源の信号から周波数成分を抽出し(S404)、抽出された信号の周波数成分をあらかじめ定めた周波数に逓倍し(S405・406)、逓倍された信号の周波数を、基準クロックの周波数に分周する(S407)。分周された基準クロックの周波数の位相を補正し(S408)、補正された基準クロックを出力し(S409)、あらかじめ定めたフレームの同期処理を行う(S410)。

(もっと読む)

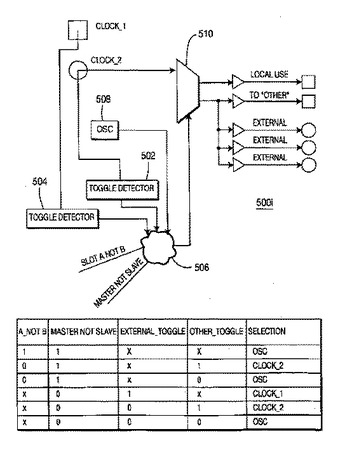

非同期信号をルーティングするためのシステムおよび方法

少なくとも1つの入力信号および少なくとも1つの出力をルーティングするルータ(100)は、少なくとも1つの入力モジュール(4021〜402x)および少なくとも1つの出力モジュール(4041〜404y)からなる。入力モジュールおよび出力モジュールの各々は、部分的には、第1および第2のクロック信号が切り替わったかどうか、に基づいて、第1および第2のクロック信号、および発振器信号の中から、共通の出力クロック信号として選択するための少なくとも1つのクロック・セレクタ回路(5001〜500n)を備えている。クロック・セレクタ回路は、リダンダンシーを提供し、各モジュール内部の各要素にクロック信号を配信する。  (もっと読む)

(もっと読む)

種々のクロックレートを参照するコンピュータマザーボード用コンピュータチップセット

【課題】 コンピュータマザーボードを待ち時間なしで動作させることができ、コンピュータマザーボードのデータ処理効率を向上させる。

【解決手段】 第1、第2クロックレートを含むクロックレートを持つコンピュータマザーボードで使用される。第1および第2クロックレートは実質的に同期しており、一定の比率がある。コンピュータチップセットは、位相信号の集合を発生できる位相信号生成回路と、第1、第2クロックレートのうち入力信号が参照していない側を参照する出力信号を発生する信号変換論理回路をもつ。マルチプレクサは、第3クロック信号として利用されるべく、第1、第2クロックレートの一方を選択して出力する。

(もっと読む)

波長多重光送信装置および波長多重光伝送システム

【課題】伝送品質を劣化させること無しに伝送容量の増大を図る。

【解決手段】各波長の受信回路11〜1nと変調回路31〜3nとの間に同期用バッファ21〜2nを設ける。またクロック発生部5を設け、互いに位相同期したn個のクロックXを生成する。そして、各受信回路11〜1nからの送信データをそれぞれ同期用バッファ21〜2nに書き込み、これらのデータをクロックXでそれぞれ読み出すことにより、変調回路31〜3nに与えられる送信データの位相を相互に一致させる。

(もっと読む)

タイミング設定方式

【課題】物理的切替スイッチを使用することなく、バス中継器配下の複数の回路装置のアクセスタイミング及びアドレス範囲をフレキシブルに設定可能なタイミング設定方式を提供する。

【解決手段】プロセッサ(CPU)4からのソフトウエア命令にて、バス中継器1におけるアドレス範囲の設定を任意に行い、設定したアドレス範囲の独立したタイミング設定を行う。バス中継器1は、アドレス保持デコード回路2,タイミング調整回路3及び基本クロック回路6を有する。バス中継器1の配下には、複数の回路装置5a−5nを有する被コントロール装置群5が設けられている。

(もっと読む)

41 - 60 / 60

[ Back to top ]