Fターム[5K047GG08]の内容

デジタル伝送方式における同期 (12,489) | 網同期;クロック、ビット同期 (2,470) | クロックの伝送 (1,938) | クロックの受信 (1,715) | 伝送クロックよりクロックの再生 (446)

Fターム[5K047GG08]の下位に属するFターム

クロック位相調整 (261)

クロックの周波数同期 (116)

Fターム[5K047GG08]に分類される特許

1 - 20 / 69

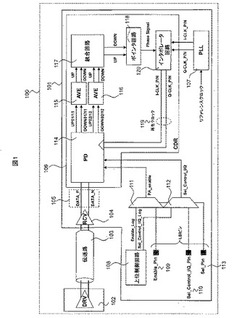

CDR回路、受信装置、および送受信システム

【課題】非線形位相比較器を用いたCDR回路、受信装置、および送受信システムの再生クロックの位相追従精度を向上させる。

【解決手段】CDR回路106、受信装置101、および送受信システム100は、受信データ105および再生クロック119が入力される非線形位相比較器の出力に、受信データに対する、再生クロックに対して位相差を有するクロックの遅れまたは進みに応じて重み付けをし、重み付けされた出力に基づいて再生クロックの位相を調整する。

(もっと読む)

網同期装置のシェルフ、網同期装置

【課題】 クロック断における不要な警報通知を遮断する。

【解決手段】

クロック信号の入力を受け付けるためのクロック入力受付部と、クロック信号を出力するためのクロック出力部と、前記クロック入力受付部がクロックを受け付けない場合にクロック断を検出するクロック断検出部と、前記クロック入力受付部を介してAIS信号を受け付けた場合にAIS信号を検出するAIS信号検出部と、AIS信号を生成するAIS信号生成部と、前記クロック断検出部がクロック断を検出した場合に、前記AIS信号検出部がAIS信号を検出していなければ、所定の警報通知を出力するアラーム制御部と、前記クロック断検出部がクロック断を検出した場合に、前記AIS信号生成部が生成したAIS信号を前記クロック出力部に出力する出力信号選択部と、を備えることを特徴とする。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

信号配線システム及びジッタ抑制回路

【課題】従来は、信号配線のジッタ量を削減しつつ、回路規模の増大化を抑制することが難しかった。

【解決手段】差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部からの前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システム。

(もっと読む)

信号処理装置、及び信号処理方法

【課題】簡易な回路構成で入出力クロックの誤差を吸収すること。

【解決手段】所定数のデータと、第1のクロックに同期し、データが有効な区間でアクティブな状態をとる第1のイネーブル信号と、が入力される入力部と、第1のクロックよりも高速な第2のクロックを基準に、第1のイネーブル信号が非アクティブな状態をとる区間のクロック数をカウントするカウント部と、第2のクロックを基準に、所定数に等しいクロック数分だけ第2のイネーブル信号をアクティブな状態にし、カウント部によりカウントされたクロック数分だけ第2のイネーブル信号を非アクティブな状態にするイネーブル信号制御部と、第2のイネーブル信号を出力するイネーブル信号出力部と、第2のイネーブル信号がアクティブな状態をとる区間に、第2のクロックに同期して所定数のデータを出力するデータ出力部と、を備える信号処理装置が提供される。

(もっと読む)

オーバーサンプリング回路及びそれを用いたシリアル通信装置及びシリアル通信方法

【課題】主な目的は、消費電流を減少させることにあり、副次的な目的は、オーバーサンプリング間隔を切り替えることができるオーバーサンプリング回路及びそれを用いたシリアル通信装置及びシリアル通信方法を提供する。

【解決手段】シリアルデータを所定時間だけ遅延させた多相シリアルデータを生成する生成部と、その多相シリアルデータを多相クロックでオーバーサンプリングするオーバーサンプリング部と、を備えた。

(もっと読む)

送信装置、受信装置及び伝送システム

【課題】簡易な構成によりクロックリカバリを実現し、伝送時のオーバーヘッドを削減する。

【解決手段】送信装置1−1は、制御用メタデータを生成し、制御用メタデータを定期的に受信装置2−1へ送信する。また、送信装置1−1は、コンポーネントの符号化を行い、自身のコンポーネントのクロックを用いてPCR、DTS及びCTSを生成し、または、他のコンポーネントのクロックを用いてDTS及びCTSを生成し、コンポーネントの符号データ等を受信装置2−1へ送信する。受信装置2−1は、制御用メタデータを定期的に受信すると共に、コンポーネントの符号データ等を受信する。そして、受信装置2−1は、制御用メタデータに従って、受信したPCRに基づいて自身のコンポーネントのクロックに対しクロックリカバリを行い、復号等を行う。また、受信装置2−1は、他のコンポーネントのクロックを流用して復号等を行う。

(もっと読む)

クロック再生装置、クロック再生方法および制御プログラム

【課題】アダプティブクロック再生法を用いて同期を取っている時にパケット固定遅延を検出した場合でも、安定して送信端末と受信端末との同期を取る。

【解決手段】クロック再生装置10は、クロック出力手段50から受信したクロックに同期させてバッファ60からパケットを出力させると共に、バッファ60の蓄積量を計測して出力するバッファ制御手段20と、遅延の有無を監視し、遅延を検出した場合、遅延量を算出して出力する遅延検出手段30と、バッファ制御手段20から受信した蓄積量に基づいてクロック制御値を生成して出力すると共に、遅延検出手段30から遅延量を受信した場合、該遅延量に対応する期間、所定のクロック制御値を出力するクロック制御手段40と、クロック制御手段40から受信したクロック制御値に基づいてクロックを生成して出力するクロック出力手段50と、を備える。

(もっと読む)

送信装置、受信装置および送受信システム

【課題】回路規模の増大を抑制しつつEMIノイズの低減を図ることができる送信装置を提供する。

【解決手段】送信装置10Aは、送信データ生成部11および出力バッファ部12Aを備える。送信データ生成部11は、受信装置へ送出すべきデータdata1およびクロックclock1を生成し、これらを出力バッファ部12Aへ出力する。出力バッファ部12Aは、データ送信部13およびクロック送信部14Aを含む。クロック送信部14Aは、間欠的に位相シフトを与えられたクロックを生成して送出する。データ送信部13は、クロック送信部14Aにより送出されるクロックに同期してデータを送出する。

(もっと読む)

PONシステムの局側装置、クロックデータ再生回路及びクロック再生方法

【課題】 想定外の伝送レートの入力信号が入力されても、次の入力信号に対するクロックとデータの再生を適切かつ高速に行えるようにする。

【解決手段】 本発明は、位相ロックループと周波数ロックループのうちのいずれか一方に切り替え可能なデュアルループ方式のクロックデータ再生回路50に関する。この再生回路50は、各ループのうちのいずれか一方を選択的に動作させるセレクタ53と、各ループにおいてそれぞれ制御電圧を発生させ、周波数ロックループの動作中に制御電圧をいったん入力信号の到来前の中立状態に戻す電圧発生回路54と、を備える。

(もっと読む)

データ受信回路

【課題】高速で高精度のデータ受信を可能にするデータ受信回路の提供を図る。

【解決手段】入力データDataを受け取って遅延した遅延データを出力する可変遅延回路2と、データ取り込みクロックCLK1に従って前記遅延データを取得するデータ取得用フリップフロップ31と、クロック信号CLKを受け取ってフラクショナルクロックを出力するフラクショナルPLL回路1と、前記フラクショナルクロックCLK2に従って前記遅延データの位相検出を行う位相検出用フリップフロップ32と、該位相検出用フリップフロップの出力信号および前記データ取得用フリップフロップの出力信号から前記可変遅延回路における遅延量を制御して位相調整を行う位相調整回路4と、を有する。

(もっと読む)

基準クロック復元方法、パケット多重装置、パケット分離装置及び伝送システム

【課題】一つの基準クロックを有する送信側から配信された複数の種類の信号を受信側で受信する際に、単一のクロック復元部で受信側の複数の復号器が送信側の各符号器のSTCと同期可能である基準クロック復元方法、パケット多重装置、パケット分離装置及び伝送システムを提供することを目的とする。

【解決手段】本発明に係る基準クロック復元方法は、伝送フレームにおけるIFGの挿抜により、装置間の処理クロックの違いを吸収しようとするIP網において、パケット分離装置251のパケット揺らぎ検出部32により得たIFGの挿抜情報に基づき、パケット分離装置251内のクロック周波数を変更することによって、パケット多重装置201の処理クロックとパケット分離装置251の処理クロックを同期させることとした。

(もっと読む)

ビデオ・エンコーダおよびエンコーダからデコーダへのタイミングを同期させる方法

【課題】 多重化およびトランスポート・パケット化装置の同期をとる。

【解決手段】 圧縮された多層のビデオ信号のトランスポート層または多重層のような、中間層の信号の同期を発生させる装置は、システムの符号化端末において、システム・クロック22に応答する計数器23を含んでおり、計数値は処理装置13により所定のスケジュールに従ってトランスポート層における信号に詰め込まれる。システムの受信端末において、逆トランスポート処理装置18は、補助トランスポート・データからのPCR、および制御信号をシステム・クロック発生器27に供給する。クロック発生器27はこれらの信号に応答し、少なくとも逆トランスポート処理装置18の動作に同期するシステム・クロック信号を発生する。このシステム・クロック信号は、処理要素のタイミングを制御する為に、受像機システム制御装置26に供給される。

(もっと読む)

音響信号処理装置及び音響信号処理システム

【課題】 システムを複数の伝送路を接続した構成とする場合でも、クロック源を異なる伝送路のデバイスに変更したことに伴って生じる各伝送路における伝送不能時間を短縮できるようにする。

【解決手段】 ブリッジデバイスで接続された第1ネットワークと第2ネットワークとを含む音響信号処理システムにおいて、上記ブリッジデバイスが、上記第1ネットワークでスレーブとして、上記第2ネットワークでマスタとして動作し、上記第2ネットワークがリセットされた場合、その第2ネットワークにおいてスレーブとしての動作を開始し、その後、その第2ネットワークにおいて他のデバイスがマスタとして動作して送出した音声伝送フレームの継続的な受信を開始した場合に、上記第1ネットワークをリセットし、その第1ネットワークにおいてマスタとしての動作を開始する(S174)。

(もっと読む)

デジタルクロック再生器

サンプリング装置(110)は、変動する周期時間を有する入力クロック信号(CLKin)を受信し、入力クロック信号(CLKin)の平均周波数より実質的に高い周波数を有するサンプリングクロック信号(CLKsmpl)に基づいて、入力クロック信号(CLKin)をサンプリングする。サンプリング装置(110)は、入力クロック信号(CLKin)の各周期に対して、各周期長値(PL)を生成する。平均化装置(120)は、いくつかの周期長値(PL)をサンプリング装置(110)から受信し、それに基づき、前記数の周期長値(PL)に等しい周期数を含む平均化期間に渡って、入力クロック信号(CLKin)に対して平均周期時間を表す平均周期長値(PLavg)を生成する。出力装置(151)は、平均周期長値(PLavg)およびサンプリングクロック信号(CLKsmpl)に基づいて、安定した出力クロック信号(CLKout)を生成する。 (もっと読む)

シリアル及びパラレル通信のためのハイブリッドインターフェイス

本発明の実施形態は、一般に、シリアル及びパラレル通信用のハイブリッドインターフェイスに関する。方法の実施形態は、第2装置へのデータの送信又は第2装置からのデータの受信のため第1装置を初期化する段階と、第1装置のインターフェイスを第1の複数のピンを含むパラレルインターフェイスの第1モードに切り換える段階と、第1の複数のピンを介して第1モードでパラレルデータを送信又は受信する段階とを含む。本方法は、更に、第1装置のインターフェイスを、第2の複数のピンを含み且つ第1の複数のピン及び第2の複数のピンが共に重なり合うピンのセットを含むシリアルインターフェイスの第2モードに切り換える段階と、第2の複数のピンを介して第2モードでシリアルデータを送信又は受信する段階と、を含む。 (もっと読む)

CDR回路

【課題】MACからの制御信号なしでも瞬時に入力データとの同期を確立し、周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するVCO11と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10とVCO11との間に設けられた、所望のデータレート周波数の信号を通過させるバンドパスフィルタ40とを備える。

(もっと読む)

通信ネットワークのネットワーク要素

そのローカルクロックを基準クロック信号に同期するように構成された、通信ネットワーク用のネットワーク要素が開示される。ネットワーク要素は、内部同期トランスポートプロトコルをサポートするように構成された内部モジュールおよび内部モジュールに接続されたコネクタを備えるメインボードと、コネクタに取り外し可能に接続されるように構成されたプラグ着脱可能モジュールとを備える。プラグ着脱可能モジュールは、コネクタに接続されたときに、他のネットワーク要素と外部同期情報を交換し、外部同期情報は、内部同期トランスポートプロトコルとは異なる外部同期トランスポートプロトコルに従ってフォーマットされ、内部同期トランスポートプロトコルに従ってフォーマットされた内部同期情報を内部モジュールと交換し、内部同期トランスポートプロトコルと外部同期トランスポートプロトコルとをインターフェースするように構成される。  (もっと読む)

(もっと読む)

信号処理装置、信号伝送方法、及びデータ復元方法

【課題】簡易な制御により省電力化することが可能な信号処理装置を提供すること。

【解決手段】第1データから、周波数f1を有する第1クロックに同期した第1データ信号を生成する第1信号生成部と、第2データから、周波数f2=N*f1を有する第2クロックに同期し、かつ、第1クロックの1/2周期について振幅を合計した値が0となる第2データ信号を生成する第2信号生成部と、第1信号生成部により生成された第1データ信号と、第2信号生成部により生成された第2データ信号と、を加算して加算信号を生成する信号加算部と、信号加算部により生成された加算信号を送信する信号送信部と、第1信号生成部を常時動作させ、第2データを送信する場合に第2信号生成部を動作させ、第2データを送信しない場合には第2信号生成部の動作を停止させる制御回路と、を備える、信号処理装置が提供される。

(もっと読む)

データ処理装置及びデータ処理システム

【課題】信号受信から信号送信までのタイミング誤差を小さくする。

【解決手段】複数のデータ処理ノードが所定のトポロジで通信路に接続されたデータ処理システムにおいて、データ処理ノードのデータ処理装置は、受信信号に基づいて受信クロック信号を再生し、再生された受信クロック信号に同期して受信データ再生部(122)で受信信号から受信データを再生すると共に、再生された受信データに対する送信データを送信データ生成部(123)で生成し、送信部(125)で送信データから送信信号を生成して送信クロック信号に同期して通信路に送信する、通信機能を備える。データ処理ノードは更に、受信データ再生部による信号の受信から送信部による送信信号の送信までに許容される時間に対して処理時間が短いとき、その誤差時間を検出する検出部(124)を有する。送信部は検出部による誤差時間の経過を待って送信データの送信を開始する。

(もっと読む)

1 - 20 / 69

[ Back to top ]