Fターム[5K047GG09]の内容

デジタル伝送方式における同期 (12,489) | 網同期;クロック、ビット同期 (2,470) | クロックの伝送 (1,938) | クロックの受信 (1,715) | 伝送クロックよりクロックの再生 (446) | クロック位相調整 (261)

Fターム[5K047GG09]に分類される特許

1 - 20 / 261

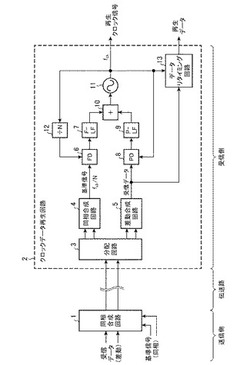

信号伝送システム、信号送信装置およびクロックデータ再生回路

【課題】良好な通信品質で、高速な位相同期ループを得る。

【解決手段】送信側は、一方が差動信号であり他方が同相信号であるデータ信号および基準信号を同相合成し、一対の伝送路を通じて伝送する同相合成回路1を備え、クロックデータ再生回路2は、同相合成回路1からの信号からデータ信号および基準信号を分離する信号分離手段(分配回路3、同相合成回路4および差動合成回路5)と、データ信号と位相が同期した再生クロック信号を生成する再生クロック信号生成手段(位相比較回路8、位相同期ループ用ループフィルタ9および電圧制御発振器11)と、再生クロック信号を分周し、当該分周した信号の周波数を基準信号の周波数に同期させる制御信号を生成し、当該制御信号により再生クロック信号の周波数を制御する再生クロック信号収束手段(周波数比較回路6、周波数同期ループ用ループフィルタ7、電圧制御発振器11およびN分周回路12)とを備えた。

(もっと読む)

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

CDR回路

【課題】誤ロック状態を検出し、この誤ロック状態から復帰することが可能なCDR回路を提供する。

【解決手段】CDR回路は、受信データ信号のデータをサンプルすべきデータサンプリングクロックとして第1のクロックと、受信データ信号のエッジをサンプルすべきエッジサンプリングクロックとして第2のクロックと、を生成し、且つ第1のクロックおよび第2のクロックの位相を調整するクロックリカバリ回路を備える。CDR回路は、第1のクロックで受信データ信号をサンプルした結果をデータサンプリング結果として出力し、第2のクロックで受信データ信号をサンプルした結果をエッジサンプリング結果として出力する位相検出回路を備える。CDR回路は、エッジサンプリング結果と、予め設定されたデータパターンとを比較し、エッジサンプリング結果とデータパターンとが一致した場合、誤ロック状態であると判断し、誤ロック状態検出信号を出力する結果比較回路と、を備える。

(もっと読む)

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

音声信号中継回路および音声信号中継方法

【課題】音声信号生成回路をより安定して動作させることが可能な音声信号中継回路等を提供すること。

【解決手段】音声信号中継回路100が、イネーブル信号入力部110と、搬送クロックを入力する搬送クロック入力部150と、サンプリングレートクロックを入力するサンプリングレートクロック入力部160と、音声信号を入力する音声信号入力部170と、搬送クロックを音声信号生成回路30に出力する搬送クロック出力部150と、サンプリングレートクロックを音声信号生成回路30に出力するサンプリングレートクロック出力部161と、音声信号を音声信号再生回路50に出力する音声信号出力部171と、擬似搬送クロックを生成する擬似搬送クロック生成部130と、擬似サンプリングレートクロックを生成する擬似サンプリングレートクロック生成部140を含んで構成される。

(もっと読む)

シンボル同期捕捉システム及びその方法

【解決課題】 低C/N環境下においても、また突発的な外乱を含みうる通信路環境下においても、安定して高速・高精度なシンボルの同期捕捉と同期追従を行うことを可能としたシンボル同期捕捉システムを得る。

【解決手段】 ディジタル変調された入力系列のシンボルクロックをPLL回路を用いて同期捕捉するシンボル同期捕捉システムにおいて、入力系列の特徴量系列を算出する手段と、最初のNサンプル(Nは2以上の整数)の特徴量系列をFFT処理する手段71と、このFFT処理結果に基づいてスペクトル最大成分を探索する手段72と、FFT処理結果に基づいて第N/2サンプルの時刻におけるシンボルクロックの位相推定をなす手段73とを含み、このスペクトル最大成分の周波数と位相推定値とをPPLL回路の初期設定値とする。

(もっと読む)

CDR回路、受信装置、および送受信システム

【課題】非線形位相比較器を用いたCDR回路、受信装置、および送受信システムの再生クロックの位相追従精度を向上させる。

【解決手段】CDR回路106、受信装置101、および送受信システム100は、受信データ105および再生クロック119が入力される非線形位相比較器の出力に、受信データに対する、再生クロックに対して位相差を有するクロックの遅れまたは進みに応じて重み付けをし、重み付けされた出力に基づいて再生クロックの位相を調整する。

(もっと読む)

同期化回路及び同期化方法

【課題】短時間に受信側クロックで位相を同期化すること。

【解決手段】受信したデータを同期化する同期化回路10は、位相差判定回路15と第1のFF11と第2のFF12とを有する。位相差判定回路15は、同期化回路10と接続された他装置から受信したデータを同期化回路の内部クロックの位相で受付けた場合、データを安定に捉えられるか否かを判定する。第1のFF11は、位相差判定回路15によってデータを内部クロックの位相で安定に捉えられると判定された場合、データと内部クロックとを受付け、データを内部クロックの位相で捉えて同期化する。第2のFF12は、位相差判定回路15によってデータを内部クロックの位相で安定に捉えられないと判定された場合、データと位相が反転された内部クロックとを受付け、データを位相が反転された内部クロックの位相で捉えて同期化する。

(もっと読む)

適応型受信システム、適応型送受信システム及び複数チャネル送受信システム

【課題】ロックポイント付近におけるサンプリングクロックの位相の調整と、イコライザ部の制御とを安定させ、ジッタトレランスを高める。

【解決手段】位相比較部は、サンプリングタイミングとサンプリングタイミングよりも第一の所定位相分前のタイミングとの間の第一区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LAG(n)を出力するとともに、サンプリングタイミングとサンプリングタイミングよりも第二の所定位相分後のタイミングとの間の第二区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LEAD(n)を出力する。判定部は、検出データパターンの各ビットに対応する位相比較信号LAG(n),LEAD(n)の出力パターンを所定の比較対象パターンと比較し、合致するか否かに基づいて、等化信号EQDATAの1ビットがサンプリングクロックCKの1周期よりも長いか短いかを判定する。

(もっと読む)

半導体装置、及び情報処理装置

【課題】

安定的な動作を確保できる半導体回路装置、及び情報処理装置を提供することを課題とする。

【解決手段】

半導体装置は、入力信号に遅延を与える遅延部と、前記遅延部から出力される出力信号の位相を検出する位相検出部と、前記位相検出部から出力される位相情報に基づき、前記出力信号の位相の安定動作範囲を設定する設定部と、前記安定動作範囲から位相が外れた前記出力信号の検出回数をカウントするカウンタと、前記遅延部の動作条件又は外的要因に応じて、前記カウンタのカウント数のディスカウント数を表すディスカウント信号を生成するディスカウント制御部と、前記カウンタのカウント数と前記ディスカウント信号が表すディスカウント数とに基づき、前記出力信号の位相のエラーの有無を判定するエラー判定部とを含む。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

位相調整装置およびカメラ

【課題】 より簡易な構成で、データとクロックとの位相の関係を適切に調整するための手段を提供する。

【解決手段】 位相調整装置は、第1データ取得部と、第2データ取得部と、判定部と、位相調整部とを備える。第1データ取得部は、入力されるシリアル転送データの基準位相での第1出力と、第1出力に対して第1遅延量による位相差を付与した第2出力とをそれぞれ取得する。第2データ取得部は、第1遅延量よりも大きな第2遅延量による位相差を第1出力に対して付与した第3出力と、第3出力に対して第1遅延量による位相差を付与した第4出力とをそれぞれ取得する。判定部は、第1データ取得部および第2データ取得部の各出力について、シリアル転送データに含まれる検出対象のデータ列が検出できたか否かをそれぞれ判定する。位相調整部は、判定部での判定結果に基づいて、出力されるシリアル転送データに付与する遅延量を調整する。

(もっと読む)

判定帰還型等化器を用いた受信機のためのクロック回復回路

【課題】 本発明は、判定帰還型等化器を用いた受信機のためのクロック回復回路を提供する。

【解決手段】 特定の実施形態では、方法は、判定帰還型等化器(DFE)により、送信データを有する第1の信号を受信し、前記DFEにより、前記送信データを有する等化信号に前記第1の信号を調整し、位相誤り検出器により、前記送信データの4分の1のデータ・レート以下のデータ・レートで位相誤りを検出し、前記位相誤り検出器により、前記検出された位相誤りに基づき位相誤りレベルを生成し、前記DFE及び前記位相誤り検出器のためのクロック回復回路により、前記位相誤りレベルに基づき前記送信データに関連するクロック信号を回復する。

(もっと読む)

信号デスキュー方法および装置

【課題】超低圧VDDデジタル回路においては、クロックスキューは厳密な時間収率の劣化を招く大きな原因であるが、コンピュータによる設計の高度な自動化(EDA)手段の様々なプロセスが存在する中でのスキュー調和がとれたクロックツリーを実現する。

【解決手段】参照信号およびローカル信号を受信し、それらを比較して位相差を検出するための位相比較器、位相差の値に関連して制御信号のオン/オフを切り替えるための制御回路、およびローカル信号バッファーを有し、前記ローカル信号バッファーはnMOSトランジスタおよび/またはpMOSトランジスタを有しており、前記制御信号に応じてホットキャリアインジェクションストレスをnMOSトランジスタまたはpMOSトランジスタに掛けてnMOSトランジスタまたはpMOSトランジスタのしきい値電圧を増加させる。

(もっと読む)

サンプリングクロック同期装置、ディジタルコヒーレント受信装置およびサンプリングクロック同期方法

【課題】受信品質の向上を図る。

【解決手段】サンプリングクロック同期装置は、A/Dコンバータ、フィルタ部およびサンプリング同期化部を備える。A/Dコンバータは、サンプリングクロックにもとづいて、アナログ/ディジタル変換を行う。フィルタ部は、A/Dコンバータから出力された、スペクトル狭窄化を受けている信号に対して、スペクトル狭窄化の特性と逆特性のフィルタ特性で、スペクトル狭窄化による帯域制限を補償する。サンプリング同期化部は、スペクトル狭窄化の補償後の信号から、サンプリングクロックの位相ずれを検出して、サンプリングクロックの位相を調整し、サンプリングタイミングの同期をとる。

(もっと読む)

ラッチ回路、CDR回路、および受信装置

【課題】 消費電力を抑えた受信回路を提供する。

【解決手段】 本発明では、差動信号を差動増幅させる際に、差動入力によって発生する電流を対となる差動出力により遮断することで差動信号をラッチする回路を提供する。該ラッチ回路の適用により、受信信号の差動信号電圧差が小さい場合でも伝送データを受信できる為、増幅用アンプの削減が可能となり、受信装置の消費電力の低減を図ることができる。

(もっと読む)

通信回路及びサンプリング調整方法

【課題】サンプリングクロックのタイミングを受信データのタイミングに合わせる通信回路及びサンプリング調整方法を提供することを目的とする。

【解決手段】入力される通信データのビットレートに対しm倍の周波数であり、通信データの1ビット周期にmより小さい奇数であるnパルス連続するサンプリングクロックを用いてサンプリングを行うサンプリング回路12と、通信データの1ビット周期にサンプリングされたn個の受信データの多数決により多数と判定された値の受信データを出力する多数決回路14と、n個の受信データのうち先頭近傍のデータが他のデータと異なっているときサンプリングクロックを所定量だけ遅らせ、n個の受信データのうち最後尾近傍のデータが他のデータと異なっているときサンプリングクロックを所定量だけ進めるサンプリングクロック調整手段24,34,35とを有する。

(もっと読む)

データ受信装置、データ送信装置、制御方法

【課題】 データ受信装置がデータ送信装置から受信するデータと、データ受信装置がデータ送信装置へ出力するクロックとの間で1サイクル以上の遅延がある場合、データ受信装置がデータ送信装置から供給されるデータを取りこぼしてしまう可能性がある。

【解決手段】 データ送信装置へコマンドを送信する際に、コマンドの送信終了タイミングと、送信装置からの前記コマンドに対応するデータの受信開始タイミングとの間のサイクル数をカウントする。

(もっと読む)

位相調整回路、受信装置、および通信システム

【課題】回路構成の複雑化、消費電力の増大を抑止しつつ、複数チャネル間の同期化が可能となり、高速シリアル通信に適用することが可能な位相調整回路、受信装置、および通信システムを提供する。

【解決手段】位相調整回路310は、クロックに応答して所定の位置に同期パターンが挿入されているシリアルデータをパラレルデータに変換するシリアルパラレル変換部313と、シリアルパラレル変換部313によるパラレルデータの同期パターンの位置を検出する同期パターン位置検出部316と、同期パターン位置検出部316で検出された同期パターン位置情報により、同期パターン位置に合わせてパラレルデータおよびクロックの位相を調整する調整部315とを有する。

(もっと読む)

複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法

【課題】システムは、メモリコントローラおよび直列接続されている複数の半導体デバイスを備える。各デバイスはデータを格納する。コントローラは、デバイスの動作を同期させるクロックを供給する。

【解決手段】各デバイスは、イネーブル信号によって選択的にイネーブルまたはディセーブルされるPLLを備える。選択デバイスのPLLはイネーブル信号によってイネーブルされ、他のデバイスはディセーブルされる。イネーブルされたPLLは、90°の倍数の位相シフトで複数の再生クロックを供給する。データ転送は、再生クロックのうちの1つのクロックと同期する。ディセーブルされたPLLのデバイス内で、データ転送は入力クロックと同期する。イネーブルおよびディセーブルされたPLLにより、各デバイスはソース同期クロッキングおよび共通同期クロッキングを行う。最後のデバイスのデバイス識別子の最下位ビットがクロック整列を決定する。

(もっと読む)

1 - 20 / 261

[ Back to top ]