Fターム[5K047GG56]の内容

デジタル伝送方式における同期 (12,489) | 網同期;クロック、ビット同期 (2,470) | 従属同期 (106)

Fターム[5K047GG56]に分類される特許

1 - 20 / 106

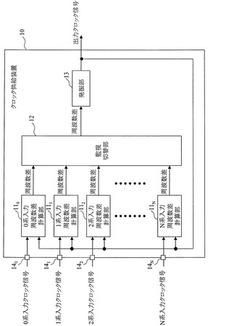

クロック供給方法およびクロック供給装置

【課題】本発明は、クロック基準信号が異常な場合においてもクロックパスの監視が可能であり、かつ、正常系のクロックパスへの切替を可能とすることを目的とする。

【解決手段】本願発明のクロック供給装置10は、3つ以上のクロック入力部140〜14Nと、クロック入力部140〜14Nから入力されたいずれかのクロック周波数で発振する発振部13と、クロック入力部140〜14Nからの各入力クロック信号の周波数と発振部13の発振周波数との各周波数差を計算する周波数差計算部110〜11Nと、周波数差計算部110〜11Nからの各周波数差が予め定められた閾値を超えたか否かを判定し、閾値を超えたクロックパスの個数と閾値を超えていないクロックパスの個数に関して多数決を用いて比べることにより各クロックパスが正常であるか、異常であるかを判定する監視切替部12と、を備える。

(もっと読む)

受信装置、周波数偏差算出方法及びコンピュータプログラム

【課題】異なるタイミングで受信されるリファレンス信号間の相関から推定できる周波数偏差の範囲を拡大する。

【解決手段】受信装置12は、異なる複数の受信間隔で受信されるリファレンス信号に基づいて、複数の受信間隔毎に各受信間隔において生じる受信信号の位相差を推定する処理と、推定された位相差に基づいて、複数の受信間隔毎に複数の位相差候補を決定する候補決定処理と、複数の受信間隔毎に選択される位相差候補同士を組み合わせて形成される位相差候補の複数の組合せの中から、複数の受信間隔における受信信号の位相差を示す組合せを選択する選択処理と、選択された組合せに含まれる位相差候補に基づいて受信信号の周波数偏差を推定する推定処理を実行する制御部17を備える。

(もっと読む)

同期ネットワークデバイス

【課題】物理層デバイスおよび同期デバイスの複数のポート間でクロックを同期させる方法を提供する。

【解決手段】制御方法は、グランドマスタークロックのソースとなるポートを選択するステップを含む(302)。選択されたポートは、リンク先からの送信に基づいてグランドマスタークロックを再生する。マルチポートPHY ICは、グランドマスターソースポートのRX_CLKを出力する(304)。グランドマスターソースポートのTX_CLKは、ローカルオシレータから取得される(306)。そして、ほかの全てのポートのTX_CLKは、クロック同期部の出力から取得される(308)。クロック同期部は、グランドマスターソースポートを有するマルチポートPHY ICからの再生クロックに基づいて同期させる(310)。

(もっと読む)

揺らぎの蓄積を克服して大きなネットワーク上で精密なクロック分配を達成するシステムおよび方法

【課題】パケット交換ネットワーク全体にわたってクロックを同期するシステムおよび方法は、揺らぎの蓄積を解消して大きなネットワーク全体にわたって高精度のクロック分配を可能にする。

【解決手段】標準的な高精度時間プロトコル(PTP)の同期メッセージまたは同様の時間同期メッセージに加えて、各クロック再生器ステージは、前のステージからグランドクロック誤差メッセージを受信し、その誤差メッセージを自身のステージクロック誤差で更新した後、更新後のグランドクロック誤差を次のステージに送信する。これにより、同期アルゴリズムは前のステージの誤差を補償して、各クロック再生器ステージを直接グランドマスタクロックに有効にロックすることができる。

(もっと読む)

データ受信回路、データ送受信システム及びデータ受信方法

【課題】データ送信回路とデータ受信回路とが互いに同期していないときに、データ受信回路においてデータ過多又はデータ欠損を生じさせることなく、音声又は音楽の再生品質を向上する。

【解決手段】サンプリングレートコンバータ4は、送信LRクロックLRsに同期したオーディオデータDaを送信LRクロックLRsAに同期したオーディオデータDacに変換する。周期測定部1は、高速サンプリングクロックfsrを用いて送信LRクロックLRsAの周期を測定する。データ補間部2は、送信LRクロックLRsAの周期と受信LRクロックLRrの周期との周期差を算出し、受信LRクロックLRrの各出力タイミングにおいて、算出された周期差に基づいて当該各出力タイミングにおける送信LRクロックLRsAの位相を算出し、オーディオデータDacを算出された位相に基づいて補間して補間オーディオデータDinsrを生成する。

(もっと読む)

光受信装置

【課題】連続信号対応の汎用的なCDR回路を備えた制御LSIに、応答特性を損なうことなくシリアルデータ信号を入力する。

【解決手段】光受信装置は、データ信号期間/無信号期間を問わず信号を出力し続けるLA回路6と、LA回路6の出力信号からクロックを抽出しデータを再生するバーストCDR回路2とを備える。バーストCDR回路2は、LA回路6の出力信号とタイミングの合った再生クロックを出力する第1の電圧制御発振器と、第1の電圧制御発振器と同一の周波数で発振する第2の電圧制御発振器と、第2の電圧制御発振器の出力と参照クロックとを周波数比較して、第1、第2の電圧制御発振器を所望のデータレート周波数で発振させる周波数制御信号を出力する周波数比較器と、LA回路6の出力信号の識別再生を再生クロックに基づいて行う識別回路とを有する。

(もっと読む)

クロック同期式シリアル通信装置およびその通信制御方法

【課題】マスターデバイスと複数のスレーブデバイスとがシリアルデータ通信を行う場合に、通信対象とするスレーブデバイスの指定時に生じる通信オーバーヘッドを削減すること。

【解決手段】クロック同期式シリアル通信装置は、クロック信号の周波数を調整するとともに、周波数が調整されたクロック信号およびデータ信号を出力するマスターデバイスと、前記マスターデバイスから出力されたクロック信号およびデータ信号を受信するとともに、受信したクロック信号の周波数を計測する複数のスレーブデバイスとを備え、

前記複数のスレーブデバイスは、それぞれ、識別用の周波数を保持し、計測した周波数と該識別用の周波数とが一致したか否かに応じて、前記マスターデバイスから出力されたデータ信号を保持または破棄する。

(もっと読む)

CDR回路および受信回路

【課題】参照クロックが不要なインタポレータ方式のCDR回路を小面積で実現することができる技術を提供する。

【解決手段】CDR回路101において、再生クロックのエッジの近傍と遠方にある伝送データのエッジの個数を計測するデータエッジ位置計測回路117と、伝送データのエッジの近傍と遠方にある再生クロックのエッジの個数を計測するクロックエッジ位置計測回路118とを含み、データエッジ位置計測回路117の計測結果とクロックエッジ位置計測回路118の計測結果に応じて、再生クロックの周波数を調整する周波数調整回路116を有する。エッジの近傍と遠方の判定には、CCL回路の最小入力振幅を制御することで実現している。

(もっと読む)

光受信器

【課題】直交位相変調された光信号を受信する光受信器にて行われる、受信データを正しく再生するためのパターン同期において、ビットシフトとパターンチェンジの重複する組み合わせを使わず信号導通を高速に確立する。

【解決手段】変調方式とパターン同期検索順序で生じる重複する組み合わせの確認を行わない制御方法であって、2つのデータ列を多重化するMUX回路が多重化したデータのデータ確認を信号チェック回路が行い、ビットシフト・パターンチェンジ制御回路は、データ確認結果により、ビットシフト回路及びパターンチェンジ回路を制御して、正しい再生データの正しい組み合わせを検出し、信号導通を確立する。ここにおいて、ビットシフト回路及びパターンチェンジ回路については、重複する組み合わせの確認が行われないようにする。

(もっと読む)

位相調整装置

【課題】デジタル画像データとクロックとの位相を調整する場合に、投影画像による目視判断などを行わないで自動的に調整する。

【解決手段】データセレクタ104は、遅延回路101から並列に供給される互いに所定時間遅延時間の異なる複数の遅延クロックのうち、セレクト端子に供給されるnビットカウンタ値に応じた1種類の遅延時間の遅延クロックを選択する。ラッチ回路105は、デジタルデータをデータセレクタ104から出力された遅延クロックの立ち上がり及び立ち下りでラッチする。4段シフトレジスタ106は、ラッチ回路105からのデジタルデータを、データセレクタ104から出力された遅延クロックをシフトクロックとして4段シフトする。コンパレータ107は、4段シフトレジスタ106の入力デジタルデータと出力デジタルデータとを比較し、比較結果が一致する場合は、ラッチが正しくできていると判断する。

(もっと読む)

ラッチ回路、CDR回路、および受信装置

【課題】 消費電力を抑えた受信回路を提供する。

【解決手段】 本発明では、差動信号を差動増幅させる際に、差動入力によって発生する電流を対となる差動出力により遮断することで差動信号をラッチする回路を提供する。該ラッチ回路の適用により、受信信号の差動信号電圧差が小さい場合でも伝送データを受信できる為、増幅用アンプの削減が可能となり、受信装置の消費電力の低減を図ることができる。

(もっと読む)

無線通信装置

【課題】対象装置からの信号に基づいて当該対象装置と同期をとる構成において、非同期状態から同期状態へ早期に復帰することが可能な無線通信装置を提供する。

【解決手段】無線通信装置201は、対象装置から受信した受信データに基づいて生成された再生タイミング信号に基づいて第1の制御電圧を生成し、電圧制御発振器25に第1の制御電圧を供給することにより、再生タイミング信号の周波数成分のうち、所定の周波数以上の成分が減衰された周波数成分を有し、かつ再生タイミング信号に同期する基準タイミング信号を生成するためのジッタ抑圧部12と、タイミング信号生成部22によって生成される再生タイミング信号の異常を検知し、異常を検知した場合には、第1の制御電圧の代わりに、第1の所定範囲内の電圧である第2の制御電圧を電圧制御発振器25に供給するための発振器制御部13とを備える。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

受信回路、送信回路、通信システム、及び通信システムの送信設定方法

【課題】信号遷移発生用の符号化を用いることなくデータとクロックとを1つの信号に纏めて送受信可能な送信回路及び受信回路を提供する。

【解決手段】送信回路は、データ信号とクロック信号とを重み付け加算することにより生成した信号を送信する。また受信回路は、受信した第1の信号の信号遷移からクロック信号を抽出するクロック抽出回路と、抽出されたクロック信号を第1の信号から減算することにより第2の信号を生成する減算回路と、抽出されたクロック信号に応じたタイミングにおいて第2の信号をデータ判定するデータ判定回路とを含む。

(もっと読む)

光パケットスイッチ装置

【課題】伝送路の帯域利用効率を向上できる光パケットスイッチ装置を提供する。

【解決手段】光パケットスイッチ装置10は、光カプラ13と、光スイッチ部12と、光スイッチ制御部14とを備える。光スイッチ制御部14は、光電変換部16と、シリアル/パラレル変換部18と、並び検出部17と、並び換え部19と、フレーム同期部20と、方路検出部24と、制御信号生成部26と、並び検出部17からのフレーム同期パターンの並び情報に基づいて、光スイッチ部12に光スイッチ制御信号を出力するタイミングを調整するタイミング調整部27とを備える。

(もっと読む)

通信装置、および、通信方法

【課題】対向装置のクロックモードに応じて自装置のクロックモードをより適切に設定することができる通信装置を提供すること。

【解決手段】受信信号から受信クロックを抽出する受信クロック抽出部11と、自走クロックを出力する自走モードと、受信クロックに同期させた従属クロックを出力する従属モードとのいずれかに切替可能なクロック生成部12と、自走クロックおよび受信クロックの周波数差を検出するクロック比較部13と、周波数差が検出されなかった場合に、自走クロックの周波数を変更させる自走クロック周波数制御部14と、クロック生成部12を自走モードにした上でクロック比較部13により周波数差があると検出された場合、および、自走クロックの周波数の変更後に周波数差があると検出された場合に、クロック生成部12を従属モードにするクロックモード制御部15と、を備える。

(もっと読む)

受信回路

【課題】受信信号にプリアンブルまたはユニークワードが含まれているかに係らず、かつ受信信号の符号化方式に依存せずに、データの先頭が検出できる受信回路を提供する。

【解決手段】受信回路100は、1シンボルの参照信号を受信信号に対してスライディングさせながら相関演算をすることによって、相関信号を生成する相関演算部11を備える。参照信号は、前半の1/2シンボル期間がハイレベルであり、後半の1/2シンボル期間がロウレベルである。受信回路100は、さらに、受信信号に対して、参照信号の1/2シンボル期間分だけ遅延させて、遅延信号を出力する遅延部17と、相関信号の先頭のピークのタイミングを遅延信号に含まれるデータの先頭のタイミングとして検出するデータ先頭タイミング検出部16とを備える。

(もっと読む)

データ位相同期装置およびデータ位相同期方法

【課題】簡易な構成でデータ位相の同期をとることが可能なデータ位相同期装置を得ること。

【解決手段】デリミタ値、トレーニングパタンフレーム番号に対応するカウンタ値、反転カウンタ値を含むトレーニングパタンフレームを生成するトレーニングパタンフレーム合成部14と、トレーニングパタンフレームを複数のレーン内のデータに同期して挿入する選択部15と、受信データに挿入されたトレーニングパタンフレームからデリミタ値を検出し、フレーム位相を判定するデリミタ検出部18と、フレーム位相に基づいてトレーニングパタンフレーム番号を再生するカウンタ再生部19と、フレーム位相およびトレーニングパタンフレーム番号に基づいてレーン毎のスキュー量を推定するスキュー推定部20と、レーン毎のスキュー量に基づいてレーン間のスキューを打ち消す制御を行うデスキュー制御部21と、を備える。

(もっと読む)

2チャンネルネットワークシステム

【課題】ピュアアロハの低消費電力特性と、スロッテドアロハの高い周波数利用効率とを備えたネットワークシステムが求められている。

【解決手段】起動時は、従来のピュアアロハと同様に通信を行うが、各端末局は中央局からの受信確認信号を時計信号として用い、これに同期するようにパケット送信を行うことで、擬似的にスロッテドアロハとする。中央局の受信確認信号は、周期的なクロックパルスに同期して送信し、端末局は受信した受信確認信号に同期したクロック信号を生成し、当初の非同期状態から同期状態でパケット送信を行う形態に移行する。端末局の受信部は、パケットの送信後の所定の期間だけ動作状態にする。また、端末局の受信部は、動作状態期間を変化させて、受信確認信号を探索し、受信確認信号を受信できるように上記期間を維持することで、受信した受信確認信号に同期したクロック信号を生成する。

(もっと読む)

送信装置、受信装置及び伝送システム

【課題】パケット間隔が不定で、伝送遅延変動が発生する伝送環境においても、クロックリカバリを確実に実現する。

【解決手段】送信装置1のMU生成部13は、発振器10からのカウンタ値に基づいてDTS及びCTSを生成し、AUにDTS及びCTSを付加すると共に、システムタイム生成部11からのUTC時刻を参照時刻に設定して付加し、MUを生成する。IP/UDPパケット化部15は、MUが分割されたATSパケットをIPパケットに格納し、放送ネットワーク/通信回線3を介して受信装置2へ送信する。受信装置2は、受信したIPパケットに含まれるDTS及び参照時刻、発振器26からのカウンタ値並びにシステムタイム生成部23からのUTC時刻に基づいて、発振器26のカウンタ値を補正する。これにより、受信装置2の発振器26におけるクロックを送信装置1の発振器10におけるクロックに同期させることができる。

(もっと読む)

1 - 20 / 106

[ Back to top ]