Fターム[5K047MM62]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本回路、機能 (1,980) | 比較回路 (311)

Fターム[5K047MM62]の下位に属するFターム

位相比較回路 (220)

Fターム[5K047MM62]に分類される特許

1 - 20 / 91

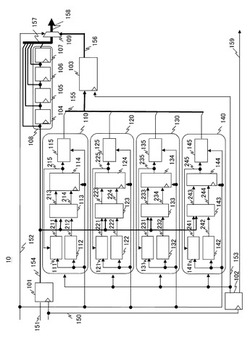

シリアル同期検出回路及び同期検出方法

【課題】異なるプロトコルのシリアル通信に対応可能であって、より回路規模を抑制したシリアル同期検出回路及び同期検出方法を提供する。

【解決手段】本実施の形態にかかるシリアル同期検出回路10は、それぞれ異なるビット長の同期コードを有する複数のプロトコルに対応可能なシリアル同期検出回路である。シリアル同期検出回路1は、同期コードを含むシリアル信号を所定ビット数単位のパラレル信号に変換するシリアルパラレル変換回路101と、変換されたパラレル信号と、複数のプロトロコルに含まれる任意のプロトコルの同期コードを前記所定ビット数に分割した同期期待値とを、所定ビット数単位で順に繰り返し比較して、同期コード全体を比較することにより、同期を検出する同期検出回路110〜140とを備えている。

(もっと読む)

受信装置

【課題】パターン検出回路の回路規模を削減し、コストダウンすることができる受信装置を提供する。

【解決手段】Mビット長の特定パターンを含むシリアルデータをNビット(N<M)幅のパラレルデータに変換する変換回路と、パラレルデータの、連続するNビットの範囲のそれぞれのビットを先頭とするLビット(N≦L<M)の部分と特定パターンの対応する部分とを比較する比較回路と、比較回路が、連続するNビットの範囲の先頭からKビット目(K=0〜N−1)を先頭とするLビットの部分と特定パターンの先頭からLビットの部分との一致を検出し、さらに、L/Nの商をq、余りをrとして、Nビットの範囲およびK、N、q、rによって決まる特定の周期内に、特定のビットを先頭とするJビット(J≦M−L)の部分と特定パターンのL+1ビット目からJビットの部分との一致を検出する検出回路とを備える。

(もっと読む)

受信装置

【課題】特定パターンの連続検出を効率良く行い、かつ連続検出回数を正しく判断することができる受信装置を提供する。

【解決手段】受信装置は、Mビット長の特定パターンを含むシリアルデータをNビット(N<M)幅のパラレルデータに変換するシリアルパラレル変換回路と、所定のビット幅のパラレルデータを格納するレジスタ群と、所定のビット幅のパラレルデータのうちの連続するMビットの複数の格納パターンのそれぞれと特定パターンとを比較する比較回路と、比較回路が、パラレルクロックの第1の周期内に、Nビットの範囲の先頭からKビット目(K=0〜N−1)を先頭とする格納パターンと特定パターンとの一致を検出し、さらに、M/Nの商をQ、余りをRとして、Nビットの範囲およびK、N、Q、Rによって決まる特定の周期内に、特定のビットを先頭とする格納パターンと特定パターンとの一致を検出して、特定パターンを含むシリアルデータの受信を検出する検出回路とを備える。

(もっと読む)

トランシーバ

【課題】サンプリングに使用するクロックとは非同期に送信データが供給されるトランシーバにおいて、送信データの信号レベルを正しくサンプリングできるようにする。

【解決手段】送信データTXDのスタートビットの開始エッジのタイミング(開始タイミング)が検出されると、バスクロックBCKに同期し、そのバスクロックBCKの1周期当たり4個のサンプリング用エッジを有するサンプリングSCKを用い、開始タイミングを起点として2個目のサンプリング用エッジのタイミングで送信データTXDをサンプリングし、以後、4個目のサンプリング用エッジのタイミング毎に、送信データTXDをサンプリング(ラッチ)する。そのサンプリングしたデータを、更に、バスクロックBCKの立ち下がりエッジでサンプリングすることによって、バスクロックBCKに同期した同期送信データdTXDを生成する。

(もっと読む)

通信装置、制御信号生成方法、シャッターメガネ、及び通信システム

【課題】 受信データから得られる基準タイミングに基づいた表示装置等の被制御装置の制御を遅延なくかつ低消費電力で可能にする通信装置、その被制御装置を制御するための制御信号生成方法、受信データから得られる基準タイミングに基づいたシャッターの開閉を遅延なくかつ低消費電力で可能にするシャッターメガネ、及び基準タイミングを表すデータの送受信を遅延なくかつ低消費電力で可能にする通信システムを提供する。

【解決手段】 間欠的に到来するデータ内に所定の基準タイミング信号パターンが存在するか否かを識別するタイミング信号識別手段と、タイミング信号識別手段によって所定の基準タイミング信号パターンの存在が識別された場合に被制御装置に対する制御信号を生成する制御信号生成手段と、通信装置の制御を司る制御手段と、を備える。

(もっと読む)

半導体装置、及び情報処理装置

【課題】

安定的な動作を確保できる半導体回路装置、及び情報処理装置を提供することを課題とする。

【解決手段】

半導体装置は、入力信号に遅延を与える遅延部と、前記遅延部から出力される出力信号の位相を検出する位相検出部と、前記位相検出部から出力される位相情報に基づき、前記出力信号の位相の安定動作範囲を設定する設定部と、前記安定動作範囲から位相が外れた前記出力信号の検出回数をカウントするカウンタと、前記遅延部の動作条件又は外的要因に応じて、前記カウンタのカウント数のディスカウント数を表すディスカウント信号を生成するディスカウント制御部と、前記カウンタのカウント数と前記ディスカウント信号が表すディスカウント数とに基づき、前記出力信号の位相のエラーの有無を判定するエラー判定部とを含む。

(もっと読む)

光受信装置

【課題】連続信号対応の汎用的なCDR回路を備えた制御LSIに、応答特性を損なうことなくシリアルデータ信号を入力する。

【解決手段】光受信装置は、データ信号期間/無信号期間を問わず信号を出力し続けるLA回路6と、LA回路6の出力信号からクロックを抽出しデータを再生するバーストCDR回路2とを備える。バーストCDR回路2は、LA回路6の出力信号とタイミングの合った再生クロックを出力する第1の電圧制御発振器と、第1の電圧制御発振器と同一の周波数で発振する第2の電圧制御発振器と、第2の電圧制御発振器の出力と参照クロックとを周波数比較して、第1、第2の電圧制御発振器を所望のデータレート周波数で発振させる周波数制御信号を出力する周波数比較器と、LA回路6の出力信号の識別再生を再生クロックに基づいて行う識別回路とを有する。

(もっと読む)

データ転送回路

【課題】異なるクロックのデータ転送を行うときに、パルスストレッチ回路を用いることなく、不正な値が転送されないようにすることを目的とする。

【解決手段】クロックCLK−Aで動作する入力側回路部2とクロックCLK−Bで動作する出力側回路部3とを有し、データData−Aを出力データData−Bとして出力させる回路であって、入力側回路部2に設けられ、入力データData−Aを入力して中間データMidとして出力する入力側フリップフロップ4と、出力側回路3に設けられ、中間データMidを入力して出力データData−Bとして出力させる出力側フリップフロップ5と、出力側フリップフロップ5が中間データMidを入力するときには、中間データMidを固定値として出力するように入力側フリップフロップ4を制御する制御部6と、を備えたことを特徴とする。

(もっと読む)

位相調整装置

【課題】デジタル画像データとクロックとの位相を調整する場合に、投影画像による目視判断などを行わないで自動的に調整する。

【解決手段】データセレクタ104は、遅延回路101から並列に供給される互いに所定時間遅延時間の異なる複数の遅延クロックのうち、セレクト端子に供給されるnビットカウンタ値に応じた1種類の遅延時間の遅延クロックを選択する。ラッチ回路105は、デジタルデータをデータセレクタ104から出力された遅延クロックの立ち上がり及び立ち下りでラッチする。4段シフトレジスタ106は、ラッチ回路105からのデジタルデータを、データセレクタ104から出力された遅延クロックをシフトクロックとして4段シフトする。コンパレータ107は、4段シフトレジスタ106の入力デジタルデータと出力デジタルデータとを比較し、比較結果が一致する場合は、ラッチが正しくできていると判断する。

(もっと読む)

情報処理装置及び携帯端末

【課題】ベースバンド処理部からネットワーク網の同期信号が出力されない場合においても、音声信号の伸長処理を実行可能にする。

【解決手段】情報処理装置(1)は第1シリアルインタフェース(19)を含む。第1シリアルインタフェースは、ベースバンド処理部から取り込まれるデータが、予め設定されたデータ量に達する毎に、その状態を音声処理部(20)に通知するための通知信号を形成する通知信号生成回路(195)を含む。音声処理部は、上記通知信号に基づいてネットワーク網同期信号を形成する同期信号生成回路(205)を含む。上記ネットワーク網同期信号に基づいて上記PCM通信用のクロック信号を形成することにより、ベースバンド処理部からネットワーク網の同期信号が出力されない場合においても、音声信号の伸長処理を実行可能にする。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、送信クロックの周波数が安定するまでに多くの時間を要する問題があった。

【解決手段】本発明の半導体装置は、送信クロックCLKから生成される受信クロックRCLKと入力信号RDと間の位相の進み又は遅れを示す位相差信号を生成し、受信クロックRCLKの位相を入力信号RDの位相に追従させる制御を行う位相追従ループと、受信クロックRCLKの周波数を入力信号RDの周波数に追従させる制御を行う周波数追従ループと、を有し、入力信号RDからデータ信号Sout及びデータ信号に対応する同期クロックSCLKの抽出を行うクロックアンドデータリカバリ回路13と、位相差信号に基づき生成される周波数差信号FPに応じて周波数調整信号Fadjにより示される値を増減させる周波数誤差調整器14と、周波数調整信号Fadjに基づき送信クロックCLKの周波数を増減させる発振器12と、を有する。

(もっと読む)

位相補正回路

【課題】外部水平同期信号の入力状態が変化したときに、内部水平同期信号の位相を短時間で補正することのできる位相補正回路を提供する。

【解決手段】実施形態の位相補正回路は、入力状態変化検出部1が、外部水平同期信号HSの入力状態の変化を検出し、カウント値設定部2が、入力状態変化検出部1により外部水平同期信号HSの入力状態の変化が検出されたときに、同期カウンタ101に所望の値を設定する。

(もっと読む)

PCM信号復調回路、該復調回路に用いられるPCM信号復調方法及びPCM信号復調プログラム

【課題】入力PCM信号にノイズが含まれている場合でも、高精度で復調するPCM信号復調回路を提供する。

【解決手段】復調タイミング判定手段(タイミング制御部24、ローカルクロック25、PLL26、エンベロープ予測部27)は、ゼロクロス検出信号zbを入力すると共にピーク検出信号pbを入力して入力PCM信号ibの1周期分の位相及び振幅を含むデータptを生成し、エンベロープデータとして蓄積して基準位相標本情報及び基準周期情報を作成すると共に、基準位相標本情報及び基準周期情報に基づいて、入力PCM信号ibの後続の周期の位相及び振幅の予測情報efを作成し、予測情報efと後続の周期の位相及び振幅とを比較して誤差が所定の範囲内にあるとき、復調タイミング信号tcを出力する。復調部28により、復調タイミング信号tcに同期して復調データmdが出力される。

(もっと読む)

クロック・データリカバリ回路

【課題】デュアルレートPONシステムにおけるクロック・データリカバリ回路を1つのクロック・データリカバリ回路の構成で実現し、かつ、双方のビットレートのシステムにおける上位層との接続インターフェースを備えたマルチレート対応のクロック・データリカバリ回路を提供する。

【解決手段】入力データのタイミングに合うように位相を調整し、入力データとタイミングのあったクロック信号を出力するクロック出力回路と、クロック信号に基づいて入力データを識別し、入力データを再生した再生データを出力する識別回路と、クロック信号を分配し、第1のクロック信号と第2のクロック信号とを出力する第1の分配器と、第2のクロック信号を入力として、この第2のクロック信号をn(nは整数)分周したn分周クロック信号を出力する第1の分周器とを備える。

(もっと読む)

CDR回路

【課題】MACからの制御信号なしでも瞬時に入力データとの同期を確立し、周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するVCO11と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10とVCO11との間に設けられた、所望のデータレート周波数の信号を通過させるバンドパスフィルタ40とを備える。

(もっと読む)

受信回路、情報処理装置、およびバッファ制御方法

【課題】複数レーンのシリアル通信を行う回路において、低レイテンシーの受信回路を提供すること

【解決手段】受信回路は、レーンごとに設けられた複数のバッファと、レーン間のスキューを検出し、該レーン間のスキューを無くすように前記バッファのリードアドレスを調節する第1の信号およびレーン間のスキューの調整を行うことを示すデスキュー信号を出力するマルチレーン制御回路と、前記デスキュー信号に応じて、前記第1の信号を前記バッファに出力する、レーンごとに設けられた複数のアドレス制御回路と、を備える。

(もっと読む)

受信機の同期方法および受信回路

【課題】直交アンダーサンプリング技術を用いた受信機に簡素な同期回路を提供する。

【解決手段】A/D変換器(1)から出力されるベースバンドI/Q信号のサンプル点につき、4/シフトQPSK変調の同一シンボル期間中において+I成分と−I成分または+Q成分と−Q成分の和を時系列的に連続して算出し(21)、時間的変化からシンボルタイミングを再生する(22)。

(もっと読む)

データ処理装置及びデータ処理システム

【課題】信号受信から信号送信までのタイミング誤差を小さくする。

【解決手段】複数のデータ処理ノードが所定のトポロジで通信路に接続されたデータ処理システムにおいて、データ処理ノードのデータ処理装置は、受信信号に基づいて受信クロック信号を再生し、再生された受信クロック信号に同期して受信データ再生部(122)で受信信号から受信データを再生すると共に、再生された受信データに対する送信データを送信データ生成部(123)で生成し、送信部(125)で送信データから送信信号を生成して送信クロック信号に同期して通信路に送信する、通信機能を備える。データ処理ノードは更に、受信データ再生部による信号の受信から送信部による送信信号の送信までに許容される時間に対して処理時間が短いとき、その誤差時間を検出する検出部(124)を有する。送信部は検出部による誤差時間の経過を待って送信データの送信を開始する。

(もっと読む)

半導体装置およびデータ転送方法

【課題】複数のクロックドメイン間での非同期データ転送を汎用的に行うことができるようにする。

【解決手段】データ転送元の第1クロックドメイン10と、データ転送先の第2クロックドメイン20と、前記第1クロックドメインの第1データDATAを前記第2クロックドメインの第2データD3に乗せ換えるデータ乗せ換え回路40,21,22,23と、を有する半導体装置であって、前記データ乗せ換え回路は、前記第1データDATAおよび前記第2データD3を直接比較して第1制御信号ENを出力する第1論理回路23を有するように構成する。

(もっと読む)

クロック供給システム、クロック供給装置、網同期クロック管理装置、およびコンピュータプログラム

【課題】ネットワーク内の或る局においてクロックの周波数変動(周波数精度の劣化)が生じた場合において、当該局のみならず、その下位局など、階層的にクロックの周波数精度の劣化が生じる場合に、網全体を見渡し、より少ない局でのクロック従属元の切替を行う。

【解決手段】クロック供給システム1において、クロック供給装置21は、入力クロックおよび出力クロックの周波数精度を計測し、周波数精度が劣化した場合に、警報として網同期クロック管理装置100に送信する。網同期クロック管理装置100は、クロック供給装置21から警報を受信した場合に、当該警報発出局の上位局と、当該警報発出局の下位局群と、における警報出力の状況を検出し、所定の規則に従い、クロック従属元を切り替えるべき局を判定し、この局にクロック従属元の切替信号(制御信号)を出力する。

(もっと読む)

1 - 20 / 91

[ Back to top ]