Fターム[5K047MM63]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本回路、機能 (1,980) | 比較回路 (311) | 位相比較回路 (220)

Fターム[5K047MM63]に分類される特許

1 - 20 / 220

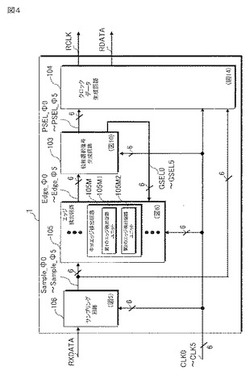

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

受信装置、周波数偏差算出方法及びコンピュータプログラム

【課題】異なるタイミングで受信されるリファレンス信号間の相関から推定できる周波数偏差の範囲を拡大する。

【解決手段】受信装置12は、異なる複数の受信間隔で受信されるリファレンス信号に基づいて、複数の受信間隔毎に各受信間隔において生じる受信信号の位相差を推定する処理と、推定された位相差に基づいて、複数の受信間隔毎に複数の位相差候補を決定する候補決定処理と、複数の受信間隔毎に選択される位相差候補同士を組み合わせて形成される位相差候補の複数の組合せの中から、複数の受信間隔における受信信号の位相差を示す組合せを選択する選択処理と、選択された組合せに含まれる位相差候補に基づいて受信信号の周波数偏差を推定する推定処理を実行する制御部17を備える。

(もっと読む)

クロック再生回路

【課題】ジッタが小さく、面積が小さなクロック再生回路を提供する。

【解決手段】このクロック再生回路は、各UGにおける外部データ信号列Dinの最初の立ち上がりエッジに応答して論理レベルが反転される信号PD_Dinと、内部クロック信号VCOCLKに同期したクロック信号PD_Cinとを生成するエッジ抽出回路1と、信号PD_Dinとクロック信号PD_Cinの位相を比較し、比較結果を示す信号UP,DNを出力する位相比較器6とを備える。したがって、各UGで1回だけ位相比較を行なうので、データパターンに依存するジッタを抑制できる。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

CDR回路、受信装置、および送受信システム

【課題】非線形位相比較器を用いたCDR回路、受信装置、および送受信システムの再生クロックの位相追従精度を向上させる。

【解決手段】CDR回路106、受信装置101、および送受信システム100は、受信データ105および再生クロック119が入力される非線形位相比較器の出力に、受信データに対する、再生クロックに対して位相差を有するクロックの遅れまたは進みに応じて重み付けをし、重み付けされた出力に基づいて再生クロックの位相を調整する。

(もっと読む)

同期化回路及び同期化方法

【課題】短時間に受信側クロックで位相を同期化すること。

【解決手段】受信したデータを同期化する同期化回路10は、位相差判定回路15と第1のFF11と第2のFF12とを有する。位相差判定回路15は、同期化回路10と接続された他装置から受信したデータを同期化回路の内部クロックの位相で受付けた場合、データを安定に捉えられるか否かを判定する。第1のFF11は、位相差判定回路15によってデータを内部クロックの位相で安定に捉えられると判定された場合、データと内部クロックとを受付け、データを内部クロックの位相で捉えて同期化する。第2のFF12は、位相差判定回路15によってデータを内部クロックの位相で安定に捉えられないと判定された場合、データと位相が反転された内部クロックとを受付け、データを位相が反転された内部クロックの位相で捉えて同期化する。

(もっと読む)

適応型受信システム、適応型送受信システム及び複数チャネル送受信システム

【課題】ロックポイント付近におけるサンプリングクロックの位相の調整と、イコライザ部の制御とを安定させ、ジッタトレランスを高める。

【解決手段】位相比較部は、サンプリングタイミングとサンプリングタイミングよりも第一の所定位相分前のタイミングとの間の第一区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LAG(n)を出力するとともに、サンプリングタイミングとサンプリングタイミングよりも第二の所定位相分後のタイミングとの間の第二区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LEAD(n)を出力する。判定部は、検出データパターンの各ビットに対応する位相比較信号LAG(n),LEAD(n)の出力パターンを所定の比較対象パターンと比較し、合致するか否かに基づいて、等化信号EQDATAの1ビットがサンプリングクロックCKの1周期よりも長いか短いかを判定する。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

切替装置および切替方法

【課題】 例えば伝送速度40Gb/s以上の高速な光ネットワークに適用する場合にも、小規模で低消費電力の回路構成により現用系と冗長系間の遅延量の調整が実現可能な切替装置を提供することを目的としている。

【解決手段】 入力した第1の伝送信号および第2の伝送信号のいずれか一方から他方に切替を行って出力する切替装置であって、前記第1の伝送信号および前記第2の伝送信号の間の遅延量に基づくオフセットをクロック信号に与えたオフセットクロック信号を用いて前記遅延量の調整を行う遅延量調整手段を備えたものである。

(もっと読む)

位相調整装置およびカメラ

【課題】 より簡易な構成で、データとクロックとの位相の関係を適切に調整するための手段を提供する。

【解決手段】 位相調整装置は、第1データ取得部と、第2データ取得部と、判定部と、位相調整部とを備える。第1データ取得部は、入力されるシリアル転送データの基準位相での第1出力と、第1出力に対して第1遅延量による位相差を付与した第2出力とをそれぞれ取得する。第2データ取得部は、第1遅延量よりも大きな第2遅延量による位相差を第1出力に対して付与した第3出力と、第3出力に対して第1遅延量による位相差を付与した第4出力とをそれぞれ取得する。判定部は、第1データ取得部および第2データ取得部の各出力について、シリアル転送データに含まれる検出対象のデータ列が検出できたか否かをそれぞれ判定する。位相調整部は、判定部での判定結果に基づいて、出力されるシリアル転送データに付与する遅延量を調整する。

(もっと読む)

信号デスキュー方法および装置

【課題】超低圧VDDデジタル回路においては、クロックスキューは厳密な時間収率の劣化を招く大きな原因であるが、コンピュータによる設計の高度な自動化(EDA)手段の様々なプロセスが存在する中でのスキュー調和がとれたクロックツリーを実現する。

【解決手段】参照信号およびローカル信号を受信し、それらを比較して位相差を検出するための位相比較器、位相差の値に関連して制御信号のオン/オフを切り替えるための制御回路、およびローカル信号バッファーを有し、前記ローカル信号バッファーはnMOSトランジスタおよび/またはpMOSトランジスタを有しており、前記制御信号に応じてホットキャリアインジェクションストレスをnMOSトランジスタまたはpMOSトランジスタに掛けてnMOSトランジスタまたはpMOSトランジスタのしきい値電圧を増加させる。

(もっと読む)

CDR回路

【課題】ジッタの抑圧と応答時間の短縮とを両立させる。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO11と、G−VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO12と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ回路3と、入力データ4のデータ信号期間の少なくとも一部において、ゲーティング回路10の出力パルスが再生クロック7に与える影響を、入力データ4の同期信号期間と比較して小さくするよう制御する可変減衰器16とを備える。

(もっと読む)

サンプリングクロック同期装置、ディジタルコヒーレント受信装置およびサンプリングクロック同期方法

【課題】受信品質の向上を図る。

【解決手段】サンプリングクロック同期装置は、A/Dコンバータ、フィルタ部およびサンプリング同期化部を備える。A/Dコンバータは、サンプリングクロックにもとづいて、アナログ/ディジタル変換を行う。フィルタ部は、A/Dコンバータから出力された、スペクトル狭窄化を受けている信号に対して、スペクトル狭窄化の特性と逆特性のフィルタ特性で、スペクトル狭窄化による帯域制限を補償する。サンプリング同期化部は、スペクトル狭窄化の補償後の信号から、サンプリングクロックの位相ずれを検出して、サンプリングクロックの位相を調整し、サンプリングタイミングの同期をとる。

(もっと読む)

半導体集積回路装置およびジッタ補正方法

【課題】SERDESがジッタを含むシリアルデータ信号をオーバーサンプリング動作によって受信した場合に、SERDESから出力されたパラレルデータ信号およびリカバリクロック信号に基づいて、もとのシリアルデータ信号を正しく受信できるようにすること。

【解決手段】半導体集積回路装置は、シリアルデータ信号をm倍(mは2のべき乗)オーバーサンプリングするSERDES回路から出力されたNビットの第1のパラレルデータ信号に基づいてKN/mビット(N/mは偶数)の第2のパラレルデータ信号を生成するとともに、SERDES回路から出力された第1のリカバリクロック信号をK分周(Kは2のべき乗)して第2のリカバリクロック信号を生成し、第2のパラレルデータ信号と第2のリカバリクロック信号とを同期して出力するクロックデータリカバリ回路を備えている。

(もっと読む)

GPSジッタ低減装置

【課題】後段側の装置を軽量に設計することのできるGPSジッタ低減装置を得る。

【解決手段】位相比較調整処理部105は、GPS11が出力する1PPSと、出力パルス生成部104から出力される平滑化された1PPSとの位相差をカウントし、位相差目標値と比較して、固定値にて調整を実施する。出力パルス生成部104は、移動平均処理部103の出力と、位相比較調整処理部105の調整値に基づいて平滑化した1PPSを生成する。

(もっと読む)

ラッチ回路、CDR回路、および受信装置

【課題】 消費電力を抑えた受信回路を提供する。

【解決手段】 本発明では、差動信号を差動増幅させる際に、差動入力によって発生する電流を対となる差動出力により遮断することで差動信号をラッチする回路を提供する。該ラッチ回路の適用により、受信信号の差動信号電圧差が小さい場合でも伝送データを受信できる為、増幅用アンプの削減が可能となり、受信装置の消費電力の低減を図ることができる。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

位相同期装置および位相同期方法

【課題】無線回線を介して接続された装置間の位相同期を行うことが可能な位相同期装置を得ること。

【解決手段】マスタ側無線装置3は、マスタ装置1からの受信パケットから、位相同期の基準となるタイミングを抽出し、基準となるタイミングに同期して、スレーブ側無線装置4へパケットを送信するタイミングを決定し、受信パケットをスレーブ側無線装置4へ送信し、スレーブ側無線装置4は、マスタ側無線装置3からの受信パケットから、位相同期の基準となるタイミングを抽出し、抽出したタイミングと自装置内の動作タイミングとを比較して検出した位相差に基づいて、周波数偏差を検出し、位相差および周波数偏差に基づいて、自装置内の動作クロックの周波数を制御し、基準となるタイミングに同期してスレーブ装置2へパケットを送信するタイミングを決定し、受信パケットをスレーブ装置2へ送信する。

(もっと読む)

光パケットスイッチ装置

【課題】伝送路の帯域利用効率を向上できる光パケットスイッチ装置を提供する。

【解決手段】光パケットスイッチ装置10は、光カプラ13と、光スイッチ部12と、光スイッチ制御部14とを備える。光スイッチ制御部14は、光電変換部16と、シリアル/パラレル変換部18と、並び検出部17と、並び換え部19と、フレーム同期部20と、方路検出部24と、制御信号生成部26と、並び検出部17からのフレーム同期パターンの並び情報に基づいて、光スイッチ部12に光スイッチ制御信号を出力するタイミングを調整するタイミング調整部27とを備える。

(もっと読む)

無瞬断切替装置及び方法

【課題】 局内クロックなど共通のクロックを持たないOTN伝送装置において無瞬断切替を可能とする。

【解決手段】 本発明は、送信側の分岐手段で複数の伝送路に分岐された2系統の信号を、それぞれクロック再生及び信号の識別を行い、2つのバッファのそれぞれに、再生された伝送クロックを用いて、識別されたそれぞれの信号を書き込み、再生された2つの伝送クロックから共通クロックを生成し、2つの信号検出手段のそれぞれが、共通クロックを用いて前記バッファに書き込まれた信号をそれぞれ読み出して2つの信号の境界を認識し、2つの信号の境界を比較して、検出された2つの信号の遅延差を調整し、共通クロックを用いて、読み出された2つの信号を切り替える。

(もっと読む)

1 - 20 / 220

[ Back to top ]