Fターム[5L106FF04]の内容

半導体メモリの信頼性技術 (9,959) | 時期 (1,298) | 書込み時 (476)

Fターム[5L106FF04]に分類される特許

1 - 20 / 476

メモリシステム及びそれのブロック複写方法

ホスト装置、システム、及び装置

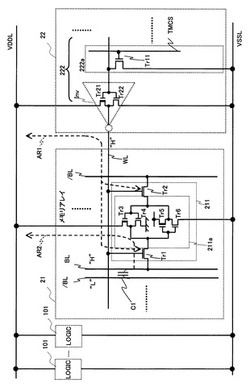

半導体集積回路,および,半導体集積回路の試験方法

【課題】チップ面積,製造コストが増大することなく,試験時における電源電圧降下を抑制する半導体集積回路を提供する。

【解決手段】半導体集積回路は,複数のワード線WLと,複数のワード線と交差する複数のビット線対BL,/BLと,複数のワード線と複数のビット線対との交差部に設けられた複数のメモリセル211とを有するメモリと,電源供給線VDDLからの電源電圧を電源として所定の論理演算を行うLOGIC101と,論理回論の試験制御を行う試験制御回路と,電源供給線VDDLに接続され,電源供給線VDDLからの電源電圧を複数のワード線WLに供給するドライバ部222と,試験制御回路の試験制御実行時に,電源電圧を複数のワード線WLに供給して複数のメモリセル211に電源電圧を供給するチャージ回路222aとを有する。

(もっと読む)

半導体装置

【課題】半導体装置の動作テストのスループットを向上させる。

【解決手段】判定回路112は、2つのメモリバンクBANK(A)、BANK(E)から読み出される計16ビットのテストデータを検査する。検査対象となる16ビットのメモリセルMCにはすべて「H」の書き込みが実行されており、いずれのメモリセルMCに異常がなければそのまま「H」が読み出される。判定回路112は、メモリバンクBANK(A)のテストデータ同士を比較する第1検出回路124とメモリバンクBANK(E)のテストデータ同士を比較する第2検出回路126に加えて、更に、メモリバンクBANK(A)のテストデータとメモリバンクBANK(E)のテストデータを比較する第3検出回路128を備える。

(もっと読む)

半導体装置

【課題】不揮発性記憶回路の出力として「未破壊」を示す第1の論理レベルが期待される場面で、第1及び第2の不揮発性記憶素子の一方に干渉破壊が発生したとしても、第3の不揮発性記憶素子に干渉破壊が生じない限り、不揮発性記憶回路に正しく第1の論理レベルを出力させる。

【解決手段】半導体装置は、第1及び第2の不揮発性記憶素子31,32と、少なくとも1つの第3の不揮発性記憶素子33と、少なくとも1つの第3の不揮発性記憶素子33すべてと、第1及び第2の不揮発性記憶素子31,32のうちの少なくともいずれか一方とが未破壊状態である場合に、未破壊を示す第1の論理レベルを出力する論理演算回路2とを有する不揮発性記憶回路1を備える。

(もっと読む)

不揮発性メモリにおける書き込み欠陥からのデータ保護

【課題】メモリ装置の書き込み欠陥からデータを保護するための方法及びシステムを提供する。

【解決手段】この方法は、データアイテムのセットにわたる冗長情報を計算し、データアイテムを、メモリに記憶するために送信することを含む。冗長情報は、データアイテムがメモリに首尾良く書き込まれるまでの間のみ保持され、次いで、破棄される。データアイテムは、それをメモリに書き込むのに欠陥が生じたとき、冗長情報を使用して回復される。

(もっと読む)

集積回路,試験回路,試験装置,及び試験方法

【課題】記憶部と記憶部の試験を行なう試験部とを備える集積回路の回路規模の増大又は製造コストの増加を低減させる。

【解決手段】記憶部3と、供給される一組のアドレス及びデータを含む試験情報に基づいて前記記憶部3に対する書込及び読出試験を行なう試験部4と、を備え、前記試験部4は、前記試験情報に基づき前記記憶部3への書き込みが行なわれた場合に当該書き込みに用いられた第1書込アドレス及びデータを保持する第1保持部5と、前記試験情報に基づく第2書込アドレス及びデータによる前記記憶部3への書き込みと同時に前記記憶部3の第1読出アドレスから第1読出データを読み出す同時読出に用いる前記第1読出アドレスを、前記第1保持部5に保持された前記第1書込アドレスに基づいて生成する第1生成部6と、前記第1読出データの期待値を、前記第1保持部5に保持された前記第1書込データに基づいて生成する第2生成部7と、を備える。

(もっと読む)

半導体装置

【課題】半導体装置の共通規格に依存してテストモードのリセットを行うのではなく、自律してテストモードのリセットを行う半導体装置が、望まれる。

【解決手段】半導体装置は、内部回路のテストを可能にする第1のテスト部と、第1のテスト部の動作状態を制御可能な第2のテスト部と、第2のテスト部が、第1のテスト部のリセット状態を解除したことに応答して活性化されると共に、第1のテスト部の活性化から所定の期間が経過後に、リセット信号を発生するテストリセット部と、を備えている。第2のテスト部は、テストリセット部が発生するリセット信号を受け付けた場合に、第1のテスト部をリセット状態とする。

(もっと読む)

半導体ディスク寿命監視装置

【課題】不揮発性の半導体ディスクの寿命を監視する半導体ディスク寿命監視装置を提供する。

【解決手段】半導体ディスク5−1〜5−Kの書込み制御を行うファイルシステム3と、当該ファイルシステム3と前記半導体ディスク5−1〜5−Kを接続するインタフェースドライバ4を備え、当該インタフェースドライバ4により書込みが行われる半導体ディスク5−1〜5−Kの寿命を予測する半導体ディスク寿命監視装置1であって、前記ファイルシステム3からの書込みを書込情報として測定する測定部7と、前記測定結果を累積し第1の保存データ32として保存する保存部8と、前記保存した累積書込情報に基づいて、半導体ディスク5−1〜5−Kの寿命を予測する。

(もっと読む)

半導体メモリ装置及びそのテスト方法

【目的】少ない外部端子によって、半導体メモリ装置に構築されているメモリが故障しているか否かの製品出荷時のテスト及びその故障要因を特定することが可能な半導体メモリ装置及びそのテスト方法を提供することを目的とする。

【構成】半導体メモリ装置に構築されているメモリが読出指令に応答したか否かを判定し、メモリが読出指令に対して非応答であった場合にはメモリから読み出されたメモリデータに代えてエラーコードを外部出力する。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】ロールコールテストに要する工数を削減できる半導体記憶装置及びそのテスト方法を提供する。

【解決手段】不良アドレスが格納される不揮発性の記憶素子を備えた半導体記憶装置にロールコールテスト時にマスク用テストモード信号を出力するテスト制御回路とロールコール回路とを備える。ロールコール回路は、アドレス信号と不良アドレスとをビット単位で比較し、その比較結果を出力する。また、ロールコール回路は、マスク用テストモード信号が入力されると、アドレス信号の所望のビットに対応する比較結果をマスクして上記アドレス信号と不良アドレスとが一致していることを示す値を出力すると共に、マスクされていないビットに対するロールコールテストを可能にする。

(もっと読む)

半導体装置およびその制御方法

【課題】テストモード時にテストモードがリセットされるのを防ぐ。

【解決手段】本発明の半導体装置1は、外部から入力されるコマンドに応じて、半導体装置を通常動作モードまたはテストモードで動作させるテスト制御回路220と、通常動作モード時または前記テストモードにおける所定期間外に所定のコマンドが入力されると、テストモードリセット信号TRSTを活性化してテスト制御回路220に入力し、テストモードにおける所定期間内は、所定のコマンドが入力されても、テストモードリセット信号TRSTを活性化しないテストモードリセット制御回路210と、を有する。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

試験装置および試験方法

【課題】アドレスを反転制御することができる。

【解決手段】被試験メモリのアドレスを発生するアドレス発生部と、アドレス発生部により発生されたアドレスをビット反転して被試験メモリに供給するか否かを選択する選択部と、アドレスをビット反転することを選択部が選択した場合にアドレス発生部により発生されたアドレスをビット反転して出力し、アドレスをビット反転しないことを選択部が選択した場合にアドレス発生部により発生されたアドレスをビット反転せずに出力する反転処理部と、反転処理部が出力した反転制御されたアドレス、および、反転処理部が出力したアドレスがビット反転したアドレスであるか否かを示す反転サイクル信号を、被試験メモリへと供給する供給部と、を備える試験装置を提供する。

(もっと読む)

半導体装置

【課題】CRC機能を有し、ライト動作とリード動作を高速に行うことができる半導体装置を提供する。

【解決手段】メモリセルアレイ(メモリセルアレイ11)と、巡回冗長論理符号を生成する誤り検出符号生成回路(誤り検出符号生成回路20)と、メモリセルアレイから読み出されたデータに巡回冗長論理符号を付加してデータ入出力端子を介して半導体装置の外部へリードデータとして出力し、或いは半導体装置の外部からライトデータが入力されて、前記メモリセルアレイへ書き込むデータを誤り検出符号生成回路に出力するデータ入出力部(データ入出力部19)と、メモリセルアレイとデータ入出力部との間に配置されるバス配線(リードライトバス)と、誤り検出符号生成回路とデータ入出力部との間に配置される巡回冗長論理符号配線(CRC信号線)と、を備える。

(もっと読む)

半導体装置

【課題】パリティエラーが発生した場合に適切な処理を実行する。

【解決手段】例えば、アクセスすべきメモリセルMCのアドレスを示すアドレス信号ADD及びアクセスの種別を示すコマンド信号CMDを外部から受け、これらに基づいてメモリセルアレイ11にアクセスするアクセス制御回路20を備える。アクセス制御回路20は、外部から供給される検証信号PRTYに基づいてアドレス信号ADD及びコマンド信号CMDを検証する検証回路90を含む。検証回路90は、アドレス信号ADD又はコマンド信号CMDがエラーであると判定した場合、メモリセルアレイ11へのアクセスを停止する。これにより、いわゆるパリティエラーなどの不良が検出された場合、誤ったコマンドの実行によってデータが破壊されたり、誤ったアドレスにデータを上書きしたりすることがない。

(もっと読む)

半導体装置

【課題】動作速度と駆動能力とのバランスが調整された多入力論理回路を備えた半導体装置を提供する。

【解決手段】3入力以上の入力端子を含み当該3入力以上の入力端子の論理レベルについて論理演算を行う多入力論理回路(XOR_H)を備え、当該多入力論理回路は、それぞれ2つの入力端子を含み当該2つの入力端子の論理レベルに対して前記論理演算を行う複数の2入力論理回路を含み、当該複数の2入力論理回路は、第1の2入力論理回路(XOR_D61)と当該第1の2入力論理回路よりも占有面積が小さく駆動能力が小さい第2の2入力論理回路(XOR_F61、XOR_F62)とを含み、前記第1の2入力論理回路が前記多入力論理回路の最終段として動作し、前記第2の2入力論理回路が前記第1の2入力論理回路に信号を供給する前段回路の少なくとも一部として動作することを特徴とする。

(もっと読む)

復号方法、復号装置および記憶装置

【課題】回路規模を削減した復号装置を得ること。

【解決手段】データと誤り検出符号と最大訂正能力をTビットとする誤り訂正符号とで構成される符号語に基づいて誤り訂正処理を行う復号装置であって、符号語に基づいて前記符号語に基づいて、少なくとも一部の処理でJ(Jは1以上T未満の整数)ビット誤りまでに対応可能な演算器を用いた誤り訂正処理を行う誤り訂正処理部と、誤り訂正処理の開始時に誤り数期待値を初期値I(Iは1以上T未満の整数)とし、設定した誤り数期待値に対応する演算を行うよう誤り訂正処理部を制御し、誤り検出符号に基づき誤り検出部により誤り訂正後のデータに誤りが検出されなかった場合処理を終了し、誤り訂正後のデータに誤りが検出された場合、誤り数期待値を増加させて演算を行うよう誤り訂正処理部を制御する動作を、誤り検出部により誤りが検出されなくなるまでまたは誤り数期待値がTビットとなるまで繰り返す。

(もっと読む)

半導体集積回路

【課題】回路規模の増加を抑制しつつ、テスト時間の短縮を図る半導体集積回路を提供する。

【解決手段】BIST回路1は、アドレス信号を生成するアドレス生成回路1bと、書き込みデータ及び書き込みデータに対応する期待値データを生成するデータ生成回路1aと、メモリを制御するチップイネーブル信号生成回路1cと、メモリの書き込み動作及び読み出し動作を制御する制御信号を生成する制御信号生成回路1dとを有する。メモリブロック化回路2は、複数のメモリを有し、アドレス信号から複数のメモリのうちテスト対象となるメモリのアドレスに対応するアドレス入力信号を生成し、且つ、複数のメモリからテスト対象のメモリを選択するメモリ選択信号を生成するアドレス変換回路Aを有し、メモリ選択信号に基づいて、複数のメモリのうちテスト対象のメモリが出力するデータを選択して出力するメモリ出力選択回路DSと、を有する。

(もっと読む)

半導体装置

【課題】テスト時間を短縮させる。

【解決手段】フラッシュメモリLSI1は、データを記憶する記憶部であって、予め定められたビット数のデータ領域を複数有するフラッシュメモリ部8と、フラッシュメモリ部8から読み出したデータとデータの期待値とが不一致であるビットを示す不良ビットの数が、予め定められた閾値以下であるか否かを、データ領域ごとに判定する判定回路部10と、判定回路部10が判定した判定結果に応じた出力を出力端子(RB#端子)に出力させるRB制御回路部60と、を備える。

(もっと読む)

1 - 20 / 476

[ Back to top ]