Fターム[5M024AA21]の内容

Fターム[5M024AA21]の下位に属するFターム

ノイズ対策 (159)

クロストークの防止 (32)

電源変動対策 (102)

ピーク電流の削減 (33)

スキュー対策 (73)

ラッチアップの防止 (5)

二重選択の防止 (2)

フローティングの防止 (5)

タイミングマージンの拡大 (206)

電圧マージンの拡大 (76)

その他 (154)

Fターム[5M024AA21]に分類される特許

1 - 20 / 21

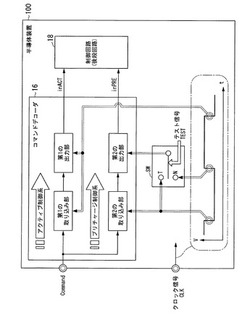

半導体装置及び半導体装置の制御方法

【課題】tRP期間の性能限界試験を実行可能な半導体装置及びその制御方法を提供する。

【解決手段】コマンドデコーダ16は、デバイスのアクティブ動作を認識し保持する第1の取り込み部、第1の取り込み部が出力する第1の出力信号を後段の回路(制御回路18)に出力する第1の出力部、デバイスのインアクティブ動作を認識し保持する第2の取り込み部、第2の取り込み部が出力する第2の出力信号を後段の回路に出力する第2の出力部を含む。第1及び第2の取り込み部は、同期信号(クロック信号CLK)の第1の遷移エッジに対応してCommandを取り込み且つ保持し第1の出力部は、第1の遷移エッジに対応して第1の出力信号(inACT)を出力する。第2の出力部は、テストモード信号が第2の論理であるテストモード動作時に、第1の遷移エッジと逆の遷移エッジである同期信号の第2の遷移エッジに対応して第2の出力信号(inPRE)を出力する。

(もっと読む)

半導体記憶装置

【課題】同一サイクルで複数のデータを読み出すことを前提としない場合においても、振動やノイズに耐性のある半導体記憶装置を提供する。

【解決手段】制御部20は、1受信単位を構成する複数のデータユニットのうち、最後に入力されたデータユニットをメモリアレイ2内の第1のアドレスのメモリセルに格納し、最後に入力されたデータユニットに先行して入力されたデータユニットをメモリアレイ内の、第1のアドレスとは別の第2のアドレスのメモリセルに格納する。第1のアドレスのメモリセルと第2のアドレスのメモリセルとは、メモリアレイ2内では少なくとも行方向および列方向において隣接しない。

(もっと読む)

電源回路

【課題】電源回路を備える装置の低消費電力化と、電源回路が発生させる出力電圧の安定化とを両立させる。

【解決手段】負荷へ供給するための出力電圧を入力電圧に基づいて発生させる一対のMOSトランジスタで構成された電圧発生部と、入力電圧および出力電圧の電圧値を検出する検出部と、検出された電圧値に応じて電圧発生部の駆動を制御する駆動部とを有する電源回路において、負荷の動作状態に応じて駆動部を制御することにより、一対のMOSトランジスタの不感帯の幅を変化させる制御部を有する。

(もっと読む)

時間多重化誤り訂正符号化をサポートするメモリ・トランザクション・バースト動作及びメモリ構成部分

【課題】専用のECCメモリ装置及び専用のECCビット・レーンに対する要求を避けることを可能とする。

【解決手段】誤り訂正符号化データが、バースト・モード転送において、同じデータ・バス線(DQ1−DQn)上でユーザ・データと時間多重化される。モジュール上のメモリ装置はそれぞれ、装置のアドレス指定可能なセグメントに関連した間接的にアドレス指定可能な更なるECCセグメントを含む。時間多重化されたECCデータが、バースト・モード転送において伝送されるアドレス指定データに関連した間接アドレス指定可能セグメントとの間で読み書きされる。さらに2つのタイプのバースト・モードがサポートされ、一方はECCデータを含み、他方は含まない。1つのタイプのメモリ・モジュールがECCシステムも非ECCシステムもサポートし、同じデータにECCを用いるが、同じシステムの別のデータには用いないことを可能にする。

(もっと読む)

半導体装置及びその製造方法

【課題】不良アドレス1ビット分を一対のアンチヒューズ素子に記憶させる半導体装置において、一方のアンチヒューズ素子のみが不良品である場合であっても、不良品として検出できるようにする。

【解決手段】半導体装置10は、それぞれハイレベル及びローレベルのうちのいずれか一方にある一対のアンチヒューズ素子51A,51Bと、これらのうちの少なくとも一方がハイレベルにある場合と、両方がローレベルにある場合とで異なる論理情報を出力するオア回路56と、これらの論理状態が互いに異なる場合と、互いに同一である場合とで異なる論理情報を出力するエクスクルーシブオア回路58とを備えることを特徴とする。

(もっと読む)

アドレスエラー検出装置、アドレスエラー検出方法

【課題】メモリ回路のアドレスデコード部で発生する障害を高確率で検出できる小面積のアドレスエラー検出装置およびアドレスエラー検出方法を提供する。

【解決手段】Xデコーダ103の出力から複数ビットの冗長符号を生成するX符号化器105と、Yデコーダ104の出力から前記冗長符号と同じビット数の冗長符号を出力するY符号化器106と、X符号化器105の出力10とY符号化器106の出力11を各ビット排他的論理和するXOR回路107と、XOR回路107の出力12とアドレス信号1を入力し、誤り検出を行う誤り検出器108と、を備える。X符号化器105とY符号化器106、およびXOR回路107によって、アドレス信号をハミング符号化した冗長部12を生成する。誤り検出器108では、元のアドレス信号と生成された冗長符号に対して検査行列の掛け算を行い、エラーが発生したか否かを検出し、エラー出力3を得る。

(もっと読む)

フューズラッチ回路及びフューズラッチ方法

【課題】フューズ素子の状態を安定して検知して保持することができるフューズラッチ回路を提供する。

【解決手段】動作モードを設定するレジスタに外部から入力されるコマンドに基づいて動作モードを設定することで動作する半導体装置に用いられるものであって、外部コマンドが電源投入後に動作モードレジスタをリセットするコマンド(MRSリセットコマンド)である場合に、フューズ素子の状態読み出しのためのプリチャージ動作を開始する期間tFPREを設定するとともに、tFPRE期間のプリチャージ動作完了後にフューズ素子の状態を読み出して保持する期間tFSETを設定したフューズラッチ回路である。

(もっと読む)

内部電源回路

【課題】バーイン加速試験で内部回路の動作に支障を与えず不良を顕在化することができる参照電圧生成回路を提供する。

【解決手段】参照電圧に基づいて内部電圧を生成する内部電源回路は,通常動作時に第1の電位を有する外部電源が印加されバーイン加速試験時に第1の電位より高い第2の電位を有する外部電源が印加される外部電源端子と,外部電源から参照電圧を生成する参照電圧生成ユニットと,参照電圧に基づいて内部電圧を生成する内部電圧生成ユニットとを有する。そして,参照電圧生成ユニットは,通常動作時において,外部電源の電位に依存しない通常参照電圧を生成し,バーイン加速試験時において,外部電源の電位に依存する第1のバーイン参照電圧と通常参照電圧と同じ電位を有する第2のバーイン参照電圧とを生成する。

(もっと読む)

半導体装置

【課題】製造ばらつきおよび特性変動による影響を抑制することが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1のメモリ回路CM1の記憶データに基づく信号が現われる第1の制御線ML1と、第1の制御線ML1に現われた信号に対する読み出し特性を調整する第1の特性調整回路CL1と、第2のメモリ回路CM1Tの記憶データに基づく信号が現われる第2の制御線MLTと、第2の制御線MLTに現われた信号に対する読み出し特性を調整する第2の特性調整回路CLTと、第2の特性調整回路CLTによる調整結果に基づいて制御信号を生成する制御信号生成回路11とを備え、第1の特性調整回路CL1は、第1の制御線ML1に現われた信号に対する読み出し特性を制御信号に基づいて調整し、第2のメモリ回路CM1Tには、第1のメモリ回路CM1と異なる電源電圧が供給される。

(もっと読む)

半導体記憶装置

【課題】ECC動作時におけるサイクル数及びレジスタ数の増加を抑制し高速動作を可能とした半導体記憶装置を提供する。

【解決手段】パリティ/シンドロームジェネレータ31により読み出しデータに対して、符号生成及び誤り検出を行いパリティビット及びシンドロームを生成し、パリティ/シンドロームレジスタ39に保持する。シンドロームデコーダ32は、シンドロームをデコードし読み出しデータ中の誤りデータを特定するためのエラー信号を出力する。誤り検出ジェネレータ33は、パリティビットに基づいて誤り検出信号を生成する。誤り検出信号に基づいて、アドレス/コマンドジェネレータ22により誤りデータが記憶されたメモリセルのアドレスとライトコマンドが生成され、前記アドレスはフェイルアドレスレジスタ40に保持される。そして、エラー信号に基づいて、データ訂正回路36により読み出しデータ中の誤りデータが訂正される。

(もっと読む)

DRAM装置

【課題】データ保持特性が不良なメモリセルを、冗長メモリセル領域を設けることなく救済するDRAMを提供する。

【解決手段】DRAM10は、データ保持特性が不良なメモリセルの救済アドレスを記憶し、データ読出し及び書込みの際に入力される外部アドレスが、記憶された救済アドレスと一致すると、SA救済判定信号S1を出力するセンスアンプ救済判定回路24と、SA救済判定信号S1が発生すると通常のSA選択信号S3に代えて救済用SA選択信号S2を発生するセンスアンプ制御回路25と、救済用SA選択信号S2が発生すると、対応するセンスアンプを通常よりも高い電源電圧に設定するセンスアンプ部12とを備える。

(もっと読む)

集積回路装置

【課題】マルチポートメモリをテストするのに好適な組み込み自己テスト回路を備える集積回路装置を実現する。

【解決手段】第1のクロック信号が入力される第1のポートと、第2のクロック信号が入力される第2のポートとを有するメモリと;前記第1のクロック信号が入力される第1の信号生成回路と、前記第2のクロック信号が入力される第2の信号生成回路と、前記第1及び第2のクロック信号が入力され、入力されたクロック信号の内のいずれか1つを選択し出力するクロック選択回路と、前記第1又は第2のクロック信号を要求するクロック要求信号を前記クロック選択回路に出力し、前記クロック選択回路により選択され出力されたクロック信号に基づいて動作し、前記第1又は第2の信号生成回路を制御するための制御信号を出力する制御回路とを有する組み込み自己テスト回路と;を備えることを特徴とする集積回路装置。

(もっと読む)

半導体記憶装置

【課題】ウェハ状態でのダイナミックバーインの簡単化とバーイン時間の短縮化を図る。

【解決手段】半導体記憶装置は、ウェハに形成されている。この半導体記憶装置は、複数のメモリセルが配列されたメモリセルアレイ10と、外部からバーインモード設定信号S1を入力する入力パッド20と、信号S1に基づいてメモリセルに対するアドレスを発生するクロック発生回路40及びアドレスカウンタ46,47と、信号S1に基づいてメモリセルに対するデータの書き込み及び読み出しの制御信号/RAS,/CAS,/WEを発生するコマンド発生回路41と、制御信号/RAS,/CAS,/WEにより制御され、アドレスに対応するメモリセルを選択してデータの書き込みを行うアドレスデコーダ50,60及び書き込み回路45と、メモリセルのバーイン状態を外部に出力する出力パッド44とを有している。

(もっと読む)

半導体記憶装置

【課題】チップ面積の増大を抑制しつつ、パッケージング後に発見される不良ビットを正しく救済可能な半導体記憶装置を提供する。

【解決手段】バンク#0〜#7と、バンクごとに設けられた不良救済回路170〜177と、不良アドレスを記憶する不良アドレス記憶回路180〜183と、アクセスが要求されたアドレスと不良アドレスとを比較する比較回路190〜193とを備える。不良アドレス記憶回路180〜183及び比較回路190〜193は、それぞれ2つバンクに対して共通に割り当てられており、これによりチップ面積を縮小することが可能となる。救済可能な不良ビット数については少なくなるが、パッケージング後に発見される不良ビットの数は非常に少なく、このため、不良が発見されないバンクがほとんどであることから、実用上の障害となることはほとんどない。

(もっと読む)

電気ヒューズ回路、メモリ装置及び電子部品

【課題】電気ヒューズへの書き込みの誤動作を防止することができる電気ヒューズ回路及びメモリ装置を提供することを課題とする。

【解決手段】電気ヒューズを構成するキャパシタ(101)と、ライト信号に応じて前記キャパシタの両端子間に電圧を印加することにより、前記キャパシタの絶縁膜を破壊するライト回路(103)と、前記キャパシタの端子に対してプリチャージするプリチャージ回路(121)とを有することを特徴とする電気ヒューズ回路が提供される。

(もっと読む)

半導体メモリおよびシステム

【課題】 ダミー信号線に隣接するリアル信号線およびリアルメモリセルを十分に評価する。ダミー信号線をリアル信号線として使用可能にする。

【解決手段】 半導体メモリは、リアルメモリセルに接続され、リアルドライバにより駆動されるリアル信号線と、リアル信号線の外側に配置され、ダミーメモリセルに接続され、ダミードライバにより駆動されるダミー信号線とを有する。リアルドライバおよびダミードライバは、動作制御回路により生成される共通のタイミング信号に同期してリアル信号線およびダミー信号線を駆動する。これにより、例えば、メモリセルアレイの外周部に位置するリアル信号線も、内側に位置するリアル信号線と同じ条件でストレス評価を実施できる。ダミー信号線は、共通のタイミング信号を用いて駆動され、評価されるため、不良を救済するための冗長信号線として使用できる。

(もっと読む)

内部電源生成回路及びこれらを備えた半導体装置

【課題】 内部電源生成回路において、その出力にオーバードライブ電圧が印加されることで、内部電源生成回路内の電圧設定が変動する。ドライバーの制御節点が動作範囲外に変動し、オーバードライブ終了後に内部電源生成回路が動作しない不感帯が発生するという問題がある。

【解決手段】 内部電源生成回路のドライバーの制御節点電圧を制御する制御回路を設ける。オーバードライブ期間には制御回路により制御節点電圧を制御し、制御節点電圧をドライバー動作可能範囲の適正レベルに設定する。制御節点電圧を適正レベルに設定することで、オーバードライブ終了後には不感帯もなく内部電源生成回路は内部電源電圧を供給できる効果が得られる。この構成とすることで不感帯のない内部電源生成回路及びこれらを備えた高速動作可能な半導体装置が得られる。

(もっと読む)

温度センサ及び区間別温度の検出方法

【課題】区間別温度に応じて温度コードを発生する温度センサ及び区間別温度の検出方法を提供する。

【解決手段】温度検出信号を受けて遅延させる複数個の直列連結された一定遅延セルと、温度検出信号を受けて遅延させる可変遅延セルと、可変遅延セルの出力に応答して一定遅延セルの出力をラッチし、温度コードを発生する区間判別ロジック部と、を備える温度センサである。区間判別ロジック部は、温度変化に応じた可変遅延セルの出力と一定遅延セルの出力それぞれが一致する温度を基準として区間別温度に分け、区間別温度に対応する温度コードを発生する。

(もっと読む)

半導体メモリ装置およびその読み出し方法

【課題】しきい値電圧調整のためのイオン注入工程の追加を行うことなく、データ読み出し時のビット線電圧値を十分大きくする。

【解決手段】各メモリセルMCaが、書き込みトランジスタTW、読み出しトランジスタTR、キャパシタCを有し、書き込みワード線WWLと読み出しワード線RWLのそれぞれが、行方向に並ぶ複数のメモリセルで共有され、ビット線RBLが列方向に並ぶ複数のメモリセルMCsとMCuで共有されている半導体メモリ装置の読み出し時に、ビット線RBLと基準電位GNDとの間に定電流駆動手段TDを設け、読み出し対象の選択メモリセルMCsの読み出しワード線RWLsに電源電圧Vccを印加し、非選択メモリセルMCuの読み出しワード線RWLuに0[V]を印加し、かつ、定電流駆動手段TDをオンさせる。

(もっと読む)

半導体メモリ装置のデータストローブ信号発生回路

【課題】CASレイテンシ信号を用いてtCKの変化に従い各tCKに対するtDQSS特性をそれぞれ調節するようにし、全てのtCKに対し十分なtDQSSマージンを確保する。

【解決手段】本発明に係る半導体メモリ装置のデータストローブ信号発生回路は、複数個のCASレイテンシ信号のそれぞれにより制御され内部クロック信号を遅延する複数個の内部クロック遅延部と、入力データをラッチするためのデータラッチ制御信号及び前記複数個の内部クロック遅延部の出力の論理演算を行なう選択制御部と、前記選択制御部の出力を用いて所定のパルスを有するデータストローブ信号を発生するパルス発生部とを含んで構成することを特徴とする。

(もっと読む)

1 - 20 / 21

[ Back to top ]