Fターム[5M024AA63]の内容

Fターム[5M024AA63]に分類される特許

1 - 20 / 27

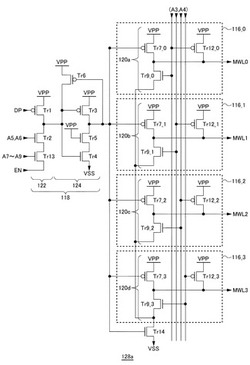

半導体装置

【課題】ワード線の選択回路のサイズを縮小することにより、半導体装置のサイズを縮小する。

【解決手段】メインワード線は、複数のグループに分類され、メインワードドライバはアドレス情報にしたがってメインワード線を選択する。4本のメインワード線MWL0〜MWL3から構成される1つのグループが、1つのレベルシフタ118を共有する。アドレス情報は、グループ選択のための第1アドレスとメインワード線選択のための第2アドレスを含む。メインワードドライバは、第1アドレスにしたがって、第1グループ選択回路や第2グループ選択回路128aを選択し、選択された第2グループ選択回路128aのレベルシフタ118は活性電位(ローレベル)を出力する。そして、選択された第2グループ選択回路128aに所属する複数のメインワード線MWL0〜MWL3のうちの1本が第2アドレスA3,A4により選択される。

(もっと読む)

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】半導体装置は、ビット線と、二以上のワード線と、トランジスタおよびキャパシタからなるサブメモリセルを二以上有するメモリセルと、を有する。トランジスタのソースまたはドレインの一方がビット線と接続し、トランジスタのソースまたはドレインの他方がキャパシタと接続し、トランジスタのゲートがワード線の一と接続し、キャパシタの容量が各サブメモリセルで異なる。

(もっと読む)

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

半導体装置

【課題】回路規模が小さい階層型DRAMを提供すること。

【解決手段】それぞれが複数のメモリセルと、前記メモリセルに接続されたビット線と、前記ビット線をプリチャージするプリチャージ回路とを有し、行方向及び列方向にマトリクス状に配置された複数のサブアレイと、前記列方向に沿って延設され、前記サブアレイの列を選択するための列選択信号線と、前記行方向に沿って延設され、前記サブアレイの行を選択するためのメインワード線と、前記プリチャージ回路に対してプリチャージ信号を供給するプリチャージ信号線と、を備え、前記行方向または前記列方向に並べて配置された少なくとも2つの前記サブアレイが前記プリチャージ信号に応じて同一論理で制御される半導体装置。

(もっと読む)

半導体装置及び情報処理システム

【課題】ビット線構成が階層化されたメモリセルアレイにおいて、回路規模が小さくチップ面積の増加及びタイミングスキューを抑制可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ビット線構成がローカルビット線LBLとグローバルビット線GBLとに階層化され、ローカルビット線LBLとグローバルビット線GBLとの間の接続を制御する階層スイッチSWを備えている。階層スイッチSWの制御のため、ローカルスイッチ制御線LSLとメインスイッチ制御線MSLが配置される。ローカルスイッチ制御線LSLはローカルスイッチドライバLSDにより駆動され、メインスイッチ制御線MSLはメインスイッチドライバMSDにより選択的に活性化される。メモリセルアレイの規模が大きくなっても、ローカルスイッチドライバLSDとメインスイッチドライバMSDの配置によるレイアウト面積の増大及びタイミングスキューを抑制することができる。

(もっと読む)

半導体装置及びその制御方法

【課題】ビット線構成が階層化されたメモリセルアレイのプリチャージ動作時に配線レイアウトに起因するプリチャージ速度の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ローカルビット線LBLとグローバルビット線GBLとに階層化され、階層スイッチLSWによりローカルビット線LBLとグローバルビット線GBLとの間の電気的接続が制御され、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。プリチャージ動作時には、階層スイッチLSWが導通している状態で、グローバルビット線GBLの側のプリチャージ回路(不図示)によりプリチャージ電圧がグローバルビット線GBLに供給される。所定時間が経過してローカルビット線LBLの電位がプリチャージ電圧に収束すると、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。

(もっと読む)

半導体装置

【課題】 半導体装置のレイアウト面積を大きくすることなく、内部電源回路の電流供給能力の向上を可能にする。

【解決手段】 半導体装置は、主領域12と、第1の方向に沿って主領域に形成された複数の第1の電源配線15と、第1の電源配線と交差しかつ電気的に接続されるように第2の方向に沿って主領域に形成された複数の第2の電源配線16と、第1の方向に関して主領域の一方の側に隣接する第1の隣接領域13に設けられ、第1の電源配線の一端にそれぞれ接続された第1の内部電源回路17と、第2の方向に関して主領域の一方の側に隣接する第2の隣接領域14に設けられ、複数の第2の電源配線のうち最も第1の電源配線の他端に近い電源配線の一端に接続された第2の内部電源回路18と、を備える。

(もっと読む)

半導体装置

【課題】 レイアウト面積の増加を抑制しつつ、更なる高速動作を可能にする半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板141と、半導体基板中に埋め込まれ、かつ第1の方向に延伸して形成された第1のローカルビット線501と、半導体基板上に形成された第1の絶縁層142と、第1の絶縁層上に形成された第1のグローバルビット線GBLと、第1の絶縁層中に形成され、第1のローカルビット線の一端と第1のグローバルビット線とを接続する第1の経路502と、第1の絶縁層中に形成され、第1のローカルビット線の他端と第1のグローバルビット線とを接続する第2の経路503とを備えている。

(もっと読む)

情報処理方法、積層型集積回路メモリ

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる。

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置及びこれを備えるシステム

【課題】ビット線が階層化された半導体装置において、端部に位置するメモリマットを他のメモリマットと同様に扱えるよう構成する。

【解決手段】グローバルビット線GBL及びそれより短いダミーグローバルビット線DGBLと、これらの電位差を増幅するセンスアンプSAと、階層スイッチSWを介してグローバルビット線GBLに接続されるローカルビット線LBLをそれぞれ含む複数のメモリブロックMBと、ダミー階層スイッチDSWを介してダミーグローバルビット線DGBLに接続されるLBLと同じ長さのダミーローカルビット線DLBLを含むダミーメモリブロックDMBと、階層スイッチSWのいずれか及びダミー階層スイッチDSWを活性化させる制御回路100とを備える。これにより、端部に位置するメモリマットと他のメモリマットとを同じ記憶容量とすることが可能となる。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】階層化メモリセルアレイにおける信号電圧の判定タイミングを適切に制御して消費電力を低減可能な半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置は、メモリセルMCの信号を伝送する第1のビット線LBLと、第1のビット線LBLの伝送信号を増幅して増幅素子を含む第1のセンスアンプ21と、第1のビット線LBLと選択的に接続される第2のビット線GBLと、第2のビット線の信号電圧のレベルを判定する第2のセンスアンプ22と、第1のセンスアンプ21の増幅動作中に信号電圧の判定タイミングを制御するセンスアンプ制御回路としてのレプリカ回路14を備えている。この判定タイミングは、通常動作時には第1のタイミングに設定され、リフレッシュ動作時には第1のタイミングより遅延した第2のタイミングに設定され、リフレッシュの間隔を長くして消費電力を低減することができる。

(もっと読む)

電子回路装置

【課題】

同一の機能を実行する構成要素を複数個積層して構成した電子回路装置において、各構成要素に構成要素を特定する情報を予め持たせることなく、制御要素が積層された複数の構成要素から任意の構成要素を選択することを可能とする。

【解決手段】

各構成要素に順序論理回路を設け、前段に積層された構成要素、或いは制御要素から送信された制御データにより順序論理回路の状態を変更することにより、制御対象の構成要素の状態を制御要素による選択を受け付ける状態に設定する。

(もっと読む)

メモリアーキテクチャ

【課題】複数の外部ポートを有する多重平面階層構造のメモリアーキテクチャを提供する。

【解決手段】多重階層平面を有するマルチポートメモリアーキテクチャは、典型的には最下位階層平面において1ポートメモリセルを有している。その上の各階層平面におけるメモリブロックは、それぞれすぐ下の階層平面におけるメモリブロックによって構成されている。多重階層平面を有する所定のマルチポートメモリアーキテクチャによって、チップ上の所要面積が低減される。階層平面におけるメモリブロックは要求に応じてメモリブロックマトリクス、交換ネットワーク、バンク技術構成等として配置することができる。このようにして、適用事例ごとに最大限の設計自由度が得られる。さらにこのマルチポートメモリアーキテクチャは、アクセスコンフリクトを処理するための回路を有している。

(もっと読む)

バンクタイプ半導体メモリ装置

【課題】本発明は、半導体メモリ装置に関し、より詳しくは、複数のサブバンクからなる複数のバンクを含む半導体メモリ装置に関する。

【解決手段】本発明の半導体メモリ装置 は、データ信号ラインの断絶なしに連続的にスタックされた少なくとも二つのサブバンクからなるスタックバンク構造体、及びスタックバンク構造体の一側に配置され、サブバンクのコラム関連信号を同時に制御するコントロールブロックを含む。他の発明は、一定間隔をおいて複数配置され、複数のサブバンクからなるスタックバンク構造体と、スタックバンク構造体を構成するサブバンクのコラム関連信号を全部制御するコントロールブロックと、スタックバンク構造体間に配置される複数のグローバル入出力ラインとを含む。

(もっと読む)

半導体メモリ装置

【課題】本発明は、面積マージンを増加させる半導体メモリ装置を提供する。

【解決手段】本発明の半導体メモリ装置は、複数のメモリセルを含む第1のメモリセル領域及び複数のメモリセルを含み、第1のメモリセル領域に隣接して配置される第2のメモリセル領域と、第1のメモリセル領域及び第2のメモリセル領域とデータ入出力動作を行うサブ−ローカルデータバスと、及び、第1のメモリセル領域と第2のメモリセル領域との間に配置され、サブ−ローカルデータバスとデータ入出力動作を行い、それぞれ第1のデータ入出力センスアンプと第2のデータ入出力センスアンプとに接続される第1のローカルデータバス及び第2のローカルデータバスを含む。

(もっと読む)

半導体記憶装置、および半導体記憶装置のデータ出力方法

【課題】リードライトアンプ部分への入力信号の本数を減少させることにより、チップサイズを小さくした半導体記憶装置を提供する。

【解決手段】4ビットプリフェッチ動作のDDRにおいて、カラムアドレスの下位2ビットの信号Y0/Y1で分離された4つのデータD0〜D3をデータバスRWBSに転送する際に、DQ部10から先に出力される2データ(前サイクルのデータ)と後に出力される2データ(後サイクルのデータ)の判定を、データセレクタ(13A、13B)の部分においてY1信号のみにより行う。また、RWBS転送後のデータに対し、DQ部10のY0セレクタ&RWBSセレクタ14においてY0信号により順番を切り替える。

(もっと読む)

1 - 20 / 27

[ Back to top ]