Fターム[5M024JJ02]の内容

Fターム[5M024JJ02]の下位に属するFターム

DDR (373)

データストローブ信号を用いるもの (93)

Fターム[5M024JJ02]に分類される特許

1 - 20 / 316

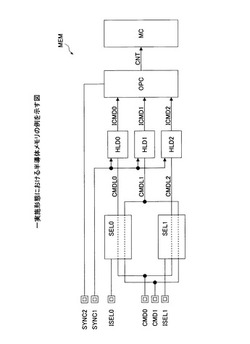

半導体メモリ、半導体メモリの動作方法、システムおよび半導体メモリの製造方法

【課題】少ない数のコマンド端子を用いて、半導体メモリを効率よくアクセスする。

【解決手段】半導体メモリMEMは、選択信号に応じて選択される1つが動作し、複数の第1コマンド端子CMD0、CMD1にそれぞれ供給される複数の第1コマンド信号を受け、受けた第1コマンド信号を出力する複数の第1選択部SEL0、SEL1と、第1選択部の出力に接続され、第1コマンド端子の数より多く、少なくとも1つが第1選択部の複数に共通に接続され、第1選択部の1つから出力される第1コマンド信号を、第1同期信号SYNC1に応答して保持し、第2コマンド信号として出力する複数の保持部HLD0、HLD1、HLD2と、第2コマンド信号に応じた動作制御信号CNTを、第1同期信号に比べて発生頻度が低い第2同期信号SYNC2に応答して出力する動作制御部OPCと、動作制御信号に応じてアクセスされるメモリセルMCとを有している。

(もっと読む)

アドレスデコーディング方法とこれを用いた半導体メモリ装置

【課題】半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる半導体メモリ装置を提供する。

【解決手段】読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成するストローブクロック生成部10と、ストローブクロックの第1レベルに応答してアドレスをラッチし、ストローブクロックの第2レベルに応答して、アドレスをデコーディングして内部アドレスを生成する内部アドレス生成部20と、内部アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する出力イネーブル信号生成部30と、を備える。

(もっと読む)

メモリインターフェースおよび画像処理装置

【課題】 フレームメモリにすでに書き込まれた直前のフレームを構成する画素の画素値を示すデータの出力を開始するまでの遅延時間の短縮化が図られたメモリ制御回路、および回路規模の削減化が図られた画像処理装置を提供する。

【解決手段】 垂直同期信号VSYNCの立ち下がりエッジをSDRAMコントローラ22で検知して、初期アドレスにクリアされたアドレス信号A,読み出しを指示するコマンドCを生成してSDRAM10に供給し、SDRAM10から所定の範囲の過去データを先読みして読み出し用FIFO23に格納しておき、現在データの入力が開始された後に読み出し用FIFO23から読み出して出力する。

(もっと読む)

半導体装置

【課題】小規模な論理回路によって基準レイテンシとオフセットレイテンシを用いた演算を行う。

【解決手段】例えば、基準レイテンシCLの値を示す複数のビットA0〜A3のそれぞれと、オフセットレイテンシSRLの値を示す複数のビットC0〜C2のそれぞれと、を論理合成して複数の制御信号E0〜E3を生成する論理回路100と、複数の制御信号E0〜E3をデコードして複数の制御信号ULPCL4〜ULPCL15を生成する論理回路200とを備える。本発明によれば、基準レイテンシCLの値とオフセットレイテンシSRLの値をデコードする前に演算していることから、より小規模な論理回路によって調整レイテンシULPCLを算出することが可能となる。

(もっと読む)

マルチバンクメモリデバイスのメモリバスアウトプットドライバ及びそのための方法

【課題】マルチバンク構成のメモリにおいて、選択バンクの読み出しデータを低面積、低電力、高速に出力可能な方法を提供する。

【解決手段】第1バス128に結合された第1トライステートデバイスにおいて、センスアンプの第1センスアウトプットおよび第2センスアウトプットを受け取ることと、第2バス130に結合された第2トライステートデバイスにおいて、センスアンプの第1センスアウトプットおよび第2センスアウトプットを受け取ることと、バス選択インプットに応じて第1バスまたは第2バスを駆動するために第1トライステートデバイスおよび第2トライステートデバイスの1つを選択的にアクティブにする。

(もっと読む)

半導体装置

【課題】積層され、貫通電極で相互に接続された複数の半導体チップの出力インピーダンスのバラツキを抑える。

【解決手段】半導体装置100は、第1の被制御チップ110と、第1の被制御チップ110を制御する制御チップ120とを備える。第1の被制御チップ110は、第1の出力回路と同一の構成を持つ第1のレプリカ出力回路111と、第1のレプリカ出力回路111に接続される第1のZQ端子112と、第1のZQ端子に接続される第1の貫通電極113と、第1のレプリカ出力回路111のインピーダンスを設定する第1の制御回路114と、を含む。制御チップ120は、第1の貫通電極113に接続される第2のZQ端子121と、第2のZQ端子121の電圧と参照電圧Vrefとを比較する比較回路122と、比較回路122からの比較結果に応じて処理を行う第2の制御回路123と、を含む。

(もっと読む)

完全に独立のパーシャルアレイリフレッシュ機能を有するダイナミックランダムアクセスメモリ

【課題】独立パーシャルアレイリフレッシュ機能を有する改善されたダイナミックランダムアクセスメモリ(DRAM)を提供する。

【解決手段】DRAMデバイスが、複数のメモリサブブロックを有する。各サブブロックは、複数のワード線を有し、これらのワード線に、複数のデータ記憶セルが接続される。パーシャルアレイセルフリフレッシュ(PASR)構成セッティングが、独立に作られる。PASRセッティングに従って、メモリサブブロックが、リフレッシュのためにアドレッシングされる。PASRセッティングは、メモリコントローラによって作られる。サブブロックアドレスのすべての種類の組合せを選択することができる。したがって、メモリサブブロックは、完全に独立にリフレッシュされる。データ保持に関するユーザ選択可能メモリアレイは、特に低消費電力モバイル応用の有効なメモリ制御プログラミングをもたらす。

(もっと読む)

メモリ装置の動作方法及び該方法を行うための装置

【課題】制御ピンを通じて入力された1つの制御信号のレベルによって命令をイシューすることができるメモリ装置の動作方法及び該方法を行う装置を提供する。

【解決手段】複数のクロックサイクルで入力されるODT入力のHとLの組み合わせに応じて、ODTコントローラによる終端抵抗の抵抗値変更、ODT回路のターンオフまたはターンオンを実行するか、パワーダウン中でも必要とされるメモリのリフレッシュ動作を実行するか等のメモリの動作制御を行う。

(もっと読む)

半導体装置及びデータ処理システム

【課題】外部電圧VDDの変動に伴うレイテンシカウンタのラッチマージンの低下を抑制する。

【解決手段】半導体装置10は、外部電圧VDDで動作する第1の回路と、外部電圧VDDよりも低い内部電圧VPERIで動作する第2の回路とを有するデータ入出力回路78と、外部クロック信号CK,/CKに基づき、データ入出力回路78の動作タイミングを制御する内部クロック信号LCLKOETを生成するDLL回路23とを備え、DLL回路23は、内部電圧VPERIで動作する回路を含む一方、外部電圧VDDで動作する回路を含まないことを特徴とする。

(もっと読む)

半導体装置及びデータ処理システム

【課題】外部電圧VDDの変動に伴うレイテンシカウンタのラッチマージンの低下を抑制する。

【解決手段】半導体装置は、外部クロック信号に基づいて生成される内部クロック信号LCLKOEFTと、外部から供給されるリードコマンドに応じて生成される内部リードコマンドMDRDTとを受け、内部リードコマンドDRCを生成するレイテンシカウンタ55を備え、レイテンシカウンタ55は、出力ゲート信号COT0〜COT7のそれぞれを遅延させることにより入力ゲート信号CIT0〜CIT7を生成する遅延回路部200を有し、遅延回路部200は、外部電圧VDDで動作する遅延素子と、内部電圧VPERIで動作する遅延素子とを含む。

(もっと読む)

ダイナミックデータストローブ検出

【課題】データストローブ信号がデータの捕獲について有効であるときを決定するための技術を提供する。

【解決手段】一実施形態において、データストローブ信号に基づきメモリからデータを捕獲するための初期時間値を決定するように構成されたメモリインターフェイス回路を備えた装置が開示される。ある実施形態では、メモリインターフェイス回路は、メモリから既知の値を読み取ることによりこの初期時間値を決定する。一実施形態では、メモリインターフェイス回路は、更に、データを捕獲するための調整された時間値を決定するように構成され、ここで、メモリインターフェイス回路は、初期時間値を使用してデータストローブ信号をサンプリングすることによりその調整された時間値を決定するように構成される。

(もっと読む)

半導体装置

【課題】外部電圧変動によるコマンドラッチミスの発生を抑制することができる半導体装置を提供する。

【解決手段】半導体装置600は、入力される第1のパルス信号1shot.CMDに由来する第1の入力信号と、入力される第2のパルス信号Out.CLKに由来する第2の入力信号と、が入力されるラッチ回路612と、ラッチ回路の出力を第2のパルス信号に依存するタイミングで後段へ出力する出力回路613と、第2のパルス信号に基づいて、第1の入力信号のパルス幅を第1のパルス信号のパルス幅よりも大きくしてラッチ回路へ供給するか、または、第2の入力信号のパルス幅を第2のパルス信号のパルス幅よりも大きくしてラッチ回路へ供給する前処理回路611とを備える。

(もっと読む)

DRAMアクセス装置及びDRAMアクセス方法

【課題】最終位相調整用のデータをDRAMに書き込む前に、その確実な書き込み動作を保証する。

【解決手段】DRAMに接続するためのストローブ用及びデータ用の双方向I/Oバッファ10,11と、当該双方向I/Oバッファ10,11より受信した信号を受け取るデータ受信部12と、DRAMのストローブ信号とデータ信号との間の位相差を調整する位相調整部13,14と、メモリコントローラ15によりDRAMに対して書き込み動作及び読み出し動作を伴う最終位相調整を始める前に確実な書き込み動作を保証するための暫定位相値を決定する暫定位相調整部20とを設ける。

(もっと読む)

集積回路チップ、これを含むシステム及び動作方法、メモリ及びメモリシステム

【課題】スレーブチップに動作命令を印加するマスタチップがスレーブチップの動作速度と関連した情報を取得するようにし、最適のレイテンシ設定が可能なようにする集積回路チップを提供すること。

【解決手段】第1のチップと第2のチップとを備え、前記第1のチップが前記第2のチップにトレーニング命令を印加すれば、前記第2のチップは、前記トレーニング命令に対応する動作の動作所要時間を前記第1のチップに報知することを特徴とする。

(もっと読む)

情報処理システム

【課題】セルフリフレッシュモードからの復帰時間を高速化する。

【解決手段】例えば、コントローラ50は、半導体装置10に対してセルフリフレッシュコマンドSREを発行することによってセルフリフレッシュモードにエントリさせる。半導体装置10は、セルフリフレッシュモードにエントリすると、オシレータ150を用いてリフレッシュ動作を周期的に実行する。セルフリフレッシュモードにおいて1回のリフレッシュ動作に要する時間をオートリフレッシュの1/4に短縮するとともに、リフレッシュ動作の実行頻度を4倍とする。これにより、セルフリフレッシュイグジットコマンドSRXを発行した後、ロウ系のコマンドの投入が禁止される期間を短縮することが可能となる。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

メモリ回路システム及び方法

【課題】メモリ回路システムを提供する。

【解決手段】インタフェース回路104が複数のメモリ回路102及びシステム106と通信できる。使用時、インタフェース回路は、メモリ回路の命令スケジューリングにおける制約を減少させるため、メモリ回路及びシステムをインターフェースするように動作する。別の実施形態では、インタフェース回路が、複数のメモリ回路、及びシステムと通信することができる。使用時、インタフェース回路は、システムとメモリ回路との間で伝達される命令に関連付けられているアドレスを変換するように動作する。更に別の実施形態では、少なくとも1つのメモリ積層体が、複数のDRAM集積回路を備えている。DRAM集積回路とホストシステムの間で1つ以上の物理パラメータを変換する目的で、ホストシステムに結合されたバッファ回路を使用して、ホストシステムにメモリ積層体をインターフェースする。

(もっと読む)

半導体メモリ、システムおよび半導体メモリの動作方法

【課題】 電源電圧が変動することを防止しながら、電圧生成部による電源電圧の生成能力を最小限にし、半導体メモリの消費電力を削減する。

【解決手段】 第1電圧生成部は、メモリセルに接続される第1信号線を選択する第1選択部に供給する第1電源電圧を生成する。第2電圧生成部は、メモリセルに接続される第2信号線を選択するために、第1選択部が動作を開始した後に動作する第2選択部に供給する第2電源電圧を起動信号の活性化中に生成する。スイッチは、短絡信号の活性化中に、第1電源線と第2電源線とを短絡する。第1制御部は、アクセス要求に応答して、起動信号を活性化し、短絡信号の非活性化に応答して起動信号を非活性化する。第2制御部は、起動信号の活性化から所定時間後に短絡信号を活性化し、アクセス要求に基づくアクセス動作の完了後に、短絡信号を非活性化する。

(もっと読む)

半導体装置

【課題】オーバドライブ時間を変更せずに、センスアンプ列の過昇圧の発生を回避する。

【解決手段】半導体装置は、複数のセンスアンプ列に対応するオーバドライブ配線23−1と、オーバドライブ配線に一端が接続される第1の容量素子61−1と、オーバドライブ配線に第1のスイッチ62−1を介して一端が接続される第2の容量素子61−2と、オーバドライブ配線に対する第1の電圧の供給及び供給停止を制御する第2のスイッチ27−1と、複数のセンスアンプ列の活性化を制御するとともに、第1のスイッチ及び第2のスイッチを制御する制御部とを備える。

(もっと読む)

エラー訂正回路を具備したオンチップ・データ・スクラビング装置及び方法

【課題】エラー訂正回路を具備したオンチップ・データ・スクラビング装置及び方法を提供する。

【解決手段】半導体メモリ装置のチップ内部でデータ・スクラビングを行うエラー訂正回路を具備したオンチップ・データ・スクラビング装置及び方法であって、該メモリ装置のリフレッシュ方法は、メモリ装置の対応する部分について、スクラビングのない少なくとも1つのリフレッシュを行う段階と、メモリ装置の対応する部分について、スクラビングを有する少なくとも1つのリフレッシュを行う段階と、を含む。

(もっと読む)

1 - 20 / 316

[ Back to top ]