Fターム[5M024LL01]の内容

Fターム[5M024LL01]に分類される特許

1 - 20 / 330

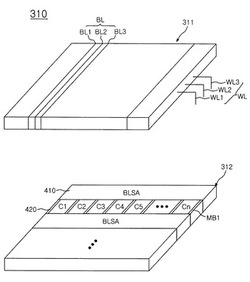

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

メモリにおけるピーク電力管理のためのメカニズム

【課題】メモリにおけるピーク消費電力管理のためのメカニズムを提供する。

【解決手段】サブ・アレイ・ブロックを含むメモリ・ストレージ・アレイにおけるピーク電力を管理するためのメカニズムが、サブ・アレイ・ブロックの各々に対するワードライン信号の起動を互い違いにすることにより、読み出し動作及び書き込み動作と関連したピーク電流を削減することができる。具体的には、1つのサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの書き込みワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、各々のサブ・アレイ・ブロックに対してワードライン信号を生成することができる。さらに、ワードライン・ユニットは、所与のサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの読み出しワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、ワードライン信号を生成することができる。

(もっと読む)

マルチバンクメモリデバイスのメモリバスアウトプットドライバ及びそのための方法

【課題】マルチバンク構成のメモリにおいて、選択バンクの読み出しデータを低面積、低電力、高速に出力可能な方法を提供する。

【解決手段】第1バス128に結合された第1トライステートデバイスにおいて、センスアンプの第1センスアウトプットおよび第2センスアウトプットを受け取ることと、第2バス130に結合された第2トライステートデバイスにおいて、センスアンプの第1センスアウトプットおよび第2センスアウトプットを受け取ることと、バス選択インプットに応じて第1バスまたは第2バスを駆動するために第1トライステートデバイスおよび第2トライステートデバイスの1つを選択的にアクティブにする。

(もっと読む)

半導体記憶装置

【課題】オープンビット線方式における電源ノイズの影響を低減した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は,列方向に両側に延びる一対のビット線に接続するセンスアンプを列方向に直交する行方向に複数配置したセンスアンプ群が列方向に複数配置され,列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,複数のビット線及び複数の未使用ビット線と複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,メモリセルアレイの列方向の一端に配置され,複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,未使用ビット線は内部電源配線に接続されている。

(もっと読む)

完全に独立のパーシャルアレイリフレッシュ機能を有するダイナミックランダムアクセスメモリ

【課題】独立パーシャルアレイリフレッシュ機能を有する改善されたダイナミックランダムアクセスメモリ(DRAM)を提供する。

【解決手段】DRAMデバイスが、複数のメモリサブブロックを有する。各サブブロックは、複数のワード線を有し、これらのワード線に、複数のデータ記憶セルが接続される。パーシャルアレイセルフリフレッシュ(PASR)構成セッティングが、独立に作られる。PASRセッティングに従って、メモリサブブロックが、リフレッシュのためにアドレッシングされる。PASRセッティングは、メモリコントローラによって作られる。サブブロックアドレスのすべての種類の組合せを選択することができる。したがって、メモリサブブロックは、完全に独立にリフレッシュされる。データ保持に関するユーザ選択可能メモリアレイは、特に低消費電力モバイル応用の有効なメモリ制御プログラミングをもたらす。

(もっと読む)

半導体装置

【課題】パリティエラーが発生した場合に適切な処理を実行する。

【解決手段】例えば、アドレス信号ADD及びコマンド信号CMDに基づいてメモリセルアレイ11を活性化させるアクティブ制御回路230と、外部から供給される検証信号PRTYに基づいてアドレス信号ADD及びコマンド信号CMDを検証することによりパリティエラー信号PERRを生成する検証回路90と、パリティエラー信号PERRがフェイルを示した場合、活性化されているメモリセルアレイ11を所定時間経過後に非活性化させるエラー処理回路120を備える。これにより、パリティエラーが発生した場合であっても、既に発行されたコマンドを正しく実行した後にメモリセルアレイを非活性化させることができる。

(もっと読む)

バッファメモリ装置及び通信装置

【課題】 リフレッシュの有無をリアルタイムに判定でき、しかも、優先データを扱うことが可能なパケットバッファ装置を提供する。

【解決手段】 対象としているパケットバッファ装置は、メモリ空間を複数のブロックに分け、メモリブロック単位で書込みデータのリフレッシュを行うものである。そして、メモリブロック毎に、書込みデータ数と読出しデータ数との一致、不一致を判定する一致・不一致判定手段と、書込みデータ数と読出しデータ数とが一致しているメモリブロックのリフレッシュを禁止し、書込みデータ数と読出しデータ数とが不一致のメモリブロックのリフレッシュを許可するリフレッシュ制御手段とを備えることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】比較的小振幅な信号が伝送される第1の信号線対で発生するカップリングノイズを低減しつつ、該第1の信号線対と直交する方向に異なる配線層で配置される、第1の信号線対よりも振幅が大きい信号が伝送される第2の信号線毎の信号遅延量の差異を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリアレイ上で配線される第1の振幅信号が伝送される複数の第1の信号線対と、該第1の信号線対と直交する方向に異なる配線層で配置される複数の第2の信号線とを有する。第1の信号線対は、メモリマットの列毎に配置され、メモリマットの列方向において、それぞれ所定の一定間隔で交差される。また、第1の信号線対の交差部位は第2の信号線の配線方向におけるメモリマットの列毎にずらして配置される。

(もっと読む)

DDR型半導体記憶装置

【課題】アドレス入力バッファによる電力消費を低減可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、アドレス端子に接続される第1入力バッファと、データ入力の基準となるクロック信号を受けるクロック端子と、前記クロック端子に接続されるクロック信号を受ける第2入力バッファとを具備する。前記第1入力バッファは、ライトコマンドが入力された場合に活性化され、ライトコマンドが入力された後、前記クロック信号の所定サイクル後に非活性化される。

(もっと読む)

半導体装置

【課題】データ処理性能の低下を防止可能な半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置は、インターフェイス回路105−1,105−2と、インターフェイス回路105−1に第1のデータバスを介して結合されると共に、インターフェイス回路105−1から出力される第1のアクセス制御信号に結合されたメモリコア106−1と、インターフェイス回路105−2に第2のデータバスを介して結合されたメモリコア106−2と、第1のアクセス制御信号、又は、インターフェイス回路105−2から出力される第2のアクセス制御信号を選択的にメモリコア106−2に結合させる選択回路107−1と、を備える。

(もっと読む)

フロントエンドプリチャージを有するメモリ

【課題】デジタルメモリデバイスの動作電力を低減する。

【解決手段】複数のメモリセル(713)を含むデジタルメモリデバイス(2904)は、一組のメモリセル(713)上で動作を実行するようにコマンドを受信し、一組のメモリセル(713)は、デバイス(2904)全体よりも含有するメモリセルが少なく、デバイス(2904)は、受信コマンドに応答して、一組のメモリセル(713)に関連する一組のビットライン(709)のみを、動作のフロントエンドに選択的にプリチャージすることを含む動作を実行する、デジタルメモリ(2904)を動作させる方法、装置、およびシステム(2900)。

(もっと読む)

ワード線分割回路、及び記憶装置

【課題】回路構成が簡略化され、安定して動作可能なワード線分割回路を提供する。また、回路構成が簡略化され、安定して動作可能な記憶装置を提供する。

【解決手段】ワード線と、サブワード線との間に、リーク電流が極めて低減されたトランジスタを直列に接続し、ワード線分割回路を構成すればよい。当該トランジスタには、チャネルが形成される半導体層に酸化物半導体を含むトランジスタを適用できる。また、このような回路構成が簡略化されたワード線分割回路を、記憶装置に適用すればよい。

(もっと読む)

半導体装置

【課題】オーバドライブ時間を変更せずに、センスアンプ列の過昇圧の発生を回避する。

【解決手段】半導体装置は、複数のセンスアンプ列に対応するオーバドライブ配線23−1と、オーバドライブ配線に一端が接続される第1の容量素子61−1と、オーバドライブ配線に第1のスイッチ62−1を介して一端が接続される第2の容量素子61−2と、オーバドライブ配線に対する第1の電圧の供給及び供給停止を制御する第2のスイッチ27−1と、複数のセンスアンプ列の活性化を制御するとともに、第1のスイッチ及び第2のスイッチを制御する制御部とを備える。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置

【課題】半導体装置のアンプ領域は、回路素子のサイズよりも各種の配線のための領域が広い状態となっており、半導体装置のチップサイズを削減する際の妨げになっている。そのため、アンプ領域を縮小し、チップサイズの削減を実現する半導体装置が、望まれる。

【解決手段】半導体装置は、其々に対応するデータを保持する複数のメモリセル、及び、複数のメモリセルのデータを第1の電圧に基づいて其々増幅する複数のセンスアンプ、を含む第1の領域と、第1の電圧を第2の電圧に基づいて発生する第1の電源生成回路を含み、第1の領域の一辺に沿って設けられた第2の領域と、を備えている。さらに、第2の電圧は、第1の領域上を、第1の領域の一辺に平行な第1の方向に延在する第1の電源配線を経由して第1の電源生成回路に供給される。

(もっと読む)

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

半導体装置

【課題】回路規模が小さい階層型DRAMを提供すること。

【解決手段】それぞれが複数のメモリセルと、前記メモリセルに接続されたビット線と、前記ビット線をプリチャージするプリチャージ回路とを有し、行方向及び列方向にマトリクス状に配置された複数のサブアレイと、前記列方向に沿って延設され、前記サブアレイの列を選択するための列選択信号線と、前記行方向に沿って延設され、前記サブアレイの行を選択するためのメインワード線と、前記プリチャージ回路に対してプリチャージ信号を供給するプリチャージ信号線と、を備え、前記行方向または前記列方向に並べて配置された少なくとも2つの前記サブアレイが前記プリチャージ信号に応じて同一論理で制御される半導体装置。

(もっと読む)

メモリ装置のリフレッシュ方法、リフレッシュアドレス生成器及びメモリ装置

【課題】メモリ装置のリフレッシュ方法、リフレッシュアドレス生成器及びメモリ装置を提供する。

【解決手段】リフレッシュレバレッジングを利用してメモリ装置をリフレッシュするように、リフレッシュアドレスがリフレッシュ周期で生成される。リフレッシュアドレスが第2アドレスの時、第2アドレスを有する第1ストロングセルの代わりに第1アドレスを有するウィークセルに対するリフレッシュが実行される。リフレッシュアドレスが第3アドレスの時、第1ストロングセルまたは、第3アドレスを有する第2ストロングセルのうち、いずれか1つに対するリフレッシュが実行される。メモリ容量が減少するように、第1、第2及び第3アドレスうち、ただ1つに対するアドレス情報が保存される。他の実施形態において、リフレッシュレバレッジングを実行するように、リフレッシュアドレスが少なくとも1つの所定のアドレスの時、フラグによってウィークセル、第1ストロングセルまたは、第2ストロングセルのうち、いずれか1つに対するリフレッシュが実行される。

(もっと読む)

半導体装置

【課題】リフレッシュ動作時に消費電流量を低減する半導体装置を提供する。

【解決手段】ビット線(BL、/BL)と、電源線(SA電源線)を有し、電源線に供給される電圧を用いてビット線の電位を増幅させるセンスアンプ(SA)と、アクティブコマンドが入力されたことに応じて活性化した時には、アクティブコマンドに対応する電圧供給期間の最初の所定期間にオーバードライブをして電源線に第1の電圧(第1電源線LVOD_kの電圧)を供給して、所定期間後に第1の電圧よりも低い第2の電圧(第2電源線LVARY_kの電圧)を供給し、一方、リフレッシュコマンドが入力されたことに応じて活性化した時には、オーバードライブをすることなくリフレッシュコマンドに対応する電圧供給期間の最初から電源線に第2の電圧を供給する電源電圧発生回路と、を備える。

(もっと読む)

半導体記憶装置

【課題】半導体集積回路の面積を節約するために、複数の拡散層を共有化すると、それらの拡散層に接続された配線に対する寄生容量が変化する。それでも、複数の拡散層に接続された対となる配線のそれぞれにおける容量負荷のバランスが保たれる半導体レイアウトを提供する。

【解決手段】対となる配線のそれぞれが接続される拡散層を交互または互い違いに配置することで、対となる配線のそれぞれにおける容量負荷の総量のバランスを保つ。

(もっと読む)

1 - 20 / 330

[ Back to top ]