国際特許分類[G02F1/1368]の内容

物理学 (1,541,580) | 光学 (228,178) | 光の強度,色,位相,偏光または方向の制御,例.スイッチング,ゲーテイング,変調または復調のための装置または配置の媒体の光学的性質の変化により,光学的作用が変化する装置または配置;そのための技法または手順;周波数変換;非線形光学;光学的論理素子;光学的アナログ/デジタル変換器 (92,458) | 独立の光源から到達する光の強度,色,位相,偏光または方向の制御のための装置または配置,例.スィッチング,ゲーテイングまたは変調;非線形光学 (92,146) | 強度,位相,偏光または色の制御のためのもの (89,922) | 液晶に基づいたもの,例.単一の液晶表示セル (81,145) | 構造配置;液晶セルの作動;回路配置 (68,793) | 半導体の層または基板と構造上組み合された液晶セル,例.集積回路の一部を構成するセル (6,819) | アクティブマトリックスセル (6,630) | スイッチング素子が三端子の素子であるもの (6,192)

国際特許分類[G02F1/1368]に分類される特許

61 - 70 / 6,192

液晶表示装置

【課題】コストの削減を可能とするとともに表示品位の劣化を抑制することを可能とする。

【解決手段】 第1方向に沿って延出し第2方向に沿って第1ピッチで配置された第1ゲート配線及び第2ゲート配線と、第2方向に沿って延出し第1方向に沿って第1ピッチよりも大きな第2ピッチで配置された第1ソース配線及び第2ソース配線と、半導体層と、第1ゲート配線と電気的に接続されたゲート電極と、半導体層にコンタクトし第1ソース配線と電気的に接続されたソース電極と、第1ソース配線及び第2ソース配線と同一材料によって形成されたドレイン電極であって半導体層にコンタクトした第1電極部、第1電極部に繋がり第1方向に沿って延出した第2電極部、及び、第1電極部に繋がり第1方向に沿って延出した第3電極部を備えたドレイン電極と、を備えた第1基板と、第2電極部と第3電極部との間に位置し第1方向に沿って延出した主共通電極を備えた第2基板と、を備えた液晶表示装置。

(もっと読む)

保護膜溶液組成物、薄膜トランジスター表示板及び薄膜トランジスター表示板の製造方法

【課題】保護膜溶液組成物を提供すること。

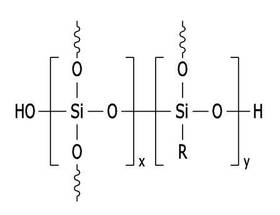

【解決手段】下記の化学式1で表わされる有機シロキサン樹脂を含む保護膜溶液組成物:

・・・化学式1

(式中、Rは1乃至25個の炭素を有する飽和炭化水素または不飽和炭化水素から選ばれた少なくとも一つの置換基であり、x、yはそれぞれ1乃至200であり、各波線は水素原子、xシロキサン単位またはyシロキサン単位との結合を示すか、あるいは、xシロキサン単位、yシロキサン単位またはこれらの組み合わせを含む他の有機シロキサン鎖のxシロキサン単位またはyシロキサン単位との結合を示す)。

(もっと読む)

積層構造、有機半導体素子、配線および表示装置、並びに有機半導体素子の製造方法

【課題】バリア性の高い保護層を有する積層構造、有機半導体素子、配線および表示装置、並びに有機半導体素子の製造方法を提供する。

【解決手段】導体または半導体を含む有機層と、絶縁材料により構成され、前記有機層を覆う保護層と、外周が前記絶縁材料と親和性を有する親和層に覆われ、前記保護層に分散された複数の粒体とを備えた積層構造。

(もっと読む)

液晶表示装置及び配向膜、並びにこれらの製造方法

【課題】液晶表示装置及び配向膜、並びにこれらの製造方法を提供する。

【解決手段】配向膜は、基板上のポリシロキサンに結合した第1プレチルト官能基、第2プレチルト官能基及び第1垂直配向性官能基を含む。環状化合物を含む前記第1垂直配向性官能基33は、前記基板191に対して実質的に垂直方向に配列する。前記第2プレチルト官能基と架橋した前記第1プレチルト官能基35aは、前記基板に対して傾くように配列する。

(もっと読む)

液晶表示装置

【課題】表示品位の劣化を抑制する液晶表示装置を提供する。

【解決手段】ゲート配線G2と、ゲート配線G2と交差するように延びたソース配線S1と、ソース配線S1と略平行に延びた主画素電極PAを備えた画素電極PEと、ゲート配線G2とソース配線S1とが交差した位置に配置されたスイッチング素子SWと、を備えた第1基板ARと、主画素電極PAを挟んだ両側で主画素電極PAと略平行に延びた共通電極CEを有する第2基板CTと、第1基板ARと第2基板CTとの間に保持された液晶分子LMを含む液晶層LQと、を備え、スイッチング素子SWは、前記画素電極と電気的に接続され前記ゲート線と重なるように配置されたドレイン配線EDを含む、液晶表示装置。

(もっと読む)

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

電気光学装置、及び電子機器

【課題】液晶装置等の電気光学装置において、保持容量を十分に確保することができ、高品質な画像を表示可能とする。

【解決手段】ゲート電極30gと電気的に接続された走査線3aと、データ線側ソースドレイン領域30sと電気的に接続されたデータ線6aと、画素電極側ソースドレイン領域30dと電気的に接続された画素電極27と、容量線3bに電気的に接続された第1容量電極16aと、第1容量電極16aと対向して設けられた第2容量電極16cと、第1容量電極16aと第2容量電極16cとに挟持された誘電体層16bと、を有する容量素子16と、を備え、層間絶縁膜11eに設けられた複数の第1コンタクトホールCNT4を介して第1容量電極16aと容量線3bとは電気的に接続される。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法及び画像表示装置

【課題】アライメント精度良く半導体層を形成し、かつ、プロセス数を増やすことなくトランジスタの素子分離を行うことのできる薄膜トランジスタ、薄膜トランジスタの製造方法及び画像表示装置を提供する。

【解決手段】薄膜トランジスタ50は、基板1と、基板1上に形成されたゲート電極2と、基板1とゲート電極2とにわたって、これらの上に形成されたゲート絶縁体層4と、ゲート絶縁体層4上に形成された半導体層5と、半導体層5上に形成された保護層6と、ゲート絶縁体層4と半導体層5と保護層6とにわたって、これらの上に形成された、ソース電極7及びドレイン電極8と、を有し、半導体層5における、ソース電極7とドレイン電極8との間のチャネル部を流れる電流の方向の一端5aは、ソース電極7の一端7aと一致し、半導体層5における他端5bは、ドレイン電極8の一端8aと一致している。

(もっと読む)

立体映像表示装置

【課題】2D映像と3D映像を選択的に実現する。

【解決手段】複数のピクセルを含み2D映像と3D映像を選択的に表示する表示パネルと、表示パネルからの光を分割するパターンドリターダを備え、ピクセルそれぞれは、第1TFTを通じデータラインに接続された第1画素電極と、上部共通ラインに接続され第1画素電極に対向する第1共通電極を含んだメイン表示部と、第2TFTを通じてデータラインに接続され放電制御TFTを通じて上部共通ラインに接続される第2画素電極と、上部共通ラインに接続され第2画素電極に対向する第2共通電極を含んだ補助表示部と、第1TFTと第2TFTに共通でスキャンパルスを印加するゲートライン、放電制御TFTに放電制御電圧を印加する放電制御ラインを含み、メイン表示部と補助表示部の間に配置された配線部を備え、上部共通ラインに共通電圧を印加する下部共通ラインはメイン表示と補助表示部の外郭部に形成される。

(もっと読む)

61 - 70 / 6,192

[ Back to top ]