国際特許分類[G06F11/10]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | エラー検出;エラー訂正;監視 (10,741) | 故障の発生への応答,例.耐故障性 (1,764) | データの表現形態に冗長性をもたせることによるエラー検出またはエラー訂正,例.チェック・コードを用いることによるもの (355) | 符号化された情報に特別のビットまたは記号を付加したもの,例.パリティチェック,9または11のキャスティングアウト (297)

国際特許分類[G06F11/10]に分類される特許

21 - 30 / 297

誤り検出訂正方法および半導体メモリ装置

【課題】効率のよい誤り検出訂正方法を提供する。

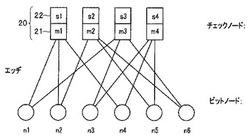

【解決手段】実施形態の誤り検出訂正方法は、低密度パリティ検査符号の検査行列のタナーグラフに対応して設定されたチェックノード20からチェックノード20に接続されている複数のビットノードに向け信頼度αを伝搬する処理と、ビットノードからビットノードに接続されている複数のチェックノード20に向け信頼度βを伝搬する処理と、を繰り返す、サムプロダクトアルゴリズムを用いた復号処理において、チェックノード20が2ビット以上のパリティを備える。

(もっと読む)

冗長化制御システム、及びその演算データの伝送方法

【課題】受信側で伝送誤り検出と、冗長系毎の演算データの誤りと故障診断とを可能とした冗長化制御システムの演算データの伝送方法を提供することを目的とする。

【解決手段】第1の演算データを生成し、返信時の誤り検出用の第1の生成アルゴリズムを使用して第1の生成データを生成するステップと、第2の演算データを生成し、誤り検出用の第2の生成アルゴリズムを使用して第2の生成データを生成するステップと、相互に第1/第2の演算データとを比較照合するステップと、一致した演算データと、第1/第2の生成データとを含む伝送データを送信するステップと、受信装置では、演算データと予め設定された第1/第2の生成アルゴリズムとから第3/第4の生成データとを生成するステップと、第1/第3の生成データとを、また、第1/第3の生成データとを比較照合して、受信した演算データの誤りを検出するステップとを備えた演算データの伝送方法。

(もっと読む)

周辺装置の設定情報のエラー検出を有するデータ処理システム

【課題】高い強固であり、且つ高い信頼性を有するデータ処理システムを提供する。

【解決手段】データ処理システムは、周辺装置用バスインタフェースと動作可能に接続された第1マスタと、周辺装置用バスインタフェースに動作可能に接続された複数の周辺装置とを含む。第1マスタは、前記周辺装置用バスインタフェースを介して複数の周辺装置の各々と通信する。該データ処理システムにおける方法は、第1マスタによって設定情報を複数の周辺装置のうちの第1周辺装置に書き込みを開始することを含む。書き込み開始に応答して、第1周辺装置に格納するために周辺装置用バスインタフェースを介して設定情報が供給される。設定情報の第1エラーシンドロームは、周辺装置用バスインタフェースによって生成される。供給された設定情報は第1周辺装置に格納され、第1エラーシンドロームは周辺装置用バスインタフェースの記憶回路に格納される。第1エラーシンドロームは、次のエラー検出中に、設定情報の完全性をチェックするように使用され得る。

(もっと読む)

車両制御システム

【課題】多数のECUがネットワークを介して協調動作を行う車両制御システムにおいて

、低コストでネットワーク内の障害ノードを正確に特定する。

【解決手段】各ノードは、ネットワーク内ノード状態判定手段,自ノードによるノード状

態判定結果送信手段および他ノードによるノード状態判定結果受信手段、および障害ノー

ド特定手段から構成され、前記ネットワーク内ノード状態判定手段による判定結果を他ノ

ードと相互に交換することにより、障害ノードを特定する。

(もっと読む)

プロセッサ

【課題】高速に符号化処理を実行可能なプロセッサを提供する。

【解決手段】プロセッサは、演算論理ユニットと、XOR回路及びAND回路を含む符号化ユニットと、第1命令のデコード結果に応じて演算論理ユニットを制御して演算処理を実行させると共に、第1命令とは別の第2命令のデコード結果に応じて符号化ユニットを制御して再帰的畳み込み符号化処理を実行させる命令デコード部と、演算論理ユニットにより実行する演算処理のオペランドを格納するとともに、符号化ユニットにより実行する符号化処理に用いるデータ及びパラメータを格納するレジスタとを含む。

(もっと読む)

データ処理回路及びデータ処理方法

【課題】データの処理時間を短縮するデータ処理回路及びデータ処理方法を提供する。

【解決手段】制御用ビットを含むデータを受信する受信回路211と、受信回路211から出力されたデータを保持する保持回路215と、受信回路211から出力されたデータのエラーを検出するエラー検出回路212と、エラー検出回路212により検出された制御用ビットのエラーである第1エラーを訂正する第1訂正回路と、エラー検出回路212で第1エラーが検出されないときは、保持回路215を経由したデータを出力し、エラー検出回路212で第1エラーが検出されたときは第1エラーが訂正されたデータを出力する出力選択回路と、を有する。

(もっと読む)

計算機の診断装置及び診断方法

【課題】 この発明は、計算機が通常動作の状態でも、エラー検出機能の検出結果からエラー検出機能を診断する、計算機の診断装置を提供する。

【解決手段】 この発明の計算機の診断装置は、診断用データを格納した診断用メモリ31と、この診断用メモリ31からCPU(中央演算処理装置)10が読み出したデータを基準データと比較し、その結果をメモリアクセスエラー情報格納部21に記憶するメモリアクセスエラー検出部20と、このメモリアクセスエラー情報格納部21を確認した後に消すメモリアクセスエラー検出部診断処理11と、を備えるものである。

(もっと読む)

情報処理装置および情報処理方法

【課題】動作に重要なプログラムが書き込まれているフラッシュROM上の物理的な記憶領域のデータが不良になっている場合にもプログラムを実行できるようにする。

【解決手段】この情報処理装置は、複数のカラムを一単位とするブロック単位にデータを記憶可能な物理的な記憶領域を有するフラッシュメモリと、プログラムデータを複数のブロックに分けて前記物理的な記憶領域に書き込み、各ブロックに付与した第1のエラー訂正符号を前記物理的な記憶領域に書き込み、前記プログラムデータに付与した第2のエラー訂正符号を前記フラッシュメモリに書き込む書き込み装置とを備える。

(もっと読む)

誤り検出訂正回路、メモリコントローラ、および半導体メモリ装置

【課題】処理効率のよい誤り検出訂正回路1を提供する

【解決手段】LDPC誤り検出訂正回路1は、サイズpの単位行列からなるブロックと複数のシフトブロックとからなる検査行列Hをもとに、受信データを、p個のグループに分割するセレクタ23と、グループをY個のサブグループに分割するセレクタ36と、確率βを算出するためのLMEM変数を第1のアドレスと関連付けて格納するビットノード記憶部26と、外部値αを算出するためのTMEM変数を第2のアドレスと関連付けて格納するチェックノード記憶部31と、チェックノード記憶部31に格納されたTMEM変数に対してシフト値にもとづくローテイト値のローテイト処理を行うローテイター35と、サブグループ単位で並列演算処理を行う(p/Y)個の演算回路からなる演算ユニット30と、全体の制御を行う制御部20と、を具備する。

(もっと読む)

ソリッド・ステート・ストレージ・デバイスのsレベル・ストレージに入力データを記録するための方法、エンコーダ装置、およびソリッド・ステート・ストレージ・デバイス

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

21 - 30 / 297

[ Back to top ]