国際特許分類[G06F11/10]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | エラー検出;エラー訂正;監視 (10,741) | 故障の発生への応答,例.耐故障性 (1,764) | データの表現形態に冗長性をもたせることによるエラー検出またはエラー訂正,例.チェック・コードを用いることによるもの (355) | 符号化された情報に特別のビットまたは記号を付加したもの,例.パリティチェック,9または11のキャスティングアウト (297)

国際特許分類[G06F11/10]に分類される特許

61 - 70 / 297

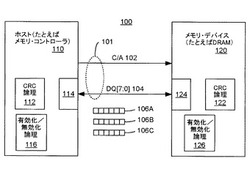

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されたエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するシステム、方法および装置を提供する。

【解決手段】メモリ・システムは、ホストとメモリ・デバイスとの間でデータを転送するためにデータ・フレームを使用する。システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

CPUポート設定方法

【課題】IDコードをより確実に切り替えるCPUポート設定方法を提供する。

【解決手段】

CPUポート設定方法は、2つのIDコードを4つのビット値の組で各々冗長に表現し、該組の各々は4つのビットで相互に値が異なり、CPU2の入力ポートの一部分をIDポート10(a、b、c、d)として割り当て、2つのIDコードのうち1つに対応するビット値の組をCPU2に読み取り可能に設定し、IDポート10を介してビット値の組を読み込み、読み込んだビット値の組が2つのIDコードのいずれのビット値の組に一致するかを判定し、一致した場合、当該IDコードを採用し、読み込まれたビット値の組が2つのIDコードのいずれかのビット値の組から1ビットで値が異なっている場合、読み込まれたビット値の組を、異なる当該IDコードのビット値の組に訂正し、該IDコードを採用する、各工程を備える。

(もっと読む)

仮想計算機システム

【課題】

PCI-Expressバスに代表される汎用のIOバスを有するサーバにおいて、32bitアドレッシングモードのI/Oアクセスを可能とするLPAR環境を提供する。

【解決手段】

(1) LPAR上のOSで発行されたIOトランザクションが32bitフォーマットであった場合で、かつ変換後の絶対アドレスが32bit空間を超えている場合に、IOトランザクションのパケットフォーマットを変換する。

(2) LPAR上のOSで発行されたIOトランザクションにECRCが付与されていた場合に、ECRCを再計算して最終受領先で正常に受信できるようにする。

(3) ECRCが既にエラーになっていた場合には、同じエラーを再現するようなECRCパターンを生成してパケットに付与する。

(4) 前記のECRC生成について、32bitと64bitのCRC演算器を搭載して同時に計算し、パケット生成時にバス上のデータ長を元に正しいCRC演算結果を選択する。

(もっと読む)

情報処理装置、該装置用のROMイメージ生成装置、および転送装置

【課題】メインプログラムをNAND型フラッシュメモリに格納する情報処理装置において、ブートストラッププログラムをNOR型フラッシュメモリに格納すると、システムのコストが高くなる。

【解決手段】電源投入後、転送装置14は、第1の記憶装置11に格納された、第1の誤り検査符号114付きのブートストラッププログラム111を検出し、誤り検出/訂正処理を施して第2の記憶装置12に転送する。転送が正常に完了した場合、CPU10は、第2の記憶装置12上のブートストラッププログラム111を実行することにより、第2の誤り検査符号115付きのメインプログラム112に誤り検出/訂正処理を施して第3の記憶装置13に転送し、第3の記憶装置13上のメインプログラム112に分岐する。これにより、NOR型フラッシュメモリを使用せずに、システムブートを行える。

(もっと読む)

データ完全性検証メカニズム

【課題】データの完全性を保守するための方法および装置が提供される。

【解決手段】ある局面の方法に従うと、物理的なチェックサム計算がデータブロック上で行なわれる(404)。物理的なチェックサム計算を行なった後、論理チェックが、データブロック内に含まれるデータ上で行なわれる(406)。データブロックが論理チェックをパスすると、データブロックは不揮発性メモリに書込まれ得る(410)。その後、データブロックが不揮発性メモリから読出されると、物理的なチェックサム検証手順がデータブロック上で行なわれて(412)、データブロック内に含まれるデータ上で論理チェックが行なわれた後にデータブロックが破損したかが判断される。

(もっと読む)

プロセッサリソースのアーキテクチャ脆弱性の検出

一実施形態では、それぞれが量子期間中のプロセッサ構造の動作に関するプロセッサメトリックに基づいてプロセッサの脆弱性計測値を検出する量子検出器を、脆弱性計測値に基づいて誤り軽減ユニットを制御するコントローラとともに提供する。他の実施形態も記載され請求されている。 (もっと読む)

誤り訂正装置、データ読み出し装置及び誤り訂正方法

【課題】消失訂正を利用した誤り訂正処理の訂正効率を向上させることのできる誤り訂正装置、データ読み出し装置及び誤り訂正方法を提供する。

【解決手段】誤り訂正回路20は、左側訂正ブロックで発生した誤りの位置を示す誤り位置情報に基づいて、右側訂正ブロックの各PI符号語が、バーストエラーが発生していると推測されるバーストエラーラインであるか否かを判定する判定回路23を備える。誤り訂正回路20は、バーストエラーラインと判定された右側訂正ブロックのPI符号語に対し、PO方向の消失訂正のための消失フラグを設定し、その設定した消失フラグを用いて右側訂正ブロックに対するPO方向の消失訂正を行う訂正回路21を備える。

(もっと読む)

マイクロプロセッサ

【課題】マイクロプログラムの読出し時にSEUを生じた場合においても対処できるマイクプロセッサを得る。

【解決手段】マイクロプログラム格納ROM1に格納されるマイクロ命令にパリティを付加する。パリティチェック回路5は、マイクロ命令レジスタ4に格納されたマイクロ命令のパリティチェックを行い、エラー検出時はパリティエラー検出信号を送出する。マイクロ命令実行部6は、パリティチェック回路5からパリティエラー検出信号が送出された場合は、例えば、マイクロプロセッサの実行を停止させる。

(もっと読む)

マイクロプロセッサおよびシグネチャ生成方法ならびに多重化システムおよび多重化実行検証方法

【課題】命令実行がプログラム順序に関係なく行われるマイクロプロセッサを用いた多重化システムにおいて、容易にシグネチャ生成できるようにする。

【解決手段】命令実行がプログラム順序に関係なく行われるマイクロプロセッサにおいて、命令が実行され、実行終了した命令の結果がプログラム順に並べ直されて命令実行が確定された、ということを示す完了命令情報を用いてシグネチャを生成する。

(もっと読む)

データ記憶プロセスにおいてデータ妥当性を確保するための装置、システム及び方法

データ記憶プロセスにおいてデータ妥当性を確保するための装置、システム及び方法が開示される。データ受信モジュール202が記憶ブロック及び既存のパリティ情報を受信する。記憶ブロック及び既存のパリティ情報を受信するのに応答して、ECC生成モジュール204が記憶ブロックのデータのための誤り訂正符号(「ECC」)チェックビットを生成する。記憶ブロックのためのECCチェックビットはブロック符号、畳み込み符号等を用いて生成される。記憶前整合性モジュール206が、記憶ブロックのデータ、既存のパリティ情報及びECCチェックビットを用いて、該記憶ブロックのデータ、該既存のパリティ情報及び該ECCチェックビットが整合しているか否かを判断する。データ記憶モジュール208が、既存のパリティ情報を格納することなく、記憶ブロックのデータ及びECCチェックビットをデータ記憶デバイス106のために格納する。  (もっと読む)

(もっと読む)

61 - 70 / 297

[ Back to top ]