国際特許分類[G06F11/10]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | エラー検出;エラー訂正;監視 (10,741) | 故障の発生への応答,例.耐故障性 (1,764) | データの表現形態に冗長性をもたせることによるエラー検出またはエラー訂正,例.チェック・コードを用いることによるもの (355) | 符号化された情報に特別のビットまたは記号を付加したもの,例.パリティチェック,9または11のキャスティングアウト (297)

国際特許分類[G06F11/10]に分類される特許

11 - 20 / 297

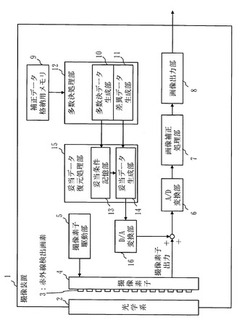

エラー訂正装置、エラー訂正方法及びエラー訂正プログラム

【課題】半導体メモリに記憶したデータにソフトエラーが発生した場合に、ソフトエラーを修正して正しいデータを得ることを目的とする。

【解決手段】補正データ格納用メモリ9には、少なくとも格納時点においては同一のデータであった補正データであって、複数のビットからなる補正データが、3つ以上の奇数個の領域に格納されている。多数決処理部12は、補正データ格納用メモリ9の各領域に格納された補正データの間で各ビットの値について多数決をとり、多数決データを生成するとともに、各領域に格納された補正データの間で値が異なるビットを示す差異データを生成する。妥当データ復元処理部15は、多数決データが妥当条件を満たす妥当データになるように、差異データが示すビットの値を変更して妥当データを生成する。

(もっと読む)

情報処理装置、情報処理システム、情報処理装置の制御方法、および、プログラム

【課題】誤動作が生じない電源電圧または周波数の正確な値を情報処理装置に設定することを容易にする。

【解決手段】第1パリティ生成部420は、演算器310により処理された処理データのエラーを検出するための第1のエラー検出符号を生成する。第2パリティ生成部は、第1のエラー検出符号から処理データのエラーを検出するための第2のエラー検出符号を生成する。第1パリティ検査部460は、保持された第1のエラー検出符号を使用して保持された処理データのエラーを第1のエラーとして検出する。第2パリティ検査部470は、保持された第2のエラー検出符号を使用して保持された処理データのエラーを第2のエラーとして検出する。制御量出力部500は、第1のエラーの発生率が第1の閾値以下であるときに、第2の閾値を第2のエラーの発生率の目標値として電源電圧または周波数を制御する制御量を出力する。

(もっと読む)

PCIバス制御システム

【課題】イニシエーターとターゲットとをPCIバスにより接続したPCIバス制御システムに関し、コマンドエラーを回避する。

【解決手段】

イニシエーター1とターゲット2−1,2−2との間をPCIバスにより接続したPCIバス制御システムであって、監視回路3と救済回路4とを設け、PCIバスによりイニシエーター1とターゲット2−1,2−2間を監視回路3と救済回路4とを介して接続すると共に、イニシエーター1と監視回路3と救済回路4との間を、コマンドCOMMとパリティPARとパリティエラーPERRとを転送するローカルバスにより接続し、監視回路3によりコマンドのパリティチェックを行って送出し、救済回路4は、PCIバスとローカルバスとを介してそれぞれ転送されたコマンドについて、正常な側を選択して、ターゲット2−1,2−2にコマンドを転送する構成を備えている。

(もっと読む)

エラー訂正回路及びエラー訂正方法

【課題】固定的に生じているエラーを含む場合は、訂正能力を超えて訂正を行う。

【解決手段】エラー訂正回路は、入力データに含まれるエラーの種別を判別する第1のエラー検出回路1と、エラー種別が1バイトエラーか、2バイトエラーである場合に、当該エラーが特定のバイトに固定的に発生している固定エラーであるか否かを判定する固定エラー検出回路2と、2バイトエラーに固定エラーが含まれる場合に、固定エラーが発生しているバイトの代わりとなる代替バイトを繰り返し発生するデータ発生回路4と、2バイトエラーに固定エラーが含まれる場合に、代替バイトで固定エラーが発生しているバイトを置き換えて、2バイトエラーが1バイトエラーとなるまで誤り検出を繰り返す第2のエラー検出回路3と、第2のエラー検出回路3で入力データが1バイトエラーとなったことを検出したら、当該入力データのエラー訂正を実行するエラー訂正回路5とを有する。

(もっと読む)

NANDフラッシュ・メモリにおける確率論的多層エラー訂正のためのシステム、方法、およびコンピュータ・プログラム

【課題】メモリからデータを検索するためのシステム、方法、およびコンピュータ・プログラムを提供する。

【解決手段】メモリからデータを検索するためのシステムを含むNANDフラッシュ・メモリにおけるエラー訂正。このシステムは、メモリと通信するデコーダを含む。デコーダは、メモリにおけるページ上に記憶されたコードワードを受信することを含む方法を実行するためのものであり、コードワードは、データおよびこのデータに応じて発生された第1の層のチェック・シンボルを含む。この方法は更に、コードワードが第1の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することを含み、これに応じて、第2の層のチェック・シンボルを受信する。第2の層のチェック・シンボルは、データの受信に応じて、更にコードワードを含むページよりも前に書き込まれたメモリにおける他のページの内容に応じて発生させる。第2の層のチェック・シンボルに応じてコードワードを訂正する。訂正したコードワードを出力する。

(もっと読む)

データ障害処理装置、及びデータ障害処理方法

【課題】繰り返しの障害発生を回避してプロセッサリリーフを実現するデータ障害処理装置、及びデータ障害処理方法を提供すること

【解決手段】データ障害処理装置は、誤り訂正機能を持つ記憶装置に格納されたデータにアクセスするプロセッサ3を備える。記憶装置は、データ供給時にデータに対して誤り訂正符号を付与する。障害識別部302は、誤り訂正符号に基づいて、前記記憶装置から供給されたデータに障害が発生しているか否かを識別する。事前評価部305は、訂正不可能障害が生じたデータが格納されたアドレスに再度アクセスする事前評価リクエストを発行する。救済可否判定部306は、前記事前評価リクエストの発行結果に応じてプロセッサリリーフが実行可能かを判定する。障害処理部307は、救済可否判定部の判定に応じて障害対応処理を行う。

(もっと読む)

車両用電装部品の制御装置およびその制御方法

【課題】内容の異なる第1のプログラムがインストールされたマイクロコンピュータに対して記憶部全体の検査を容易に行え、マイクロコンピュータの動作の信頼性を確保することができる車両用電装部品の制御装置およびその制御方法を提供する。

【解決手段】第1記憶部31には調整データ記憶領域33が設けられ、基本プログラム記憶領域32に記憶される基本プログラムのバージョンに応じた調整データが記憶される。調整データは、第1記憶部31に対する検査プログラムによる検査結果(検査値)が、基本プログラムのバージョンによらず、同値となるように調整される。よって、検査プログラムによるフラッシュメモリ30のすべての記憶領域の検査のため、基本プログラムのバージョンに応じた検査プログラムを用意する必要がない。

(もっと読む)

アドレス変換検査装置、中央処理演算装置、及びアドレス変換検査方法

【課題】メモリ管理装置に設けられたバッファに読み込まれた変換テーブルを用いて、中央処理演算装置が物理メモリへ正常にアクセスできるか否かを他のプログラムを実行したままで検査する。

【解決手段】情報処理装置10は、物理メモリのアドレスである物理アドレスと仮想メモリのアドレスである仮想アドレスとを変換するための変換テーブルに基づいて、前記仮想アドレスと前記物理アドレスとを変換するMMU20を備えている。そして、RAM14には、ページテーブルを示すページテーブル情報、及びページテーブル情報に付加され、MMU20による仮想アドレスと物理アドレスとの変換の異常の有無を検出するための異常検出情報が記憶されている。そして、CPU12は、異常検出情報に基づいて、MMU20による仮想アドレスと物理アドレスとの変換の異常の有無を検出する。

(もっと読む)

RAID装置及びガロア体の積演算処理方法

【課題】ガロア体を用いてパリテイデータを生成する際に、高速にガロア体の積演算を実行する。

【解決手段】n台のデータストレージユニット(10−1〜10−16)の内、 (n−1)/2より大きな最小の整数をsとして、i=1〜s+1番目のデータストレージユニットのデータのガロア体の元として、α^(i−1)を、i=s+2〜n番目のデータストレージユニットのデータのガロア体の元を、α^(−i+s+1)を、重み付けとして、積演算を実行する。

(もっと読む)

誤り検出訂正方法および半導体メモリ装置

【課題】効率のよい誤り検出訂正方法を提供する。

【解決手段】実施形態の誤り検出訂正方法は、低密度パリティ検査符号の検査行列のタナーグラフに対応して設定されたチェックノード20からチェックノード20に接続されている複数のビットノードに向け信頼度αを伝搬する処理と、ビットノードからビットノードに接続されている複数のチェックノード20に向け信頼度βを伝搬する処理と、を繰り返す、サムプロダクトアルゴリズムを用いた復号処理において、チェックノード20が2ビット以上のパリティを備える。

(もっと読む)

11 - 20 / 297

[ Back to top ]