国際特許分類[G06F9/455]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | プログラム制御のための装置,例.制御装置 (15,360) | プログラム記憶方式を用いるもの,すなわちプログラムを受取りそして保持するために処理装置の内部記憶装置を用いるもの (15,354) | 特別なプログラムを実行するための装置 (6,952) | エミュレーション;ソフトウェアシミュレーション (130)

国際特許分類[G06F9/455]に分類される特許

101 - 110 / 130

データ処理におけるメモリキャッシング

【課題】データ処理におけるメモリキャッシングを効率的に行うこと。

【解決手段】 データプロセッサは、主メモリと、命令キャッシュおよびデータキャッシュと、を備え、必要とされる命令を前記命令キャッシュから検索し、前記必要とされる命令が前記命令キャッシュに存在しない場合、前記データキャッシュから検索し、前記必要とされる命令がデータキャッシュに存在しない場合、前記必要とされる命令を前記主メモリから前記命令キャッシュにフェッチするように機能する命令フェッチロジックと、データ値を前記データキャッシュのデータアドレスの位置に書き込み、そして前記命令キャッシュにおいても前記アドレスが記述されている場合、そのデータ値を前記命令キャッシュに書き込むように機能するデータライトロジックと、前記データキャッシュから前記主メモリにデータを転送するように機能するキャッシュ制御ロジックと、を実行する。

(もっと読む)

複数の経路最適化を備える関数レベルジャストインタイム変換エンジン

JITバイナリトランスレータは、命令コードレベルというよりもむしろ関数レベルにおいてコードを変換する。本発明のJITバイナリトランスレータは、命令ではなく、ソースストリームからx86関数全体を取り込み、関数全体をターゲットプロセッサの同等の関数に変換し、ソースストリームに戻す前に一度にその関数全てを実行し、そうすることによって文脈切り替えを削減する。また、JITバイナリトランスレータは、ソースコード関数文脈全体を一度に参照するので、ソフトウェアエミュレータは、コード変換を最適化することができる。例えば、JITバイナリトランスレータは、x86命令のシーケンスを、効率的なPPC同等のシーケンスに変換することを決定することができる。多くのそのような最適化は、よりタイト(tighter)なエミュレートされたバイナリをもたらす。  (もっと読む)

(もっと読む)

プログラム・コード変換用の中間表現を生成するための改善されたアーキテクチャ

プログラム・コード変換に対する中間表現を生成するためのプログラム・コード変換装置および方法のための改善されたアーキテクチャ。プログラム・コード変換装置は、トランスレートされる対象コードの中間表現において、どのタイプのIRノードを生成するかを決定する。変換に関与する特定の対象および目的コンピューティング環境に依存して、プログラム・コード変換装置は、中間表現を生成する際に、ベース・ノード、複合ノード、ポリモーフィック・ノード、およびアーキテクチャ特定ノード、またはこれらの任意の組み合わせを利用する。  (もっと読む)

(もっと読む)

ファームウェアを介して仮想デバイスアクセスを提供する方法

【課題】ハードウェアサイズ、コスト及び電力消費を増大させることなく、コンピュータにおいてレガシデバイスにアクセスする方法を提供する。

【解決手段】

本発明にかかるOSにハードウェアアクセスを提供する方法は、第1のハードウェアデバイスをエミュレートする仮想化データインタフェースとして使用するため、データ処理構成のファームウェアアドレス空間の一部を割り当てること(502)と、仮想化データインタフェースをOSに提示すること(504)と、第1のハードウェアデバイスとインタフェースするOSの標準化カーネルコンポーネントを使用して、仮想化データインタフェースにアクセスすること(506)と、標準化カーネルコンポーネントを介するOSによる仮想化データインタフェースのアクセスに基づき、仮想化インタフェースと第2のハードウェアデバイスとの間でデータを交換すること(508)とを含む。

(もっと読む)

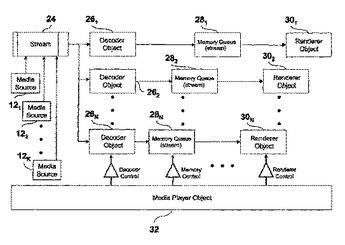

音声/映像コーデックを抽象化するためのシステム

ゲームシステムは、コーデック抽象化層(CAL)を使用して、ゲームシステムが、ゲームアプリケーションコードの変更の必要なく、新しい、かつ/または変更されたコーデックに対応できるようにする。CALは、アプリケーションプログラミングインターフェイス(API)として機能し、メディアソースとゲームアプリケーションとの間で動作する。ゲームアプリケーションは、CALと対話し、コーデックとは対話しない。コーデック間の差は、ゲームアプリケーションには気付かれない。新しいコーデックは、既存のアプリケーションコードを変更することなく、既存のアプリケーションによって導入され、使用され得る。CALは、メモリ、ファイル、httpソース、キュー、カスタムソース、外部ドライブ、ゲームメディアソース(XMediaなど)など様々なソースからのメディアを処理する。CALは、メディアのソース、受信されるメディアのタイプ(音声、画像、動画、ゲームなど)、およびメディアの圧縮に使用されるコーデックを決定する。CALは、復号されたメディアをゲームアプリケーションに提供する。  (もっと読む)

(もっと読む)

レジスタファイルとしてのオペランドスタックへの、ネイティブな命令を用いた、マイクロプロセッサのアクセス

結合されたネイティブ(RISCまたはCISC)マイクロプロセッサおよびスタック(Java(登録商標))マシン(10,11,13)は、Java(登録商標)VM命令がハードウェアで実行され得るように構築される。ほとんどのJava(登録商標)命令は直接実行され(54)、その一方でより複雑なJava(登録商標)命令、たとえばJava(登録商標)オブジェクトを操作する命令はネイティブマイクロコード(56)として実行される。ネイティブマイクロコード命令がJava(登録商標)オペランドスタックにアクセスするために、Java(登録商標)オペランドスタックポインタ(22,102)が、現在のスタックトップ(ToS)であるレジスタファイル(15,90)位置を指定する一方、状態レジスタ(101)の再マップビット(RM)は、ネイティブ命令において特定されるレジスタが、Java(登録商標)オペランドスタックポインタ最大値からJava(登録商標)オペランドスタックポインタの現在の値を引き算したものとして再マップされる(90a)ことを表わす。  (もっと読む)

(もっと読む)

マルチコアモデルシミュレータ

【課題】 高速なマルチコアモデルシミュレータを実現することを課題とする。

【解決手段】 複数のスレッド(102,103)と、前記複数のスレッドを実行する複数のコアモデル(PE0,PE1)とを有するマルチコアモデルシミュレータが提供される。複数のコアモデルは、複数のプロセッサコアモデルであり、それぞれが1つのスレッドを実行し、各スレッドの所定の実行命令数(I1)毎に相互に同期(SNC)がとられる。

(もっと読む)

異なるメモリシステム間での簡潔なマッピングを提供するためのシステム及び方法

【課題】異なるメモリシステム間での簡潔なマッピングを提供するためのメモリマッピングシステムと、それを製造及び使用するための方法である。

【解決手段】メモリマッピングシステムは、コンテンツを、一つあるいは複数の第1のメモリシステムから第2のメモリシステムに、第2のメモリシステム内でのメモリ空間の損失無しに、簡潔にマップすることができる。有利には、メモリマッピングシステムは、コンパイルの間、設計メモリシステムをエミュレーションメモリシステムにより効率的にマップするために、ハードウェアエミュレータメモリシステムに適用することができる。

(もっと読む)

プログラム・コード変換中の例外を正確に処理するための方法及び装置

対象プロセッサの正確なプログラム・カウンタ値およびレジスタ値を含む正確な対象状態に依拠する正確な例外処理。対象コード(17)は、目標プロセッサ(13)によって実行可能な目標コード(21)に変換される。生成された目標コード(17)は、障害を受けやすい対象コード命令(174)に関連する、対応する目標命令(214)を含む。さらに、対応する目標コード命令(214)の各々は回復情報(195)に関連付けられる。例外(例えば障害)が生じると、その回復情報(195)が取り出され、特に一般的なケースの目標コード(21)を生成する最適化を考慮に入れて、正確な対象状態を回復するのに当該回復情報(195)が使用される。次に、その正確な対象状態を使用して例外が正確に処理される。  (もっと読む)

(もっと読む)

インタープリタの最適化をプログラム・コード変換の間に実行する方法及び装置

トランスレータ装置に、プログラム・コード(17)の解釈機能及び変換機能の両方を実装し、対象プログラム・コード(17)は、対象プログラム・コード(17)の解釈がより大きな利点をもたらすと判断される状況においては、変換されるのではなく解釈される。トランスレータ(19)は、解釈アルゴリズムを適用して、対象プログラム・コード(17)の基本ブロックを解釈すべきか、あるいは変換すべきかについて判断する。インタープリタ機能がサポートする特定の命令サブセットをまず、対象プログラム・コード(17)の命令セット全体から選択する。基本ブロックは、1)基本ブロック内の命令の全てが、インタープリタ機能がサポートする命令サブセットに含まれると判断される場合、及び2)基本ブロックの実行回数が変換しきい値を下回る場合に解釈されることになる。これらの2つの条件のいずれかが満たされない場合、基本ブロックはトランスレータ(19)によって変換される。  (もっと読む)

(もっと読む)

101 - 110 / 130

[ Back to top ]