国際特許分類[G06T1/20]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | プロセッサアーキテクチャ;プロセッサ構成,例.パイプライン (990)

国際特許分類[G06T1/20]の下位に属する分類

ニューラルネットワーク (39)

国際特許分類[G06T1/20]に分類される特許

91 - 100 / 951

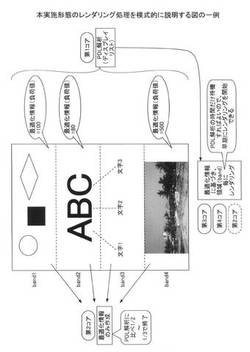

画像形成装置、画像処理方法

【課題】複数のコアを持つ画像形成装置において、描画処理部の待機時間を縮小し、複数のコアにより効率的に印刷することが可能な画像形成装置及び画像処理方法を提供すること。

【解決手段】ページの領域毎に描画処理手段16が描画処理する画像形成装置200であって、印刷データを格納する印刷データ格納手段13と、印刷データを解析し、描画対象とされるオブジェクトの描画命令をページ毎に記述した描画命令データを生成する描画命令生成手段12と、描画命令生成手段と並行して印刷データを解析し、描画処理手段16が受け持つ領域を決定するための最適化情報を作成する最適化情報作成手段14と、描画命令データと最適化情報を記憶する中間データ記憶手段15と、最適化情報に基づき受け持つ領域を決定し、領域毎に描画命令データを描画処理する描画処理手段16と、を有することを特徴とする。

(もっと読む)

演算装置および演算方法

【課題】インテグラルイメージを展開するメモリを事前に準備しておくことなく、インテグラルイメージを用いて矩形領域の積算処理を行うことができる演算装置および演算方法を提供する。

【解決手段】2次元の第1の方向および第2の方向に配列された複数の画素の値からなる画像データ群の画素の値を、第1の方向および第2の方向に順次読み出すデータ読み出し部と、基準画素の位置と第1の位置とを頂点とする矩形領域内の第1の積算値を出力する第1のデータ積算部と、基準画素の位置と第2の位置とを頂点とする矩形領域内の第2の積算値を出力する第2のデータ積算部と、第1の積算値と第2の積算値とに基づいて、第1の画素数と第2の画素数とによって表される第1の矩形データ領域の画素の値の累積値を求めるデータ累積演算部と、を備え、第1の矩形データ領域を第1の方向および第2の方向に順次移動させたときの、複数の画素の値の累積値を順次出力する。

(もっと読む)

SIMD型マイクロプロセッサ及びその処理方法

【課題】高速に階調値のヒストグラムを生成し、システム全体のスループットを向上させる。

【解決手段】プロセッサエレメントPEn(n=0,1,…,255)はそれぞれ、階調値nに対応するアドレスnを有する。マイクロカウンタ12は、カウンタレジスタ15のビット幅より小さいビット幅を有する。外部データ転送装置2から、画素データの画素値をアドレスとして含むアドレス信号が入力される毎に、当該入力されるアドレス信号に含まれるアドレスを有するプロセッサエレメントPEnのマイクロカンタ12は、カウント値C12を1だけインクリメントする。グローバルプロセッサ10は、所定のタイミングで、カウント値C12を、対応するカウンタレジスタ15に格納されたカウント値C15に累積加算するようにALU14を制御する並列加算処理を実行し、各マイクロカウンタ12に格納されたカウント値C12をリセットするように制御する。

(もっと読む)

画像処理装置、画像処理方法、プログラムおよび記録媒体

【課題】画像処理の内容に応じて、並列処理を実行するDSPの数と、入力画像データとの接続パスを決定すると共に、DSPの数に応じて画像処理の内容を削減することにより、消費電力を削減する。

【解決手段】第2の画像処理部104は、高画質処理では各色版のDSPを並列に実行させ、集約コピー処理では、C版とM版の処理を1つのDSPに実行させ、Y版とK版の処理を1つのDSPに実行させ、他のDSPの電源を落とし、消費電力を削減する。

(もっと読む)

情報処理装置、情報処理装置、プログラム

【課題】データ処理装置における内部メモリの回路規模を抑制しつつ、処理の高速化を図る。

【解決手段】 情報処理装置は、入力画像から被写体を識別するためのデータを有するパラメータを参照しながら入力画像とパラメータとの照合処理を、直列に接続された処理工程群と、処理工程群の終端の工程と分岐を介して接続された複数の処理工程群のうちのいずれか1つの処理工程群と、により多段階に行う。情報処理装置は、固定パラメータまたは可変パラメータを参照して、入力画像から被写体を識別するための照合処理を行う演算部と、演算部の演算結果により、直列に接続された処理工程群で照合処理を実行するか、または分岐を介して接続された複数の処理工程群のうちのいずれか1つの処理工程群で照合処理を実行するかを判定する判定部と、判定部の判定結果と、演算部の演算結果と、により次に演算部が参照すべき固定パラメータまたは可変パラメータを選択する選択部と、を備える。

(もっと読む)

再構成可能演算装置、データ圧縮装置及びプログラム

【課題】常に並列処理する構成と比べて回路規模を増大させずにデータを圧縮することができる再構成可能演算装置、データ圧縮装置及びプログラムを提供する。

【解決手段】再構成可能演算装置10は、複数の小回路を有し、書き込まれた回路情報に基づいて複数の小回路から選択された小回路を用いて回路を再構成可能な再構成可能回路12と、第1及び第2の圧縮回路にそれぞれ対応する第1及び第2のコンフィグデータを記憶するコンフィグデータ格納部13と、入力されるデータに応じて第1又は第2のコンフィグデータを再構成可能回路12に書き込むことにより、再構成可能回路12を第1又は第2の圧縮回路に再構成する制御部11とを備える。

(もっと読む)

画像処理装置、画像処理方法、及びスケジューリング装置

【課題】処理時間や消費電力を向上させるようにした画像処理装置、画像処理方法、及びスケジューリング装置を提供する。

【解決手段】画像データに対して画像処理を行う画像処理装置において、第1の方向と前記第1の方向に交差する第2の方向で表わされる複数の画素の画素値を用いて演算を行うマトリクス処理を含む画像処理を前記画像データに対して行う画像演算部と、前記複数の画素のサイズと、複製した画素値を用いて前記マトリクス処理を行う端処理の有無とに基づいて、前記画像データにおける第1及び第2の画像フレーム間の待ち画素数を算出するスケジューリング部と、前記第1の画像フレームの前記画像データを前記画像演算部に出力し、前記第2の画像フレームの前記画像データの出力を前記待ち画素数分遅延させた後、前記第2の画像フレームの前記画像データを前記画像演算部に出力する画像データ入力制御部とを備える。

(もっと読む)

画像処理回路及びそれを備えた画像処理装置

【課題】画像処理回路の消費電力を削減する。

【解決手段】プロセッサエレメントPEnの制御データレジスタ81は、プロセッサエレメントPEnのデータレジスタ71に格納されたデータがプロセッサエレメントPEnのデータレジスタ71の次に読み出されるプロセッサエレメントPEn+1のデータレジスタ71に格納されたデータと一致するか否かを示すプリチャージ制御データを格納する。バス制御回路44は、プロセッサエレメントPEn+1のデータレジスタ71からデータを読み出すとき、プロセッサエレメントPEnの制御データレジスタ81のプリチャージ制御データに基づいて、プロセッサエレメントPEn+1のデータレジスタ71に格納されたデータが、プロセッサエレメントPEnのデータレジスタ71に格納されたデータと一致するときは、レジスタ選択データバス501のプリチャージを抑止する。

(もっと読む)

画像処理装置、および、画像処理装置におけるメモリー制御方法

【課題】データを列単位で読み出すモジュールと行単位で読み出すモジュールを有する画像処理装置について、メモリーの設置に基づく回路規模の増大化を防ぐための技術を提供する。

【解決手段】行アクセスする第1のモジュール(行アクセス処理部107)と、列アクセスする第2のモジュール(列アクセス処理部108)と、で共用されるラインメモリー106を備える画像処理装置100における画像読み出し方法である。ラインメモリー106は、複数のバンク(1061A〜H)を有しており、第1のモジュールは、別々のバンクの同アドレス位置に格納されているデータをそれぞれ読み出し、第2のモジュールは、同一バンク内において同行に格納されている複数のデータを読み出す。

(もっと読む)

画像処理装置及びその制御方法

【課題】ダイレクトメモリアクセスを用いてメモリから画像処理モジュールへデータを転送するにおいて、メモリに要求される容量と転送帯域を小さくする。

【解決手段】

画像処理装置は、自身に設定された設定値に応じて画像データを処理する複数の画像処理部を有する。画像処理装置は、この画像処理部で処理される画像データおよび当該画像データの処理に用いる設定値を第1のアドレス空間に格納し、ダイレクトメモリアクセスにより、第1のアドレス空間から読み出した設定値および画像データのそれぞれを画像処理部に伝達するためのヘッダ情報と対応づけてコマンドとして画像処理部へ転送する。また、画像処理装置は、画像処理部から出力された処理済のコマンドからその画像処理部によって処理された画像データを抽出し、抽出した画像データをダイレクトメモリアクセスにより第2のアドレス空間へ転送する。

(もっと読む)

91 - 100 / 951

[ Back to top ]