国際特許分類[G11C11/407]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 特定の電気的または磁気的記憶素子の使用によって特徴づけられたデジタル記憶装置;そのための記憶素子 (6,432) | 電気的素子を用いるもの (5,515) | 半導体装置を用いるもの (5,114) | トランジスタを用いるもの (5,110) | リフレッシングまたは電荷再生,すなわちダイナミック・セル (3,594) | 周辺回路,例.アドレス用,デコード用,駆動用,書込み用,検出用,または同期用 (1,832) | 電界効果型のメモリ・セル用の周辺回路,例.アドレシング,復号化,駆動,書込み,検知または同期用 (1,832)

国際特許分類[G11C11/407]の下位に属する分類

初期化,増電力または減電力,メモリ消去,またはプリセット用の回路 (14)

電力供給回路または発電回路,例.バイアス電圧発生器,基板電圧発生器,バックアップ電源,電源制御回路 (170)

タイミング回路 (250)

安全または保護回路,例.不注意な,あるいは不正な読出しや書込みを防ぐためのもの;ステータス・セル;テスト・セル

アドレス回路 (57)

読出し−書込み回路 (638)

国際特許分類[G11C11/407]に分類される特許

1 - 10 / 703

半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置

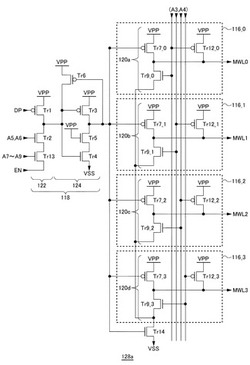

【課題】ワード線の選択回路のサイズを縮小することにより、半導体装置のサイズを縮小する。

【解決手段】メインワード線は、複数のグループに分類され、メインワードドライバはアドレス情報にしたがってメインワード線を選択する。4本のメインワード線MWL0〜MWL3から構成される1つのグループが、1つのレベルシフタ118を共有する。アドレス情報は、グループ選択のための第1アドレスとメインワード線選択のための第2アドレスを含む。メインワードドライバは、第1アドレスにしたがって、第1グループ選択回路や第2グループ選択回路128aを選択し、選択された第2グループ選択回路128aのレベルシフタ118は活性電位(ローレベル)を出力する。そして、選択された第2グループ選択回路128aに所属する複数のメインワード線MWL0〜MWL3のうちの1本が第2アドレスA3,A4により選択される。

(もっと読む)

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

メモリインターフェースおよび画像処理装置

【課題】 フレームメモリにすでに書き込まれた直前のフレームを構成する画素の画素値を示すデータの出力を開始するまでの遅延時間の短縮化が図られたメモリ制御回路、および回路規模の削減化が図られた画像処理装置を提供する。

【解決手段】 垂直同期信号VSYNCの立ち下がりエッジをSDRAMコントローラ22で検知して、初期アドレスにクリアされたアドレス信号A,読み出しを指示するコマンドCを生成してSDRAM10に供給し、SDRAM10から所定の範囲の過去データを先読みして読み出し用FIFO23に格納しておき、現在データの入力が開始された後に読み出し用FIFO23から読み出して出力する。

(もっと読む)

メモリにおけるピーク電力管理のためのメカニズム

【課題】メモリにおけるピーク消費電力管理のためのメカニズムを提供する。

【解決手段】サブ・アレイ・ブロックを含むメモリ・ストレージ・アレイにおけるピーク電力を管理するためのメカニズムが、サブ・アレイ・ブロックの各々に対するワードライン信号の起動を互い違いにすることにより、読み出し動作及び書き込み動作と関連したピーク電流を削減することができる。具体的には、1つのサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの書き込みワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、各々のサブ・アレイ・ブロックに対してワードライン信号を生成することができる。さらに、ワードライン・ユニットは、所与のサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの読み出しワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、ワードライン信号を生成することができる。

(もっと読む)

メモリ制御装置

【課題】メモリ書き込み時の消費電力を削減できるメモリ制御装置を提供する。

【解決手段】メモリ制御装置は、データバスを介してメモリ装置にデータをバースト転送するデータ出力バッファ回路390と、データのうちのメモリ装置内のメモリセルへの書き込みを禁止するデータを示すマスク信号をメモリ装置に出力するマスク信号出力バッファ回路190とを具備し、データ出力バッファ回路390は、マスク信号が書き込み禁止を示すときに出力ノードをハイインピーダンスにする。

(もっと読む)

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

メモリシステムの書き込みタイミングを較正する方法および装置

【課題】メモリの書き込み動作の実行に必要な信号のタイミングを較正する手法を提供する。

【解決手段】メモリ制御装置が、書き込み−読み出し−検証の動作を実行してデータストローブ信号とクロック信号との間のクロックサイクル関係を較正する(308)ように構成されており、クロック信号に対するデータストローブ信号の遅延をクロック周期単位で変化させることを含む。メモリチップの位相検出器は、クロック信号、マーキング信号、およびデータストローブ信号を含む複数の信号をメモリ制御装置から受信し、マーキング信号は、クロック信号の中の特定のクロックサイクルをマーキングするパルスを含み、マーキング信号を用いて、クロック信号の中の特定のクロックサイクルに窓を掛け、データストローブ信号を用いて窓掛けクロック信号を捕捉して、フィードバック信号を生成する。このフィードバック信号は、メモリ制御装置に返される。

(もっと読む)

半導体装置

【課題】パリティエラーが発生した場合に適切な処理を実行する。

【解決手段】例えば、アドレス信号ADD及びコマンド信号CMDに基づいてメモリセルアレイ11を活性化させるアクティブ制御回路230と、外部から供給される検証信号PRTYに基づいてアドレス信号ADD及びコマンド信号CMDを検証することによりパリティエラー信号PERRを生成する検証回路90と、パリティエラー信号PERRがフェイルを示した場合、活性化されているメモリセルアレイ11を所定時間経過後に非活性化させるエラー処理回路120を備える。これにより、パリティエラーが発生した場合であっても、既に発行されたコマンドを正しく実行した後にメモリセルアレイを非活性化させることができる。

(もっと読む)

半導体装置

【課題】1つのコントローラに共通接続された複数の半導体装置のモードレジスタに個々の設定値を書き込む。

【解決手段】例えば、モードレジスタ設定信号MRS1を活性化させるコマンドデコーダ82と、モードレジスタ設定信号MRS1を遅延させることによってモードレジスタ設定信号MRS2を生成するレイテンシシフタ83と、データ信号D0がローレベルである場合にはモードレジスタ設定信号MRS2に基づいてモードレジスタ設定信号MRS3を活性化させ、データ信号D0がハイレベルである場合にはモードレジスタ設定信号MRS3を非活性状態に保持する論理ゲート回路G2,G3と、モードレジスタ設定信号MRS3の活性化に応答してモード信号が設定されるモードレジスタ84を備える。これにより、1つのコントローラに共通接続された複数の半導体装置のモードレジスタに個々の設定値を書き込める。

(もっと読む)

1 - 10 / 703

[ Back to top ]