国際特許分類[G11C5/00]の内容

国際特許分類[G11C5/00]の下位に属する分類

記憶素子の配置,例.マトリックス配列におけるもの (1)

記憶素子を電気的に相互結合する機構,例.ワイヤリング (1)

記憶素子を相互結合するために用いる装置または方法,例.磁心に線を通すためのもの

電力供給装置 (4)

国際特許分類[G11C5/00]に分類される特許

51 - 60 / 102

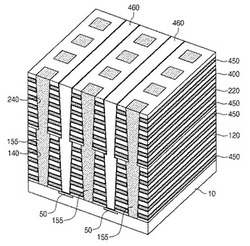

3次元半導体メモリ装置及びその製造方法

【課題】3次元半導体メモリ装置及びその製造方法を提供する。

【解決手段】本装置は、積層された導電パターン、導電パターンを貫通する活性パターン及び導電パターンと活性パターンとの間に介在される情報貯蔵膜を含む少なくとも1つのメモリ構造体を含み、活性パターンは積層された下部及び上部貫通ホールを各々満たす下部及び上部半導体パターンを含むことができる。1つのメモリ構造体を構成する情報貯蔵膜は同一の工程段階を利用して実質的に同時に形成され、1つのメモリ構造体を構成する下部及び上部貫通ホールは互いに異なる工程段階を利用して順に形成され得る。

(もっと読む)

積層型デバイス構成のための近傍界結合を使用した高速ワイヤレス直列通信リンク

【課題】バスの最大許容データ速度を負荷のせいで減少させること無く高い密度を提供する実行可能な解決策を提供する。

【解決手段】メモリモジュールは、それぞれが、空中伝播データを通信するためにループアンテナに結合されている近傍界インターフェースを有している、積層されたメモリデバイスとメモリコントローラを内蔵している。積層されたメモリデバイスとメモリコントローラとの近傍界磁界結合を作り出すために、コイルがメモリデバイス基板上に形成されているか又はプラスチックモールドに鋳込まれている。

(もっと読む)

集積回路装置及び電子機器

【課題】配線不良の発生等を低減しながらメモリーのスタックを可能にする集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置10は、集積回路装置10にスタックされるメモリー121のデータの読み出し制御、書き込み制御を行う制御部30と、メモリー121の第1〜第iのメモリーパッドPM1〜PMiに接続される第1〜第iのパッドP1〜Piと、第j〜第kのメモリーパッドPMj〜PMkに接続される第j〜第kのパッドPj〜Pkと、第iのパットPiと第jのパッドPjの間に配置される少なくとも1つのパッドPi+1〜Pj−1を含む。パッドPi+1〜Pj−1は、メモリー121のメモリーパッドには非接続であり、集積回路装置10の外部との間で信号を入力又は出力するためのパッドとなる。

(もっと読む)

半導体メモリ装置、シート状基板、筐体型半導体メモリ装置および半導体メモリ装置の製造方法

【課題】筐体型半導体メモリ装置とモジュール型半導体メモリ装置とで回路パターンや搭載される部品の共通化を図ることのできる半導体メモリ装置を提供すること。

【解決手段】本発明の半導体メモリ装置10は、回路パターン17が形成されて筐体内に収納可能とされた回路基板4と、回路基板上に搭載された不揮発性半導体メモリと、回路基板の一端部に配置されてホスト装置と接続するコネクタとを備える半導体メモリ装置であって、筐体の隅部には、筐体をホスト装置に固定するためのねじが挿入されるねじ孔が形成されており、コネクタの差込み方向に沿った回路基板の中心軸を筐体の中心軸に対してずらした配置で筐体内に回路基板が収納される場合に、回路基板をずらした方向側のねじ孔に挿入されて筐体の内側に突出するねじと干渉する回路基板の干渉部分4aを避けて回路パターンが形成され、干渉部分が切り欠かれている。

(もっと読む)

半導体装置

【課題】リペアヒューズ部から出力される貫通ラインの不良情報を複数のラッチ部に保存する半導体装置を提供する。

【解決手段】本発明の半導体装置は、積層された複数の半導体チップと、ノーマル貫通ラインとリダンダンシ貫通ラインを備え、積層された前記複数の半導体チップに信号を共通に伝達する複数の半導体チップ貫通ラインと、を備え、前記複数の半導体チップのうち少なくとも1つの半導体チップは、前記半導体チップ貫通ラインの不良情報を保存する複数のリペアヒューズ部と、前記複数の半導体チップ貫通ラインに各々割当てられ前記複数のリペアヒューズ部から出力される複数の貫通ライン不良情報信号を保存する複数のラッチ部と、を備えることを特徴とする。

(もっと読む)

メモリモジュール

【課題】高いデータ転送レートを実現可能なLoad Reduced型のメモリモジュールを提供する。

【解決手段】モジュール基板110の長辺に沿って設けられた複数のデータコネクタ120と、モジュール基板110に搭載されたメモリチップ200及びデータレジスタバッファ300と、データコネクタ120とデータレジスタバッファ300とを接続するデータ配線L0と、データレジスタバッファ300とメモリチップ200とを接続するデータ配線L1,L2とを備える。各データレジスタバッファ300と、これに対応するデータコネクタ120及びメモリチップ200は、モジュール基板110の短辺方向に並べて配置されている。本発明によれば、データ配線の配線距離が非常に短くなることから、非常に高いデータ転送レートを実現することが可能となる。

(もっと読む)

メモリモジュール

【課題】高いデータ転送レートを実現可能なLoad Reduced型のメモリモジュールを提供する。

【解決手段】モジュール基板110に搭載された複数のメモリチップ200及びそれぞれ2個以上のメモリチップが割り当てられた複数のデータレジスタバッファ300を備える。複数のデータレジスタバッファ300のそれぞれは、データ配線L0を介してデータコネクタに接続されるM個(Mは1以上の整数)の入出力端子と、データ配線L1,L2を介して対応するメモリチップ200のデータ端子に接続されるN個(Nは2M以上の整数)の入出力端子とを有しており、これにより、データ配線L1,L2の数がデータ配線L0の数のN/M倍とされている。本発明によれば、データ配線L1,L2の負荷容量が大幅に低減されることから、非常に高いデータ転送レートを実現することが可能となる。

(もっと読む)

メモリモジュール及びこれを備えるメモリシステム

【課題】高いデータ転送レートを実現可能なLoad Reduced型のメモリモジュールを提供する。

【解決手段】モジュール基板110に搭載されたメモリチップ200、データレジスタバッファ300及びコマンド/アドレスレジスタバッファ400を備える。データレジスタバッファ300は、メモリチップ200との間でデータ転送を行う。コマンド/アドレスレジスタバッファ400は、コマンド/アドレス信号をバッファリングするとともに、コントロール信号を生成する。バッファリングされたコマンド/アドレス信号は、メモリチップ200に供給され、コントロール信号はデータレジスタバッファ300に供給される。本発明によれば、データレジスタバッファ300とメモリチップ200との配線距離が短くなることから、非常に高いデータ転送レートを実現することが可能となる。

(もっと読む)

パッケージされた集積回路装置及びその動作方法とこれを有するメモリ保存装置及び電子システム

【課題】減少した信号スキューを提供するマルチチップ・パッケージされた集積回路装置及びその動作方法を提供する。

【解決手段】本発明のパッケージされた集積回路装置は、導電性パッドを上に含む基板と、基板上に複数のチップを含むチップスタックと、1次導電性ラインと、2次導電性ラインと、を備える。1次導電性ラインは、基板上の導電性パッドと、チップスタックの複数のチップのうちの一つの上に設けられた導電性パッドとを電気的に連結する。2次導電性ラインは、チップスタック内の複数のチップのうちの一つの上に設けられた導電性パッドを、その上側にある複数のチップのうちの一つ、及び下側にある複数のチップのうちの一つの上に設けられた対応する導電性パッドに電気的に連結する。

(もっと読む)

半導体装置

【課題】高温時にリフレッシュ間隔を狭めることによってDRAMをより広い温度範囲で使用する。

【解決手段】温度計測モジュールTMPは温度を検出し、検出した温度に応じた信号をリフレッシュカウンタRCとアクセスコントローラA_CONTに出力する。リフレッシュカウンタRCは、温度計測モジュールTMPの出力信号によって温度に応じたリフレッシュ間隔の変更を行い、DRAMのリフレッシュ間隔にあわせてリフレッシュを行うアドレスを生成する。アクセスコントローラA_CONTはCHIP2全体動作の制御と、DRAMへアクセスを行うためのアドレスを発生する。

(もっと読む)

51 - 60 / 102

[ Back to top ]