国際特許分類[G11C5/00]の内容

国際特許分類[G11C5/00]の下位に属する分類

記憶素子の配置,例.マトリックス配列におけるもの (1)

記憶素子を電気的に相互結合する機構,例.ワイヤリング (1)

記憶素子を相互結合するために用いる装置または方法,例.磁心に線を通すためのもの

電力供給装置 (4)

国際特許分類[G11C5/00]に分類される特許

71 - 80 / 102

データ記憶装置及び積層可能構成

第1のメモリデバイス及び第2のメモリデバイスは同一の入力/出力レイアウト配置を有する。スタックを形成するように第2のメモリデバイスは第1のメモリデバイスに固定される。接続を容易にするため、第2のメモリデバイスは、第1のメモリデバイスの出力を第2のメモリデバイスの対応する入力と位置整合させるよう、スタック内の第1のメモリデバイスに対して回転オフセットされる。第1のメモリデバイスに対する第2のメモリデバイスの回転オフセットは、第1のメモリデバイスの1つ以上の出力を、第2のメモリデバイスの1つ以上のそれぞれの入力と位置整合させる。スタック内の第1のメモリデバイスから別のメモリデバイスへの出力群と入力群との間のリンク群に基づいて、メモリデバイスのスタックは、これらのメモリデバイスを通る1つ以上の直列接続構成を担う経路群を含むことができる。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】本発明は、抵抗変化型メモリ素子をセルに用いたマルチチップパッケージにおいて、高抵抗素子を利用することにより、工程数の増加を必要とすることなく、積層された複数のメモリチップを識別できるようにする。

【解決手段】たとえば、同一パッケージ内に積層された複数のメモリチップは、それぞれ、チップアドレス識別回路150を備える。各チップは、相互に接続される第1のメモリ位置検知用パッドのテストパッドTT,TB間に、それぞれ、メモリセルと共通のプロセスにより同時に形成される可変抵抗素子CCを有する。チップアドレス識別回路150は、各チップの可変抵抗素子CCを高抵抗化することにより、チップの積層順に応じて、テストパッドTTにそれぞれ現れる電圧を、比較器154にて、メモリ位置検知回路156からの既知の比較信号と比較することで、各層のメモリチップの位置を検知する。

(もっと読む)

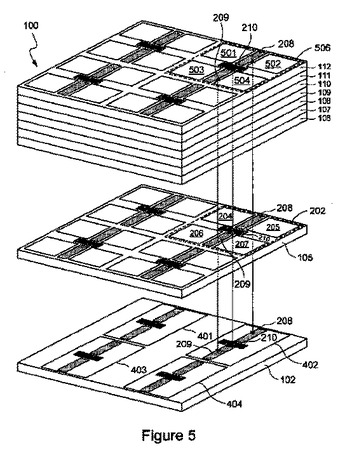

3次元メモリモジュールアーキテクチャ

本発明の様々な実施形態は、スタックされたメモリモジュールに向けられている。本発明の一実施形態において、メモリモジュール(100,600,1200,1400)は、少なくとも1つのメモリ層がスタックされた少なくとも1つのメモリコントローラ層(102,602,1204,1402)を備える。ファインピッチのスルー複数バイア(例えば、スルーシリコン複数バイア)(114,116)が、前記少なくとも1つのメモリコントローラ(401〜404)と、前記少なくとも1つのメモリ層との間の電気的な伝達を提供する前記スタックを通じて、前記少なくとも1つのメモリコントローラの表面に対してほぼ垂直に延在する。追加的には、前記メモリコントローラ層は、前記メモリモジュールに対して双方向にデータを伝達するよう構成された少なくとも1つの外部インターフェースを含む。更にまた、前記メモリモジュールには、光学層(602,1202)を含めることができる。該光学層を、前記スタック内に含めることができ、及び、該光学層は、前記少なくとも1つのメモリコントローラに対して双方向にデータを伝達するバス導波路を有する。前記外部インターフェースは、前記光学層とインターフェースする光学的な外部インターフェースとすることができる。  (もっと読む)

(もっと読む)

積み重ねられた半導体素子用の再構成可能な接続部

いくつかの実施の形態には、スタックで配置された半導体ダイと、ダイ間に通信をもたらすように構成された多数の接続部と、接続部中の欠陥を確認するとともに接続部中の欠陥を修復するように構成されたモジュールと、を含み、接続部の少なくとも一部は、ダイの少なくとも1つを通る、装置、システムおよび方法が含まれている。  (もっと読む)

(もっと読む)

積層メモリ

【課題】特定領域の動作による温度分布の偏りと、それに特性変動を効果的に削減する積層メモリを提供する。

【解決手段】外部からの活性化信号4が第1層の貫通電極1−11に入力されると、この活性化信号4は、まずマット3−1を活性化した後、バンプ2−12を経て第2層の貫通電極1−22に流れてマット3−2を活性化し、バンプ2−23を経て第3層の貫通電極1−33に流れ、マット3−3を活性化し、バンプ2−34を経て第4層の貫通電極1−44に流れマット3−4を活性化する。つまり、活性化信号4は螺旋状に層間の貫通電極を流れ、マット3−1、3−2、3−3、3−4が順次活性化される。

(もっと読む)

半導体メモリ装置、半導体メモリ装置の動作方法

【課題】各種のメモリタイプのメモリとして使用できる半導体メモリ装置の実現。

【解決手段】半導体メモリ装置としてのメモリICチップのパッケージ内に、DRAM又はSRAMとしてのメモリアレイ部が設けられていることに加え、例えばSDR、DDR、DDR2・・・DDR(n)、SRAM、DPRAM、FIFO等の各種のメモリタイプに応じた複数のインターフェースモジュールも設けられているようにする。各インターフェースモジュールは、それぞれ外部のメモリ制御回路からのアクセス要求に応じて、対応するメモリタイプに合致するタイミングでデータ書込/読出を行う。モード制御によって機能するインターフェースモジュールが動作状態とされることで、指示するモードに応じて各種のメモリタイプのメモリとして動作できるようにする。

(もっと読む)

半導体記憶装置

【課題】歩留まりを向上できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリチップ15−1〜15−8と、前記複数のメモリチップのいずれか1つが不良チップとなった場合に前記不良チップと置換される冗長用の予備チップ17と、前記複数のメモリチップおよび前記予備チップを同一のパッケージ内に封止する外囲器14とを具備する。

(もっと読む)

半導体装置及び半導体装置のテスト方法

【課題】積層パッケージの選別を容易に行う。

【解決手段】積層された2つのデバイスのうち一方のデバイスに容量ヒューズ部101から所定の信号が出力された場合、CS内部信号が、CSB入力回路103から入力される信号からDM入力回路104から入力される信号へ切り替えられ、また、他方のデバイスに容量ヒューズ部102から所定の信号が出力された場合、CS内部信号が、CSB入力回路103から入力される信号からDM入力回路104から入力される信号の極性を反転させた信号へ切り替えられ、切り替えられたCS内部信号に基づいてデバイスを測定するためのコマンド信号がコマンド回路105にて生成される。

(もっと読む)

半導体構造の製造方法

【課題】積層メモリ・ダイを利用する半導体構造とその構造を形成する方法を提供する。

【解決手段】半導体構造は、第1の半導体ダイD1と、前記第1の半導体ダイと同一の第2の半導体ダイD2を有している。第1の半導体ダイは、第1の識別回路IDと、第1の半導体ダイの表面に、第1の複数個数の入出力パッドPIO1〜PIOnを有している。第2の半導体ダイは、第2の識別回路を有しており、第1および第2の識別回路は、互に異なるプログラムを書き込まれている。第2の半導体ダイは、また、第2の半導体ダイ表面において第2の複数個数の入出力パッドを有している。第1の複数個数の入出力パッドは、各々、垂直方向に一直線上に配列されており、各第2の複数個数の入出力パッドの1個に接続されている。第2の半導体ダイは、第1の半導体ダイに対して垂直方向に一直線上に配列され、第1の半導体ダイに固着されている。

(もっと読む)

マルチダイメモリ素子

集積回路(IC)パッケージは、インタフェースダイおよび別個のストレージダイを含む。インタフェースダイは、外部メモリコントローラからメモリアクセスコマンドを受信する同期インタフェースを有するとともに、メモリアクセスコマンドに対応する行制御信号および列制御信号を出力するクロックレスメモリ制御インタフェースを有する。ストレージダイは、複数の独立アクセス可能なストレージアレイおよびクロックレスメモリ制御インタフェースから行制御信号および列制御信号を受信する、対応するアクセス制御インタフェースを有し、アクセス制御インタフェースはそれぞれ、メモリアクセスコマンドのうちの所与の1つに対応する読み取りデータを時間多重化送信で出力するデータ出力回路を含む。  (もっと読む)

(もっと読む)

71 - 80 / 102

[ Back to top ]