国際特許分類[G11C5/00]の内容

国際特許分類[G11C5/00]の下位に属する分類

記憶素子の配置,例.マトリックス配列におけるもの (1)

記憶素子を電気的に相互結合する機構,例.ワイヤリング (1)

記憶素子を相互結合するために用いる装置または方法,例.磁心に線を通すためのもの

電力供給装置 (4)

国際特許分類[G11C5/00]に分類される特許

21 - 30 / 102

半導体装置

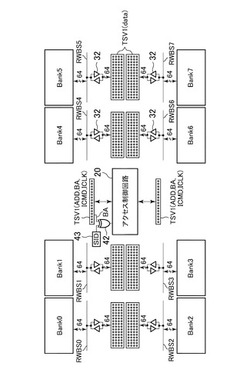

【課題】複数のメモリチップが積層された半導体装置においてリードライトバスの本数及び配線長を削減する。

【解決手段】積層された複数のメモリチップCC0〜CC7を備え、各メモリチップは複数のメモリバンクBank0〜Bank7と、各メモリバンクにそれぞれ割り当てられた複数のリードライトバスRWBS0〜RWBS7と、リードライトバスにそれぞれ割り当てられ当該メモリチップを貫通して設けられた複数の貫通電極TSV1とを備える。積層方向から見て互いに同じ位置に設けられた貫通電極TSV1はチップ間において共通接続される。メモリチップのそれぞれは、アクセスが要求されたことに応答して積層方向から見て互いに異なる位置に設けられたメモリバンクを同時に活性化し、これにより、平面位置の異なる貫通電極TSV1を介してデータの入出力を同時に行う。

(もっと読む)

半導体装置及びその温度制御方法

【課題】パッケージ基板の上に実装された半導体パッケージが提供される。

【解決手段】本発明の一実施形態による半導体パッケージは、温度測定装置と、温度制御回路とを具備している。前記温度測定装置は、前記半導体パッケージの温度を測定する機能を有する。前記温度制御回路は、前記温度測定装置で測定された前記半導体パッケージの温度を基準にして、前記半導体パッケージの動作速度を変化させる機能を有する。

(もっと読む)

半導体装置

【課題】リードデータの衝突を回避すること。

【解決手段】本発明の半導体装置は、複数のメモリチップと、前記複数のメモリチップから内部データバスに出力されたリードデータを入力し、入力されたリードデータを外部データバスに出力するI/Fチップと、を有する。また、前記内部データバスは、前記複数のメモリチップごとに設けられている。また、前記I/Fチップは、前記複数のメモリチップから前記内部データバスを介して入力されたリードデータをバッファリングするFIFO回路と、前記FIFO回路にバッファリングされたリードデータの前記外部データバスへの出力タイミングを調整するFIFOコントローラと、を有する。

(もっと読む)

メモリデバイスおよび積層半導体基板並びにこれらの製造方法

【課題】多様な種類のメモリデバイスを単位時間あたりにより多く製造できるような汎用性の高い構造を備えたメモリデバイス、積層半導体基板、これらの製造方法を提供する。

【解決手段】メモリデバイス100は、積層チップパッケージ90と、コントローラチップ95とを有している。積層チップパッケージ90は、複数のメモリチップ50が積層されている。積層チップパッケージ90とコントローラチップ95との間に介挿チップ51が積層されている。メモリチップ50は複数の配線電極50を有している。介挿チップ51は複数の配線電極35を有している。配線電極35は、コントローラチップ95に形成されている複数の配線電極97の配置パターンと共通する共通配置パターンで形成されている。介挿チップ51の上にコントローラチップ95が載置されている。

(もっと読む)

半導体装置

【課題】複数のランクに分類された積層型の半導体装置において、異なるランクに対して連続アクセスされた場合のデータの衝突を防止する。

【解決手段】ライトデータを伝送する貫通電極TSVWとリードデータを伝送する貫通電極TSVRとをそれぞれ有する互いに積層された複数のコアチップCC0〜CC7と、これらコアチップCC0〜CC7に共通接続されたインターフェースチップIFとを備える。インターフェースチップIFは、データ入出力端子16と、データ入出力端子と貫通電極TSVWとの間に設けられた52入力バッファと、データ入出力端子16と貫通電極TSVRの間に設けられた出力バッファ51とを有する。本発明によれば、ライトデータとリードデータを互いに異なる貫通電極を介して伝送していることから、異なるランクに対して連続アクセスされた場合であってもデータの衝突が生じない。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてインターフェースチップからコアチップへのクロック信号の供給を不要とする。

【解決手段】外部から供給されるコマンド信号CMD及びクロック信号CKを受けて、各々がクロック信号CKに同期し、且つ、互いにタイミングが異なる複数のリード制御信号R1,R2を出力するリードタイミング制御回路100を有するインターフェースチップIFと、インターフェースチップIFに積層され、コマンド信号CMDが示す動作をリード制御信号R1,R2に同期してそれぞれ実行する複数の内部回路を有するコアチップCC0〜CC7とを備える。本発明によれば、コアチップに内でのレイテンシ制御が不要となることから、コアチップにクロック信号を供給する必要がなくなる。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリ装置を提供する。

【解決手段】少なくともターミナルの第1対を含むパッケージインターフェースと、半導体チップのスタックと、それぞれ半導体メモリチップに備えられ、すぐに隣接した半導体チップの貫通電極と電気的に連結される貫通電極の複数のスタックと、第1情報を提供するディファレンシャル信号を受信するターミナルの第1対と連結される入力、及び貫通電極の複数のスタックのうち少なくとも一つに、第1情報を含む出力信号をシングルエンド信号のフォーマットで提供する出力を含むインターフェース回路と、を備える半導体パッケージである。

(もっと読む)

メモリ装置

【課題】異なる種類のメモリを積層させたメモリ装置を提供する。

【解決手段】メモリ装置100は、互いに異なる種類の2つのメモリセルアレイを積層して構成されたメモリセルアレイ10を備える。互いに異なる種類の2つのメモリセルアレイそれぞれには、それぞれに対応するワード線が上記マトリクスの行方向に延設されている。また、互いに異なる種類の2つのメモリセルアレイにおける上記マトリックスの列方向に延設されたデータ転送線は、互いに異なる種類の2つのメモリセルアレイにおいて共用されている。メモリ層選択部26は、互いに異なる種類の2つのメモリセルアレイのいずれか一方を選択する。Xデコーダ25は、メモリ層選択部26の選択にしたがって、それぞれに対応するワード線を通じて互いに異なる種類の2つのメモリセルアレイに各処理に応じた電圧を供給する。

(もっと読む)

半導体装置

【課題】スタブ配線の形成による信号波形の劣化を改善可能な半導体装置を提供する。

【解決手段】第1の信号経路Fが第1の入力端Faに対応して分岐を有さない1本の経路として形成され、複数の第1の入力端Faとこれに対応する複数の半導体パッケージD1の複数の第1の端子T1とが各々複数の第1の信号経路Fのうちの対応する1つによってフライバイ形式にて接続される。半導体パッケージパターン等の構成に限定されるものではなく、分岐を有さない1本の経路としてフライバイトポロジ(Fly−by Topology)が実現可能なものであれば、他の構成とすることも可能である。

(もっと読む)

半導体装置および集積型半導体装置

【課題】積層型半導体装置における全ての半導体チップのテストを行うにあたり、テスト装置側でチップ選択端子に対して割り当てるべき端子数を削減する。

【解決手段】集積型半導体装置100のチップ200において、制御信号出力部210は、制御信号入力端子302Aからの外部制御信号TRGIの入力に応じて、チップ識別子保持部250に対してチップ識別子の保持を指示する。チップ識別子保持部250は指示に応じて、アドレス入力端子303Aから入力されるチップ識別子の値を保持する。また、チップ識別子の保持タイミングを指示した後の所定タイミングで次段チップ制御信号TRGOを出力する。次段チップ制御信号TRGOは、次段のチップ200が制御信号入力端子302Aから外部制御信号TRGIとして入力する。

(もっと読む)

21 - 30 / 102

[ Back to top ]