国際特許分類[G11C5/00]の内容

国際特許分類[G11C5/00]の下位に属する分類

記憶素子の配置,例.マトリックス配列におけるもの (1)

記憶素子を電気的に相互結合する機構,例.ワイヤリング (1)

記憶素子を相互結合するために用いる装置または方法,例.磁心に線を通すためのもの

電力供給装置 (4)

国際特許分類[G11C5/00]に分類される特許

61 - 70 / 102

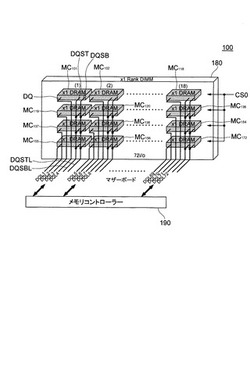

メモリモジュール

【課題】メモリバッファを用いることなく、各チャネルにかかる負荷が低減されたメモリモジュールを提供する。

【解決手段】モジュール基板180と、モジュール基板180に搭載されたメモリチップMC101〜MC172と、メモリチップMC101〜MC172にそれぞれ個別に接続され、リードデータ又はライトデータが伝送されるデータ入出力配線DQL1〜DQL72とを備える。メモリチップMC101〜MC172の数は、データ入出力配線DQL1〜DQL72を介して同時に伝送されるリードデータ又はライトデータのビット数と等しい。このように、複数のデータ入出力配線がそれぞれ個別のメモリチップに接続されていることから、メモリバッファを用いることなく、各チャネルにかかる負荷を低減することが可能となる。

(もっと読む)

マスタデバイスを含む積み重ね半導体デバイス

本発明は、スタックを備えるシステムを開示する。このスタックは、第1の不揮発性メモリチップと、少なくともいくつかの非コア回路が欠如している第2の不揮発性メモリチップと、第1の不揮発性メモリチップと第2の不揮発性メモリチップの間に延びる複数の電気経路とを含み、これらの電気経路により、第1の不揮発性メモリチップが第2の不揮発性メモリチップに、デバイス動作のために必要な信号および電圧を供給することが容易になる。  (もっと読む)

(もっと読む)

半導体装置

【課題】複数のチップダイを積層して構成される半導体装置では、システムのデータ転送速度が高速化すると、各チップダイにおけるデータ転送速度を高速化しなければならず、この結果、消費電力の増加、歩留まりの低下等の問題が生じていた。

【解決手段】単一のチップダイにおいて入出力される信号数に対応した数のビアだけでなく、積層されるべきチップダイにおいて入出力される信号数にも対応した数のビアと、前記各ビアに対する入出力を制御するスイッチを、各チップダイに備えた半導体装置が得られる。各スイッチの導通、非導通をROMによって制御することにより、積層される複数のチップダイからの信号を並列に出力することができ、各チップダイにおけるデータ転送速度をシステムの転送速度に合わせて高速化する必要がなくなる。

(もっと読む)

誤り領域を管理するためのメモリ装置及び方法

積層メモリダイ及びロジックダイを含むメモリ装置及び方法が記載される。記載される方法及び装置は、積層メモリダイを再分配し、メモリマップ内に新たな区画を格納することを提供する方法及び装置を含む。選択された構成に再分配することにより、メモリ装置の残りに影響を与えることなく、メモリの部分を利用から除外することができる。追加の装置、システム、及び方法が開示される。 (もっと読む)

超高帯域メモリのダイスタック

【課題】 3次元ダイスタックを用いて形成されたメモリを提供する。

【解決手段】 システムは、中央処理装置(CPU)、CPUと連絡し、複数の垂直に積層された集積回路チップと複数の入力/出力(I/O)ポートを含み、各I/Oポートは、基板貫通ビアによって複数のチップの少なくとも1つに接続されるメモリデバイス、及び

CPUと前記メモリデバイスと連絡し、メモリデバイスにデータを伝送、またはメモリデバイスから伝送するのを管理するように構成するダイレクトメモリアクセス(DMA)コントローラを含むシステム。

(もっと読む)

積層メモリ素子

【課題】積層メモリ素子を提供する。

【解決手段】メモリセルアレイをそれぞれ備えるとともに、複数のメモリ層のうち、少なくとも1層が複数のメモリ層のうち、他の1層の上に積層される複数のメモリ層と、メモリセルのうち、少なくとも1つのメモリセルについてのアドレス情報を、垂直アドレス情報及び水平アドレス情報に分類して処理するための第1能動回路部と、第1能動回路部によって処理された信号に基づいて、メモリセルのうち、少なくとも一つに対してメモリ選択信号を生成するための少なくとも1つの第2能動回路部とを具備する積層メモリ素子である。

(もっと読む)

半導体装置、半導体システム

【課題】動作速度が従来よりも高速な半導体装置を提供する。

【解決手段】各々に同じ信号が入力される第1電極パッド21及び第2電極パッド22と、第1電極パッド21及び第2電極パッド22の両方から信号が入力されるメモリ回路23と、を備える半導体装置である。メモリ回路23は、第1電極パッド21から入力される信号と、第2電極パッド22から入力される信号と、のいずれか早く入力される信号により動作する。

(もっと読む)

メモリモジュール及びその使用方法、並びにメモリシステム

【課題】データ入出力パッド13の終端抵抗と終端抵抗のオンオフを制御する信号を入力するための終端抵抗制御パッド14とを備えた同期式メモリチップを多ランク搭載した多ランクメモリモジュールにおいて、メモリモジュールに設けた終端抵抗制御(ODT)端子の数より、ランクの数のほうが大きい場合においても、内蔵終端抵抗を用いて、高速動作を可能にする。

【解決手段】モジュール基板8上のデータバス19とデータ入出力パッド13との配線の長さが長いメモリチップ12の終端抵抗制御パッド14を、終端抵抗制御配線18、21に接続し、ODT端子から終端抵抗のオンオフを制御し、モジュール基板上のデータバス19とデータ入出力パッド13との配線の長さが短いメモリチップ11の終端抵抗制御パッドについて終端抵抗をオンさせるように固定電位20に接続する。

(もっと読む)

メモリコネクタおよび画像形成装置

【課題】メモリに記憶されたデータの漏洩を確実に防止しうるメモリコネクタを提供する。

【解決手段】このメモリコネクタは、記憶デバイスを備えた基板の複数の端子が挿抜される複数の併設された接触子を有するメモリコネクタにおいて、前記メモリコネクタに、差し込まれた状態の前記基板の抜去操作時に前記端子と接触して、前記記憶デバイスの電源端子とグランド端子間を導電接続するショート部材を設けている。また、前記ショート部材は、前記複数の接触子の上方に配設され、前記基板の抜去操作時に前記複数の端子と接触し、少なくとも前記記憶デバイスの電源端子とグランド端子間を導電接続する導電部材であるとしてもよい。

(もっと読む)

情報処理装置および半導体記憶装置

【課題】マルチコア構成のシステムLSIの処理性能を高める。

【解決手段】1チップ内に複数のCPUコアを有するシステムLSIまたはマイクロプロセッサと、それに積層されたDRAMにより情報処理装置を構成する。システムLSIチップ内部はチップ多分割I/O分散アーキテクチャをとる。システムLSI内に独立動作可能な複数のCPUコアを有し、それぞれのCPUコアに3Dインターフェース回路を設け、独立にデータ送受信を行うことを可能とする。DRAMチップ内部もチップ多分割I/O分散アーキテクチャをとる。DRAMを独立動作可能な複数のDRAMコアに分割し、それぞれのDRAMコアに3Dインターフェース回路を設け、独立にデータ送受信を行うことを可能とする。

(もっと読む)

61 - 70 / 102

[ Back to top ]