国際特許分類[H01L21/768]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 装置内の別個の構成部品間に電流を流すため使用する相互接続を適用するもの (5,422)

国際特許分類[H01L21/768]に分類される特許

161 - 170 / 5,422

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

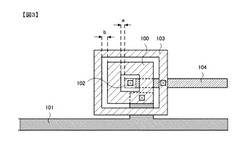

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

半導体装置およびその製造方法

【課題】 実施形態は、層間配線抵抗が低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、基板と、前記基板上に第1の触媒金属膜と、前記第1の触媒金属膜上にグラフェンと、前記グラフェン上に層間絶縁膜と、前記層間絶縁膜を貫通するコンタクトホールと、前記コンタクトホール底部に前記グラフェンと電気的に導通する導電膜と、導電膜上に水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した第2の触媒金属膜と、前記第2の触媒金属膜上にカーボンナノチューブとを備えることを特徴とする。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置及びその製造方法

【課題】 エレクトロマイグレーション耐性及び信頼性に優れた半導体装置及びその製造方法を提供する。

【解決手段】 基板上に絶縁膜を形成する工程と、前記絶縁膜をエッチングして配線溝を形成する工程と、前記配線溝内に銅膜を形成し、銅配線を形成する工程と、前記銅配線及び前記絶縁膜の表面を平坦化する工程と、平坦化された前記銅配線及び絶縁膜上に金属膜を形成する工程と、酸素を含んだ雰囲気中で加熱を行うことにより前記銅配線上の前記金属膜と前記銅配線とを選択的に反応させて合金膜を形成するとともに前記絶縁膜上の前記金属膜を酸化して絶縁性の膜に変化させる工程と、前記合金膜及び前記絶縁性の膜上にブロック膜を形成する工程とを備えた半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】バリア層(バリアメタル)13を覆うようにライナー層14が形成されている。ライナー層14は、Ni(ニッケル)から構成される。ライナー層14は、このライナー層14の内側に形成されるCu(銅)からなる導電体15に対する濡れ性を高め、かつ、溝部12の内側の平滑性を高める。

(もっと読む)

半導体装置

【課題】配線間の影響を抑制することができる多層配線を有する半導体装置を実現する。

【解決手段】本発明の実施形態における半導体装置は、下層の配線層に第1の方向に沿って形成された信号配線11と、下層の配線層と絶縁膜を介して配置される上層の配線層に第1の方向と交差する第2の方向に沿って形成された基準電位配線13と、 上層の配線層に基準電位配線13に沿って近接して形成されたシールド線14a、14bと、を有し、信号配線11と基準電位配線13の交差部15cにおいて基準電位配線13とシールド線14a、14bとの距離が他の部分に比べてより狭くなっていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体装置の製造方法

【課題】煩雑な工程を経ることなく、マイクロスリットの発生による断線が生じ難い、銅配線を含む半導体装置の製造方法を提供すること。

【解決手段】基板上の凹部を有する層間絶縁膜上にバリア膜を介して凹部を埋めるように銅膜を形成した構造体を準備する工程と、構造体の銅膜をバリア膜との界面まで化学機械研磨により除去し、凹部内にCu配線を形成する工程と、Cu配線をエッチングしてその表面を層間絶縁膜表面よりも後退させる工程と、バリア膜を化学機械研磨により除去する工程とを有し、Cu配線の表面を層間絶縁膜表面よりも後退させる際に、構造体を真空状態の有機化合物雰囲気に配置し、構造体の銅配線表面を含む面に酸素ガスクラスターイオンビームを照射し、その中の酸素ガスクラスターイオンにより、銅配線の表面の銅を酸化させて酸化銅とするとともに、酸化銅と有機化合物を反応させて銅配線を異方的にエッチングする。

(もっと読む)

半導体チップ、これを含む半導体パッケージ、及びその製造方法

【課題】信頼性を向上させることができる高集積化された半導体チップ及びこれを含む半導体パッケージが提供される。

【解決手段】本発明にしたがう半導体チップは、基板と、前記基板を貫通している貫通ビアと、前記貫通ビアと前記基板との間に介在されたウェッティング膜と、前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む。本発明の実施形態による半導体チップは突出された貫通ビアをウェッティング膜が覆っているので、導電パッドを追加に形成する必要がない。したがって、半導体チップの厚さを減らすことができ、構造が単純化されて半導体装置の高集積化により有利である。また、工程を単純化することができるので、生産収率を増大させ得る。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

161 - 170 / 5,422

[ Back to top ]