国際特許分類[H01L21/8232]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660)

国際特許分類[H01L21/8232]の下位に属する分類

MIS技術 (17,448)

国際特許分類[H01L21/8232]に分類される特許

81 - 90 / 212

化合物半導体素子及びその製造方法

【課題】高速動作が可能でかつ、ESD耐性の高い化合物半導体素子及びその製造方法を提供すること。

【解決手段】本発明に係る化合物半導体素子は、電界効果トランジスタ又はヘテロ接合バイポーラトランジスタからなるトランジスタ部と、トランジスタ部と並列に接続されたESD保護部114と、を備え、ESD保護部114は、第1導電型の不純物を含有する第1及び第2の半導体層109、113と、第1及び第2の半導体層109、113の間に形成され、第1及び第2の半導体層109、113の禁制帯幅よりも禁制帯幅が広く、かつ、不純物濃度が1×1017cm−3以下である第3の半導体層111と、を備えるものである。

(もっと読む)

増幅素子

【課題】ECMのインピーダンス変換および増幅に、J−FETを入力としバイポーラトランジスタを出力とする増幅素子に、バックゲート構造のJ−FETを用いると、バックゲート−半導体基板間の容量が、増幅素子の入出力間の寄生容量(ミラー容量)となり、増幅素子の入力ロスが増大する問題に対し有効な半導体装置を提供する。

【解決手段】接地されたp型半導体基板11にp型半導体層12を積層し、p型半導体層12にn型チャネル領域22を有するJ−FETと、n型コレクタ領域33bを有するバイポーラトランジスタを設けた増幅素子とする。これにより、増幅素子の入出力間の寄生容量が発生しなくなるため、ミラー容量による入力ロスの増大を防止できる。また、J−FETのチャネル領域は、エミツタ拡散31と同時に形成できるため、IDSSSや、ピンチオフ電圧が安定し、増幅素子としての消費電流のばらつきが低減し、生産性が向上する。

(もっと読む)

モノリシック垂直集積複合III−V族及びIV族半導体デバイス

【課題】3ー5族半導体デバイスを4族半導体デバイスと一緒に、単一のダイの上にモノリシック集積することができる半導体装置を提供する。

【解決手段】第1、第2の表面を有する両面仕上げ処理された半導体基板と、前記第1の表面上に形成され、一つの4族半導体デバイスを含む4族半導体層と、前記第2の表面上に形成され且つ前記少なくとも一つの4族半導体デバイスに電気的に結合された3−5族半導体デバイスを含む3−5族半導体本体130とを備える。さらに電気的結合のための基板ビア112及び/又はウェハ貫通ビア114を備える。4族半導体層はエピタキシャルシリコン層とすることができ、エピタキシャル層上に形成されたTFET及びショットキーダイオード(FETKY)とすることができる。また、3−5族半導体デバイスは高電子移動度トランジスタ(HEMT)170とすることができる。

(もっと読む)

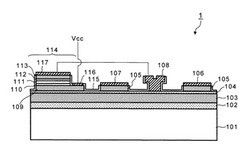

半導体装置

【課題】歪特性の改善が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、第1のFET103および第2のFET113のそれぞれに対応して設けられた基板電位制御用半導体層902および903と、半導体基板内に設けられ、基板電位制御用半導体層902および903のそれぞれを電気的に分離する素子間分離領域901と、基板電位制御用半導体層902および903のそれぞれに対応して設けられた第1の基板電位制御用電極108および第2の基板電位制御用電極118と、第1の基板電位制御用電極108および第2の基板電位制御用電極118のそれぞれに対応して設けられ、対応する基板電位制御用電極に高電圧又は低電圧を印加する複数の第1の基板電位制御信号源109および第2の基板電位制御信号源119とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

トランジスタ素子用エピタキシャルウェハの製造方法

【課題】HEMT用エピタキシャル層の移動度を低下させることのない、電気特性の良いトランジスタ素子用エピタキシャルウェハを製造することができるトランジスタ素子用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に高電子移動度トランジスタ用エピタキシャル層3を形成し、高電子移動度トランジスタ用エピタキシャル層3上に、ヘテロバイポーラトランジスタ用エピタキシャル層4を形成するトランジスタ素子用エピタキシャルウェハ1の製造方法において、高電子移動度トランジスタ用エピタキシャル層3を、成長温度600℃以上750℃以下、V/III比10以上150以下で成長させ、ヘテロバイポーラトランジスタ用エピタキシャル層4を、高電子移動度トランジスタ用エピタキシャル層3の成長温度よりも低温で成長させる方法である。

(もっと読む)

エンハンスメントモード型およびデプレションモード型のワイドバンドギャップ半導体JFETのためのゲートドライバ

接合形電界効果トランジスタ(JFET)を駆動するための、DC接続2段ゲートドライバが提供される。JFETは、SiC JFETのようなワイドバンドギャップ接合形電界効果トランジスタ(JFET)であり得る。ドライバは、第1ターンオン回路、第2ターンオン回路及びプルダウン回路を含む。ドライバは、入力パルス幅変調(PWM)制御信号を受け入れて、JFETのゲートを駆動させるための出力ドライバ信号を発生させるように配置される。 (もっと読む)

半導体装置

【課題】携帯電話用コンデンサマイクロフォンなどにおいて、J−FETのソース−ドレイン間にRFフィルタを接続する回路が採用される場合に、個別のRFフィルタとJ−FETを基板に実装すると、組立工程での歩留まりの低下が問題となる。また小型化の要求にも対応できない問題があった。

【解決手段】1つのn型半導体基板に、J−FETとRFフィルタを集積化する。半導体基板をバックドレインとし、n型半導体基板表面に設けたp型不純物領域内にJ−FETを形成する。バックドレインは表面のJ−FETのドレイン領域と接続する。J−FETのゲート領域はJ−FETのチャネル領域と、p型不純物領域に設けられる。ドレイン領域の一部はJ−FETのチャネル領域からn型半導体基板まで延在し、n型半導体基板には、p型不純物領域を設けてJ−FETのソース−ドレイン間にRF−フィルタを構成する。

(もっと読む)

ワイドバンドギャップ半導体パワーJFETのための高温ゲートドライバ及びそれを含む集積回路

高い周囲温度環境において作動することが可能なワイドバンドギャップ(例えば、>2eV)半導体接合形電界効果トランジスタ(JFET)のためのゲートドライバについて記載される。ワイドバンドギャップ(WBG)半導体デバイスは、炭化ケイ素(SiC)及び窒化ガリウム(GaN)を含む。ドライバは、入力、出力、第1供給電圧を受け取るための第1基準線、第2供給電圧を受け取るための第2基準線、グランド端子、6つの接合形電界効果トランジスタ(JFET)を有する非反転ゲートドライバであり得、第1JFETおよび第2JFETは、第1反転バッファを形成し、第3JFETおよび第4JFETは、第2反転バッファを形成し、及び第5JFET及び第6JFETは、高温パワーSiC JFETを駆動させるために使用され得るトーテムポールを形成する。反転ゲートドライバも記載される。 (もっと読む)

半導体素子

【課題】 従来のダイオードでは、微小な電圧領域では、十分な検波特性が得られない。

【解決手段】 電子及び正孔が、ダイレクトトンネル現象により透過可能な厚さの空乏層を挟んでp型半導体層及びn型半導体層が相互に接合されている。n型半導体層とp型半導体層との間に、両者のエネルギバンドがフラットになるフラットバンド電圧を印加した状態で、n型半導体層の禁制帯とp型半導体層の禁制帯とが部分的に重なる。電圧無印加時の平衡状態で、空乏層に連続するエネルギバンドの曲がり部よりも空乏層から離れた領域において、p型半導体層の価電子帯上端の電子のエネルギレベルが、n型半導体層の伝導帯下端の電子のエネルギレベルと同等か、またはそれよりも高い。

(もっと読む)

81 - 90 / 212

[ Back to top ]