国際特許分類[H01L21/8232]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660)

国際特許分類[H01L21/8232]の下位に属する分類

MIS技術 (17,448)

国際特許分類[H01L21/8232]に分類される特許

51 - 60 / 212

窒化物系半導体素子及びその製造方法

【課題】窒化物系半導体素子及びその製造方法を提供する。

【解決手段】ダイオード構造物を有するベース基板110と、該ベース基板110上に配置されるエピタキシャル成長膜120と、該エピタキシャル成長膜120上に配置される電極部140とを含み、該ダイオード構造物は、第1タイプの半導体層112と、該第1タイプの半導体層の中央に介在する第2タイプの半導体層114とを含む。

(もっと読む)

疑似ダイオードを有するIII族窒化物スイッチングデバイス

【課題】ダイオード機能を有するGaN−HEMTのようなIII族窒化物トランジスタを提供する。

【解決手段】GaNスイッチングデバイスは、低しきい値のGaNトランジスタ346の両端間に結合された高しきい値のGaNトランジスタ340を有しており、この低しきい値のGaNトランジスタ346が逆方向モードで並列ダイオードとして機能するようになっている。高しきい値のGaNトランジスタ340は、順方向モードの際にGaNスイッチングデバイスに対し雑音排除性を提供するように構成されている。互いに著しく異なるしきい値を有するようにする。その結果、従来のシリコンFETにおける固有のボディダイオードの機能及びモノリシック構造を維持したまま、III族窒化物スイッチングデバイスの優れたスイッチング特性を利用することができるようになる。

(もっと読む)

接合型電界効果トランジスタ、その製造方法及びアナログ回路

【課題】外部ノイズの影響を低減できるJFETを提供する。

【解決手段】本発明に係るJFET50は、p型半導体基板1と、p型半導体基板1の表面に形成されているn型チャネル領域3と、n型チャネル領域3内に形成されており、n型チャネル領域3よりも不純物濃度の高いn型埋め込み領域4と、n型チャネル領域3の表面に形成されているp型ゲート領域6と、n型チャネル領域3の表面に、p型ゲート領域6を挟むように形成されているn型ドレイン/ソース領域7及びn型ドレイン/ソース領域8とを備え、n型埋め込み領域4は、n型ドレイン/ソース領域7及びn型ドレイン/ソース領域8の一方の下方に形成されており、他方の下方に形成されていない。

(もっと読む)

半導体装置

【課題】本発明は、面積利用効率を向上しつつ、トランジスタTの特性を維持し、更に整流素子Dの低順方向電圧化を図ることができる半導体装置を提供する。

【解決手段】半導体装置1は整流素子DとトランジスタTとを備える。整流素子Dは、電流経路43と、その一端に配設され整流作用を持つ第1の主電極11と、その他端に配設された第2の主電極12と、その第1の主電極11と第2の主電極12との間に配設され、第1の主電極11に比べて順方向電圧が大きい第1の補助電極15とを有する。トランジスタTは、電流経路43と、その一端において電流経路43と交差する方向に配設された第3の主電極13と、第3の主電極13を取り囲んで配設された制御電極14と、第2の主電極12とを有する。

(もっと読む)

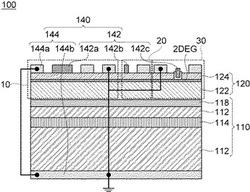

半導体装置

【課題】破壊耐量が高い、2DEGを用いた半導体装置を提供する。

【解決手段】ソース・ドレイン間の耐圧よりも耐圧が低いSBDダイオード18のカソード電極がドレイン電極16に接続され、アノード電極がポリシリコンダイオード20を介してゲート電極14に接続されている。これにより、L負荷耐量試験回路によるL負荷耐量試験において、ゲート信号がターンオフされると、ドレイン電圧が印加され、SBDダイオード18にアバランシェ電流が流れ始め、電圧降下が発生し、ゲート電圧Vgが印加される。ゲートに閾値電圧Vthよりやや高い電圧(ゲートがオンする程度の電圧)が印加されると、ソース・ドレイン間が導通状態となる。これにより、ドレイン電圧がソース電極12とドレイン電極16との間の耐圧よりも低いSBDダイオード18の耐圧にクランプされた状態で、ドレイン電流が徐々に減少していく。

(もっと読む)

高電圧スイッチング回路

【課題】高電圧処理能力および改善された実行能力を有する効率的なスイッチング回路を提供する。

【解決手段】第1および第2のIII−V族トランジスタを有し、第2のIII−V族トランジスタは、第1のIII−V族トランジスタよりも大きな降伏電圧を有する。さらに、第1のIII−V族トランジスタと並列に配置されるシリコンダイオードを有し、この並列配置は、第2のIII−V族トランジスタと直列に接続、効率的な3端子デバイスであり、第1端子は第2のIII−V族トランジスタのゲート、第1のIII−V族トランジスタのソースおよびシリコンダイオードのアノードに結合する。第2端子は第1のIII−V族トランジスタのゲートと結合し、第3端子は第2III−V族トランジスタのドレインと結合する。

(もっと読む)

半導体装置

【課題】スイッチング素子による高温の悪影響を回避して、誤点弧を防止する回路をスイッチング素子と同一の基板上に配置した半導体装置を提供する。

【解決手段】基板5上の導電体パターン51,52上にNチャネル型のMOSFET10、及びNチャネル型で半導体材料が炭化珪素からなるJFET30を各別に近接して配置し、MOSFET10のゲート電極13とJFET30のドレイン電極31とをリード線61で接続する。MOSFET10をオン/オフに制御する外部からの駆動信号がJFET30のソース電極32及びドレイン電極31間を伝播するときに、ソース電極32及びゲート電極33間のゲート電圧の低/高に応じてJFET30のチャネル抵抗を大/小に変更することにより、MOSFET10のドレイン電極11及びソース電極12間のスイッチング波形の前縁を、後縁に比較して緩やかな傾斜にする。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明の半導体装置は、nチャネルの高電子移動度トランジスタ(HEMT)とpチャネル電界効果トランジスタとを単一の基板上に形成した。

【解決手段】nチャネル電界効果トランジスタは、第1チャネル層7と、この第1チャネル層7にヘテロ接合し、n型の電荷を供給するn型第1障壁層6と、n型第1障壁層6に対してpn接合型の電位障壁を有するp型ゲート領域10とを備え、pチャネル電界効果トランジスタは、p型の第2チャネル層13と、pn接合型の電位障壁を有するn型ゲート領域18とを備える。各トランジスタはpn接合型のゲート領域を有するのでターンオン電圧を高くすることが可能となり、ゲート逆方向リーク電流を減少させたエンハンスメントモードでの動作を実現した。

(もっと読む)

トランジスタ素子

【課題】GaAs基板上にHEMT、HBTを順次積層してなるトランジスタ素子において、HEMTの移動度の低下を抑制することが可能なトランジスタ素子を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ(HEMT)3が形成され、HEMT3上にヘテロバイポーラトランジスタ(HBT)4が形成されたトランジスタ素子において、HEMT3がアンドープInGaAsPからなるバリア層10を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

51 - 60 / 212

[ Back to top ]