国際特許分類[H01L21/8232]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660)

国際特許分類[H01L21/8232]の下位に属する分類

MIS技術 (17,448)

国際特許分類[H01L21/8232]に分類される特許

31 - 40 / 212

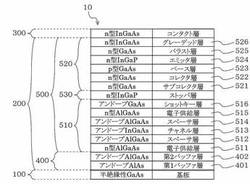

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】素子形成領域となる素子形成層の高品質化を実現し、また基板の反りを低減させると共に確実な素子分離を図り、信頼性の高い装置構成を得ることができる化合物半導体装置を実現する。

【解決手段】下地層3上に、素子分離領域に相当する部位に開口4aを有する第1のマスク4を形成し、開口4aを埋め込み、第1のマスク4上を覆うようにELO−GaN層5を成長し、ELO−GaN層5上に、素子形成領域に相当する部位に開口6aを有する第2のマスク6を形成し、開口6aを埋め込むように素子形成層7を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐圧が高く破壊等が生じにくい、信頼性の高い半導体装置を提供する。

【解決手段】基板上に形成された第1の半導体層12と、前記第1の半導体層上に形成された第2の半導体層14と、所定の領域の前記第2の半導体層の一部または全部を除去することにより形成されているゲートリセス22と、前記ゲートリセス及び第2の半導体層上に形成されている絶縁膜31と、前記ゲートリセス上に絶縁膜を介して形成されているゲート電極32と、前記第1の半導体層または前記第2の半導体層上に形成されているソース電極33及びドレイン電極34と、を有し、前記ゲートリセスの底面は、中央部分23aが周辺部分23bに対し高い形状であることを特徴とする半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜のダングリングボンドを確実に低減させて閾値電圧の変動を抑えて安定化させ、高いトランジスタ特性を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極7は、化合物半導体層2に形成された電極溝2C内に、ゲート絶縁膜6を介して一部が電極材料で埋め込まれて形成されており、ゲート絶縁膜6は、電極溝2C内において、少なくとも化合物半導体層2との界面に形成されたフッ素化合物を含有するAl−F化合物の複合層13aを有している。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層の表面におけるダングリングボンドを確実に低減させて閾値電圧の変動を抑えて安定化させ、高いトランジスタ特性を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】電極溝2Cの内壁面を含む化合物半導体層2の表面は、電極溝2Cを形成する際のドライエッチングによるエッチング残渣物12a及び変質物12bが除去されて、化合物半導体がフッ素(F)で終端されており、この電極溝2Cをゲート絶縁膜6を介してゲートメタルで埋め込み、或いは電極溝2Cを直接的にゲートメタルで埋め込んで、ゲート電極7が形成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層を加工することなく、比較的簡素な構成で確実なノーマリ・オフ動作を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2上にAlN等の第1の膜6及びAl2O3等の第2の膜7を順次に積層形成し、第2の膜7のゲート電極の形成予定部位に開口7aを形成し、開口7aをゲートメタルの一部で埋め込むように、ゲート電極8を形成し、ゲート電極のオフ時には、化合物半導体層2の電子走行層2bの2DEGがゲート電極8下の領域のみで消失する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

高周波スイッチおよび高周波モジュール

【課題】挿入損失およびチップサイズの増大を生じることなく、歪特性に優れた高周波スイッチおよび高周波モジュールを提供する。

【解決手段】高周波スイッチであって、高周波信号を入出力するための複数の入出力端子101〜103と、2つの入力端子101、103間に設けられた基本スイッチ部104、105と、基本スイッチ部104、105の導通および遮断を制御するための制御電圧が入力される制御端子106、107とを備え、基本スイッチ部104、105は、メアンダ形状のゲート電極を有するメアンダ型のFET110〜113及びFET120〜123が多段に接続されて形成され、FET110〜113、及び120〜123のうち、入出力端子103からの電気的距離が最も短いFET113、及び120のフィンガー長は、他のFET110〜112、及び121〜123のフィンガー長よりも短い。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

31 - 40 / 212

[ Back to top ]