国際特許分類[H01L23/522]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814) | 半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851)

国際特許分類[H01L23/522]の下位に属する分類

適用できる相互接続を有するもの

相互接続構造のレイアウト

材料に特徴のあるもの (313)

国際特許分類[H01L23/522]に分類される特許

31 - 40 / 2,538

半導体装置およびその製造方法、電子部品

【課題】貫通電極の微細化と表面電極の縮小化とを両立することができる半導体装置、および表面電極の大きさに関わらず、表面電極に対して貫通電極を確実にコンタクトさせることができる半導体装置の製造方法を提供すること。

【解決手段】Si基板29の表面13に複数の絶縁膜リング32を選択的に形成し、絶縁膜リング32の開口42に対向するように表面パッド33を形成する。次に、Si基板29を裏面14からエッチングすることにより、絶縁膜リング32の開口42を通過して表面パッド33に達する貫通孔56を形成し、貫通孔56の側面にビア絶縁膜35を形成した後、貫通孔56に電極材料を充填することにより、表面パッド33に電気的に接続されるように貫通電極17を形成する。

(もっと読む)

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】断線等の問題を抑制しつつ逆メサの段差に配線を設けることができる半導体装置の製造方法を提供する。

【解決手段】エッチングにより半導体基板に逆メサ段差部を形成する。逆メサ段差部の下段における半導体基板の表面に、電極を設ける。逆メサ段差部内を埋めるように当該逆メサ段差部の高さよりも厚い絶縁膜を設ける。逆メサ段差部内に絶縁膜を残すように、絶縁膜積層工程で積層した絶縁膜に対してエッチバックを行う。電極に接続する配線を、逆メサ段差部に残された絶縁膜の上方に設ける。このとき、電極とのコンタクトをとる部分を対象にして、層間絶縁膜に対し開口を形成する。開口形成後、配線を、層間絶縁膜上であって逆メサ段差部の上方の領域に蒸着する。コンタクト開口を介して、配線が電極と接続する。

(もっと読む)

半導体回路装置およびその製造方法

【課題】ビアヒューズ素子の径を小さくし、ビアヒューズ素子を低電流で溶断することが可能な半導体回路装置およびその製造方法を提供する。

【解決手段】一方向に配置された複数の配線層と、前記複数の配線層のうちの少なくとも2つの前記配線層の間に設けられたビアヒューズ素子と、前記複数の配線層の配置方向に直交する平面内において前記ビアヒューズ素子に隣接する穴と、前記穴内に設けられた貫通ビアとを備えた半導体回路装置。

(もっと読む)

半導体装置およびその製造方法、電子部品

【課題】貫通電極におけるボイドの発生を防止することができ、従来に比べて信頼性の高い半導体装置およびその製造方法、ならびに電子部品を提供すること。

【解決手段】Si基板29上のゲート絶縁膜30上に電極層51を形成する。ゲート絶縁膜30上に層間絶縁膜31を形成した後、ダマシン法により電極層51と同一パターンの下側配線42と、反対パターンの下側絶縁膜43を含む下側パッド40を形成する。次に、貫通孔59を形成し、同時に、貫通孔59内に下側絶縁膜43と同一パターンの突出部60が形成された第1層間絶縁膜32を露出させる。そして、突出部60の一部がエッチング残渣として残るように第1層間絶縁膜32をエッチングした後、ビア絶縁膜38を形成し、貫通孔59の底面のビア絶縁膜38をエッチングする。次に、貫通孔59のビア絶縁膜38の内側に電極材料をめっき成長させることにより、貫通電極17を形成する。

(もっと読む)

エッチング装置及び方法

【課題】基材の幅全体をエッチングして、埋め込まれた表面構造を露出させる方法を提供すること。

【解決手段】基材の表面をその幅の全体にわたりエッチングして材料を実質的に均一に除去すること、当該エッチング処理の間エッチングされる面に光を当てること、当該面から反射又は散乱した光に端部検出技術を適用して、埋め込まれた表面構造の出現を検出すること、そして当該埋め込まれた表面構造の検出に応じエッチングを修正することを含むエッチング方法。基材をその幅の全体にわたりエッチングして、埋め込まれたを露出させるためのエッチング装置も開示される。

(もっと読む)

半導体装置、及びその製造方法

【課題】TSV付き半導体装置において、貫通孔側面すべてにバリア及びシード層を成膜しないことで、空隙の発生を防止する。

【解決手段】

第1の溝部、及び前記第1の溝部より水平断面積が小さい第2の溝部からなる凸状溝部を画成し、且つ、前記第1及び第2の溝部により両端を開口する貫通ビアホールが形成される半導体基板と、前記第1の溝部の内面から、前記第2の溝部の側面の一部まで被覆して、前記貫通ビアホールの側面に隆起するバリア層およびシード層と、前記シード層の表面上、及び、前記シード層で被覆されていない前記第2の溝部内部に形成されて、前記半導体基板の両表面から露出する電極と、を備える半導体装置が提供される。

(もっと読む)

半導体装置の製造方法および半導体装置

【目的】配線間のコンタクト配置において配線間距離をより小さく形成する。

【構成】実施形態の半導体装置は、第1と第2の配線と、第1の絶縁膜と、第2の絶縁膜と、第1のコンタクトと、第2のコンタクトと、を備えている。第1と第2の配線は、基板上に互いに並行するように形成される。第1の絶縁膜は、第1と第2の配線を覆うように形成される。第2の絶縁膜は、第1と第2の制御ゲート線間の所定位置で第1と第2の配線と並行して延びるように形成され、第1の絶縁膜と材料が異なる。第1のコンタクトは、第1と第2の配線間で、前記第2の絶縁膜に対して前記第1の配線側に位置する前記第1の絶縁膜を通して形成される。第2のコンタクトは、前記第1と第2の配線間で、前記第1と第2の配線が延びる方向に沿って前記第1のコンタクトと互いに位置をずらしつつ、前記第2の絶縁膜に対して前記第2の配線側に位置する前記第1の絶縁膜を通して形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

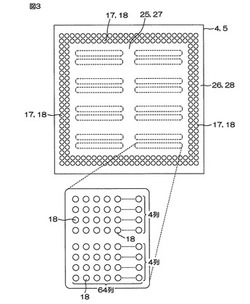

半導体装置

【課題】高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制する。

【解決手段】半導体装置1は、高周波配線、およびダミー導体パターン20(第2のダミー導体パターン)を備えている。ダミー導体パターン20は、高周波配線と相異なる層中に形成されている。ダミー導体パターン20は、平面視で、高周波配線と重なる領域を避けるように配置されている。これにより、高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制できる。

(もっと読む)

31 - 40 / 2,538

[ Back to top ]