国際特許分類[H01L23/522]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の装置内の1つの構成部品から他の構成部品へ電流を導く装置 (7,814) | 半導体本体上に分離できないように形成された導電層及び絶縁層の多層構造からなる外部の相互接続を含むもの (2,851)

国際特許分類[H01L23/522]の下位に属する分類

適用できる相互接続を有するもの

相互接続構造のレイアウト

材料に特徴のあるもの (313)

国際特許分類[H01L23/522]に分類される特許

21 - 30 / 2,538

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマークに集中する応力の方向依存性を低減して、クラックを発生しにくくする。

【解決手段】基板の第1の主面に、環状の第1の溝及びドット形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

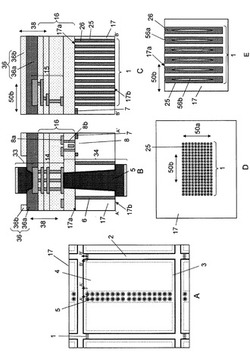

絶縁膜形成方法及び絶縁膜形成装置

【課題】信号遅延の抑制と絶縁性の向上との両立が可能な絶縁膜形成方法及び絶縁膜形成装置を提供する。

【解決手段】

シリコン貫通電極用の貫通孔が形成されたシリコン基板を備える基板Sに絶縁膜を形成するに際し、抵抗加熱ヒータ33Hによって加熱された基板Sを収容する反応室31Sに、酸素ガス及びキャリアガスであるアルゴンガスと混合されたZr(BH4)4を供給する。そして、Zr(BH4)4を上記基板S上で熱酸化することによって、基板Sの表面及び上記貫通孔の内側面にジルコニウム、ホウ素、及び酸素を含む絶縁膜の一つであるZrBO膜を形成する。

(もっと読む)

貫通電極基板の製造方法

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板の製造方法は、ウェハ状の基板に前記基板を貫通しない複数の有底孔を形成し、前記基板及び前記有底孔の表面に絶縁膜を形成し、前記有底孔が開口する側の前記基板及び前記有底孔の絶縁膜上に金属からなるシード膜を形成し、前記シード膜に第1の時間直流電流を供給する電解めっき法により、前記シード層が形成されている面の前記有底孔の底部に金属層を形成し、前記シード膜及び前記金属層にパルス電流を供給する電解めっき法により、前記有底孔内に金属材料を充填して導通部を形成し、前記有底孔が形成されている側と反対側の前記基板の表面を、前記導通部の表面が露出するまで研磨する。

(もっと読む)

基板の処理方法及びテンプレート

【課題】基板の所定位置に高い位置精度で処理液を供給し、当該基板を適切に処理する。

【解決手段】ウェハWのアライメント領域13上に純水Pを供給する(図9(a))。テンプレート20をウェハWの上方に配置する(図9(b))。純水PによってウェハWの処理領域12の上方にテンプレート20のめっき液流通路30が位置するように、テンプレート20とウェハWを位置調整する(図9(c))。テンプレート20を下方に移動させる(図9(d))。めっき液流通路30にめっき液Mを供給する(図9(e))。テンプレート20の第1の親水領域41と処理領域12との間にめっき液Mを充填する(図9(f))。めっき処理を行い、ウェハWの貫通電極10上にバンプ110を形成する(図9(g))。

(もっと読む)

半導体集積回路装置

【課題】チップあたりの端子数の増大に伴って、フリップチップ実装が種々の形態で実施されている。しかし、バンプピッチの微細化およびバンプの鉛フリー化によって、エレクトロマイグレーション耐性の確保がますます重要となっている。

【解決手段】本願の発明は、フリップチップ型の半導体集積回路装置において、チップの第1の主面上に形成された多数のUBMパッド状の各々に設けられた半田バンプの中間部には、上下を分割する前記半田バンプとは異なる材質の金属隔壁が設けられているものである。

(もっと読む)

半導体装置

【課題】基板電位を安定化させることができる半導体装置を提供する。

【解決手段】半導体装置に含まれるFET素子1は、N角形をなす外周端部30pと貫通孔を形作る内周端部30iとを有する環状のゲート電極30を備える。またFET素子1は、貫通孔の直下方に形成された内側不純物拡散領域21と、ゲート電極30のN角形の辺の外側に形成された外側不純物拡散領域22A〜22Dと、ゲート電極30の頂点の外側に形成されたバックゲート領域23A〜23Dとを備える。バックゲート領域23A〜23Dは、ゲート電極30のN角形の辺のうちゲート電極30の頂点をなす2辺の延長線Ex,Eyの少なくとも一方を跨るように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

(もっと読む)

感光性樹脂組成物、感光性フィルム及び電子部品

【課題】赤外線の吸収が可能であり、厚膜においてもパターン形成することが可能であり、低温硬化が可能である感光性樹脂組成物、フィルム及び電子部品を提供する。

【解決手段】(A)少なくとも1つのエチレン性不飽和基を有する光重合性化合物、(B)光重合開始剤、及び(C)カーボンフィラーを含む感光性樹脂組成物であって、前記(A)少なくとも1つのエチレン性不飽和基を有する光重合性化合物が、アクリレート化合物及び/又はメタクリレート化合物を含む感光性樹脂組成物。この感光性樹脂組成物をフィルム状に成形してなる感光性フィルム。絶縁膜と、前記絶縁膜の内部に配設された配線とを有した配線層を含む電子部材であって、前記絶縁膜の少なくとも一部が上記の感光性樹脂組成物又は感光性フィルムを用いて形成されたものである電子部品。

(もっと読む)

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】下層の銅配線と上層のアルミニウム配線とを接続するコンタクトプラグのコンタクト抵抗を均一化する。

【解決手段】銅配線8と、銅配線9上の層間絶縁膜10と、層間絶縁膜10上に形成されたアルミニウム配線17と、銅配線9とアルミニウム配線17とを電気的に接続するプラグ13とを備える半導体装置であって、プラグ13は銅とアルミニウムの合金からなり、銅配線9上のコンタクトホールにバリアメタルを設けずに第1のアルミニウム膜を充填し、熱処理して合金化し、未反応の第1のアルミニウム膜を除去した後、アルミニウム配線用の第2のアルミニウム膜を成膜する。

(もっと読む)

21 - 30 / 2,538

[ Back to top ]