国際特許分類[H01L25/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 複数の個々の半導体または他の固体装置からなる組立体 (14,678)

国際特許分類[H01L25/00]の下位に属する分類

すべての装置がグループ27/00〜51/00の同じサブグループに分類される型からなるもの,例.整流ダイオードの組立体 (8,439)

装置が27/00〜51/00の2つ以上の異なるメイングループに分類される型からなるもの,例.ハイブリッド回路の形成 (138)

装置がグループ27/00〜51/00の同じメイングループの2つ以上の異なるサブグループに分類される型からなるもの (5,265)

国際特許分類[H01L25/00]に分類される特許

121 - 130 / 836

電子部品内蔵モジュール

【課題】各種信号ラインが近接して形成されることによって生じ得る容量結合に起因し、且つ、各種信号ラインに対して影響を及ぼすノイズを十分に抑制する又は遮断することができ、電子回路の誤動作を確実に防止等することが可能な電子部品内蔵モジュールを提供する。

【解決手段】DCDCコンバータ1は、ICチップ7等が内蔵された電子部品内蔵基板2と、その上に載置されたインダクタ8等とを備えるものである。この電子部品内蔵基板2には、DCDCコンバータ1の出力信号を監視するフィードバック用の信号ラインである配線パターン32Fと、インダクタ8に接続されるスイッチング用の信号ラインである配線パターン32Sとが設けられており、これらの配線パターン32F,32Sは、電子部品内蔵基板2の面方向において、互いに遠ざかる方向に延在する部位を有する。

(もっと読む)

電源モジュール

【課題】入力側キャパシタの機能を保持しつつ、配線インピーダンスを低減することができ、これにより、電子回路の誤動作を確実に防止して正確な動作を安定に維持することが可能な電源モジュールを提供する。

【解決手段】電源モジュールとしてのDCDCコンバータは、ICチップ7が内蔵された電子部品内蔵基板と、その上に載置された入力側キャパシタC1等とを備えるものである。電子部品内蔵基板は、入力側キャパシタC1とは反対側に、入力電圧が入力される入力電圧端子VINを有し、ICチップ7は、入力電圧端子VINからの入力電圧が、所定の接地電位に接続される入力側キャパシタC1を経由して入力される入力電圧端子71を有するものである。そして、入力電圧端子71と入力側キャパシタC1とが接続される配線に、ビア導体(抵抗R3)が形成されるものである。

(もっと読む)

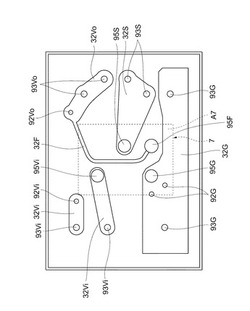

電子部品内蔵モジュール

【課題】電子回路やその周辺に位置する信号ラインに対して影響を及ぼすノイズを十分に抑制する又は遮断することができ、これにより、電子回路の誤動作を確実に防止して正確な動作を安定に維持することが可能な電子部品内蔵モジュールを提供する。

【解決手段】電子部品内蔵モジュールとしてのDCDCコンバータ1は、ICチップ7等が内蔵された電子部品内蔵基板2と、その上に載置されたインダクタ8等とを備えるものである。この電子部品内蔵基板2の内部には、DCDCコンバータ1の出力信号を監視するフィードバック用の信号ラインである配線パターン32Fが、電子部品内蔵基板2の面方向において、ICチップ7の実装領域と重なり合うように配置されている。これにより、インダクタ8からの漏れ磁束がシールドされ、ICチップ7の安定な動作が確保されるので、DCDCコンバータ1の誤動作を防止することができる。

(もっと読む)

半導体集積回路装置

【課題】消費電力を抑制することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置100は、差動信号を送信する差動信号送信素子11、差動信号を伝送する一対の第1の差動伝送線路12A、12B、差動信号送信素子11と一対の第1の差動伝送線路12A、12Bとの間に接続された一対の結合コンデンサ14A、14B、一対の第1の差動伝送線路12A、12Bの終端間に接続された終端抵抗13を備えた第1の半導体集積回路素子1と、一対の第1の差動伝送線路12A、12Bと容量性結合及び誘導性結合するように一対の第1の差動伝送線路12A、12Bに予め定めた距離を離して対向配置された一対の第2の差動伝送線路22A、22B、一対の第2の差動伝送線路22A、22Bの終端に接続され且つ差動信号を受信する差動信号受信素子21を備え、第1の半導体集積回路素子1に積層された第2の半導体集積回路素子2と、を備える。

(もっと読む)

回路装置およびその製造方法

【課題】基板を曲折する箇所に於ける機械的強度が確保された回路装置及びその製造方法を提供する。

【解決手段】回路装置10Aは、曲折領域14にて曲折された回路基板12と、回路基板の上面に形成された所定形状の導電パターン16と、導電パターン16に電気的に接続された半導体素子18等の回路素子と、を主要に備えている。そして、曲折領域14には、回路基板12を除去して設けた第1曲折部14Aと、第1曲折部14Aよりも厚い第2曲折部14Bとが含まれている。

(もっと読む)

半導体装置

【課題】携帯電話等の小型機器に実装可能なSSD(Solid State Drive)等の半導体装置を提供する。

【解決手段】半導体装置は、基台1と、メモリチップ11と、コントローラチップ12と、複数の受動素子8と、を備える。基台1は、ボンディングパッド16を有する。メモリチップ11は、基台1上に設けられ、ワイヤによりボンディングパッド16に接続され、データを電気的に記憶可能である。コントローラチップ12は、メモリチップ11から基台1に向かう方向についてメモリチップ11を含むメモリ領域MAに設けられ、メモリチップ11の動作を制御する。複数の受動素子8は、それぞれ、メモリ領域MAに設けられる。

(もっと読む)

半導体装置の製造方法

【課題】POPの場合、下段パッケージの中央部には、半導体チップが搭載されているため、上段パッケージの半田ボールを周縁部に配置しなければならない等の制約がある。そこで、下段パッケージの上面に、サブ基板を配置することで、上段パッケージの様々なボール配置、あるいは様々なチップ部品を搭載することに対応できる。このようなデュアルフェイス型パッケージの場合、サブ基板の表面には複数の接続用ランドが配置される。そのため、テスト工程においてパッケージをソケット内に収納する際、サブ基板の表面を吸着することが困難となる。

【解決手段】本願の一つの発明は、デュアルフェイス型パッケージの電気的なテストにおいて、半導体パッケージの周辺部を保持した状態で、半導体パッケージをテスト用ソケットに搬送し、電気的なテストの後、そこから搬出する半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の小型化を実現する手段を提供する。

【解決手段】配線基板10の主面10aに受動部品5を搭載する工程と、前記配線基板の主面に第1の半導体チップ4を搭載する工程と、前記配線基板の主面上に前記第1の半導体チップを介在して前記第2の半導体チップ2を搭載する工程と、前記第2の半導体チップの複数の電極パッドと前記配線基板の複数の電極パッドとを複数のボンディングワイヤ6で夫々電気的に接続する工程と、前記受動部品、前記第1及び第2の半導体チップ、及び前記複数のボンディングワイヤを樹脂封止する工程と、を有し、前記第1の半導体チップの高さは、前記受動部品の高さよりも高く、前記受動部品は、前記第1の半導体チップの周囲において、その一部若しくは全体が前記第2の半導体チップと平面的に重なる位置に搭載される。

(もっと読む)

半導体パッケージ

【課題】半導体パッケージの反りを抑制すること。

【解決手段】半導体パッケージは、第1配線基板と、第1配線基板の第1表面上に搭載された少なくとも1つの第1半導体チップと、第2配線基板と、第2配線基板の第2表面上に搭載された少なくとも1つの第2半導体チップと、を備える。第2表面は第1表面と対向している。半導体パッケージは更に、第1表面と第2表面との間に介在する樹脂層を備える。

(もっと読む)

MEMSを備える半導体装置及びその製造方法

【課題】パッケージの小型化が可能であり且つ生産効率の良い半導体装置の製造方法の提供。

【解決手段】MEMSを備える半導体装置の製造方法であって、電導層が絶縁層で被覆されたキャップ基板に、該絶縁層の上に少なくとも2つの電極を互いに離間させて形成するステップと、前記キャップ基板において前記少なくとも2つの電極間に電圧を印加することで、マイグレーションを起こして前記絶縁層を破壊させ、これにより、前記少なくとも2つの電極のうちの少なくとも一方を前記電導層に導通させるステップと、前記キャップ基板によりMEMSを覆うステップと、前記電導層に導通された電極を所定電位に接続することで、前記キャップ基板の電導層を所定電位に接続するステップとを含む。

(もっと読む)

121 - 130 / 836

[ Back to top ]