国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

1,081 - 1,090 / 9,686

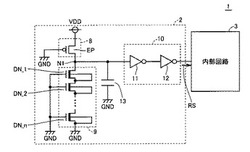

半導体装置

【課題】従来よりも低消費電力かつ小面積であるとともに設計性のよいパワーオンリセット回路またはスタートアップ回路を備えた半導体装置を提供する。

【解決手段】半導体装置1は、出力部10と、第1および第2の電位設定部8,9とを備える。出力部10は、電源投入時に、中間電位ノードN1の電位に応じた制御信号RSを内部回路3に出力する。第1の電位設定部8は、第1の基準電位ノードVDDと中間電位ノードN1との間に接続された第1の導電型を有するエンハンスメント型の第1のMOSトランジスタEPを含む。第2の電位設定部9は、第2の基準電位ノードGNDと中間電位ノードN1との間に直列接続された第2の導電型を有するディプレッション型の複数の第2のMOSトランジスタDN1_〜DN_nを含む。複数の第2のMOSトランジスタDN1_〜DN_nの各々において、ソースとウェルとが互いに接続される。

(もっと読む)

ポリシリコン抵抗の設計方法及び半導体装置の製造方法

【課題】半導体装置のサイズの大型化を抑制しつつ、ポリシリコン抵抗の抵抗値が設計値からずれた場合に補正できるようにする。

【解決手段】ポリシリコン抵抗の設計方法は、シリサイド領域1bが両端にそれぞれ形成されたポリシリコンにより構成され、シリサイド領域1bがコンタクト3へ接続されるポリシリコン抵抗1の、抵抗値を判定する工程を有する。抵抗値が設計値よりも大きい場合には、コンタクト3の位置とポリシリコン抵抗1の形成範囲とを変更せずに、シリサイドブロック膜の形成範囲を狭める補正を行うことによって、ポリシリコン抵抗1の抵抗値を減少させる工程を行う。抵抗値が設計値よりも小さい場合には、コンタクト3の位置を変更せずに、ポリシリコン(シリサイドブロック領域1a)の幅を狭める補正を行うことによって、ポリシリコン抵抗1の抵抗値を増大させる工程を行う。

(もっと読む)

半導体装置

【課題】低消費電力かつ低占有面積で、パッケージ実装後においてもプログラムを行なうことができるヒューズ素子を備えるヒューズプログラム回路を実現する。

【解決手段】ヒューズプログラム回路(FPK1−FPKn)において、ヒューズ素子FSを、多層メタル配線の第3層以上のメタル配線(M(i))を用いて実現する。各ヒューズプログラム回路において、スキャンフリップフロップ(FSSRおよびPSR)を用いてプログラム情報およびヒューズ選択情報を順次転送して、選択的に、1本ずつヒューズを電気的に切断する。

(もっと読む)

素子チップ、素子内蔵基板及び電子機器

【課題】素子チップの厚み方向に素子チップを押圧しても曲げ応力が加わり難い構造の素子チップを提供する。

【解決手段】回路基板13に接着剤12を介して実装される素子チップ1にかかわる。基板2上にスパイラルインダクターを構成するインダクター配線5と、インダクター配線5に沿ってインダクター配線5の一部を覆う第1樹脂膜6と、第1樹脂膜6に覆われていないインダクター配線5の他の一部と基板2との間に位置する第2樹脂膜7を有する。

(もっと読む)

半導体装置

【課題】FWDのVf−If特性の線形性を改善しつつ、IGBTのオン損失を低減できる半導体装置を提供する。

【解決手段】n−型ドリフト層の厚みをL1、n−型ドリフト層内でのキャリアの拡散係数をD、キャリアのライフタイムをτ、IGBTおよびFWDの構造に基づいて決まる第1パラメータをk1、p型ディープウェル層の構造に基づいて決まる第2パラメータをk2、p型ディープウェル層とn−型ドリフト層の間のビルトインポテンシャル(VAK(th))に対するスナップバック電圧(VSB)の比に対して第1パラメータk1を掛けた値(k1・VSB/VAK(th))をKとして、W3≧((k2・(Dτ)1/2)2−L12)^(1/2)かつ、W2≧L1/K1/2かつW1≦α/τ1/2+βを満たすように距離W1と距離W2と距離W3を設定する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線層の層間における剥離の有無を簡便な手法で検出できるようにする。

【解決手段】第1電極412は多層配線層20に形成されている。第2電極422は、絶縁膜22の一部を介して第1電極412と対向している。第1電極パッド430は第1電極412に接続している。第2電極パッド432は第2電極422に接続している。そして少なくとも2層以上の絶縁膜22のそれぞれが、第1電極412及び第2電極422に挟まれている。そして第1電極412及び第2電極422により、センサ40の少なくとも一部が形成されている。センサ40は、多層配線層20の層間における剥離の有無を検出するために用いられる。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタにおいてオフ耐圧及び破壊電流量の双方を高くする。

【解決手段】第2のベース領域116は、ディープウェル112の表層に形成されており、平面視において第1のベース領域114とシンカー110との間に位置している。そして第2のベース領域116は、第1のベース領域114に接続しており、第1のベース領域116よりも不純物濃度が高く、かつ第1のベース領域116よりも深さが浅い。埋込層108は、半導体層106に形成され、上面がディープウェル112及びシンカー110に接しており、ディープウェル112よりも不純物濃度が高い。

(もっと読む)

半導体集積回路

【課題】電源遮断時に、電源遮断対象ブロックへの電源配線を有効に活用することのできる半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1の電源パッドと、第2の電源パッドと、第1の電源パッドに接続された第1の電源配線と、第2の電源パッドに接続された第2の電源配線と、を備え、第1のスイッチを介して第1の電源配線に接続される電源遮断対象ブロックと、第2の電源配線に接続される常時電源供給対象ブロックと、第1の電源配線と第2の電源配線との間に接続された第2のスイッチと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】酸素・空孔欠陥が形成された半導体層を有する半導体装置の製造方法を提供すること。

【解決手段】半導体装置10の製造方法は、半導体層12の表面の一部にマスク72を形成する工程と、酸素ガス雰囲気下で半導体層12の表面に熱酸化膜74を形成する工程と、マスク72と熱酸化膜74を除去する工程と、半導体層12に向けてヘリウムを照射する荷電粒子照射工程を備えている。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

1,081 - 1,090 / 9,686

[ Back to top ]