国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

1,061 - 1,070 / 9,686

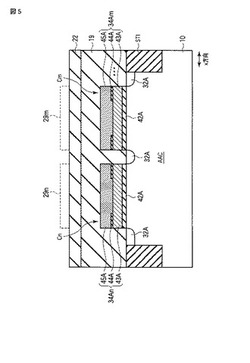

半導体装置

【課題】キャパシタを形成する領域の占有面積を縮小する。

【解決手段】本実施形態の半導体装置は、半導体基板10内に設けられた半導体領域AACと、半導体領域AAC内に設けられる複数のキャパシタCm,Cnを含むキャパシタ群と、を具備し、キャパシタCm,Cnのそれぞれは、半導体領域AAC上のキャパシタ絶縁膜42Aと、キャパシタ絶縁膜42A上のキャパシタ電極34Am,34Amと、キャパシタ電極34Am,34Amに隣接する拡散層32Aとを有し、を有し、キャパシタ電極34Am,34Anに接続される配線29m,29nのそれぞれは、キャパシタCm,Cn毎に電気的に分離され、キャパシタ電極Cm,Cnのそれぞれに異なる電位Vm,Vnが印加されている。

(もっと読む)

半導体装置

【課題】ボンディングパッドの直下の酸化膜を壊すことなくウエハテストを行う。

【解決手段】半導体基板9と、半導体基板9上に形成された5層の配線層と、前記5層の配線層のうち、最上層の第5配線層5に形成され、それぞれ一部が露出した複数のボンディングパッド5eと、半導体基板9上に形成され、かつボンディングパッド5eの下において平面視でボンディングパッド5eと重なる位置に配置され、さらにボンディングパッド5eと電気的に接続されたトランジスタ素子等の能動素子と、を有しており、ボンディングパッド5eの直下には、5層の配線層のうちのいずれの配線層も設けられていない緩衝膜7が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】トリミング素子からのトリミング時の気化ガスの圧力によりトリミング素子の下部の層間絶縁膜にクラックが入るのを防止する。

【解決手段】層間絶縁膜2上にトリミング素子Tを形成する。トリミング素子Tの上を層間絶縁膜3aで被覆する。トリミング素子Tの斜め上方領域の層間絶縁膜3a上にクラック誘導体Gを形成する。トリミング素子T及びクラック誘導体Gはレーザー光の照射領域に配置される。レーザー光を照射すると、トリミング素子Tの周辺及びクラック誘導体Gの周辺の層間絶縁膜3a等に重畳して広く延在する高温領域6が形成され、該高温化した層間絶縁膜3a等の剛性が低下する。その結果、トリミング素子Tの上辺のコーナー部に気化ガスの圧力がかかりやすくなり、トリミング素子Tの下辺のコーナー部にかかる気化ガスの圧力が小さくなるので、トリミング素子Tの下側の層間絶縁膜2のクラック5発生を防止できる。

(もっと読む)

半導体装置、半導体回路基板および半導体回路基板の製造方法

【課題】化合物半導体材料を節減しつつ化合物半導体を用いた高性能な半導体素子を得ることができる半導体装置、半導体回路基板および半導体回路基板の製造方法を提供する。

【解決手段】半導体回路基板が、トランジスタ形成基板10と回路形成基板50とを有する。トランジスタ形成基板10は、GaN基板であり、表面にBJT40が形成されている。トランジスタ形成基板10の裏面は平滑であり、かつ裏面にコンタクト領域を有する。回路形成基板50は、化合物半導体以外の材料で形成され、半導体能動素子を有さない。回路形成基板50は、平滑な表面、表面に露出するように埋め込まれたコンタクト領域52、54、および受動回路(図示せず)を有する。トランジスタ形成基板10と回路形成基板50は、絶縁膜等の他の膜を介在させずに直接に接合している。

(もっと読む)

低漏出のデータ保持回路を有する集積回路およびその方法

【課題】本発明は、低漏出のデータ保持回路のためのシステム及び方法を提供する。

【解決手段】集積回路は、第1の回路と、スリープトランジスタ回路とを有する。第1の回路は、入力信号を受信して、その入力信号を処理する。第1の回路は、また、漏れの少ないスリープ状態でデータを保持する。スリープトランジスタ回路は、第1の回路へ結合されており、負の電圧を有するスリープ信号を受信する。スリープ回路は、第1の回路でデータを保持している間、スリープ信号に基づいて、漏れが少なくなるようスリープ状態で第1の回路の電力消費を低減する。

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】スタンバイ状態への設定と解除が頻繁に繰り返されることにより、消費電力が増大することを避けることのできる半導体装置を提供する。

【解決手段】内部回路50と、第1制御信号を受けて内部回路への電源供給を制御する電源制御回路40と、第2制御信号を受けて第1制御信号を出力する制御信号発生回路30と、を備え、制御信号発生回路30は、第2制御信号の非活性期間が第1の期間未満であるときに第1制御信号を非活性状態とせず、第1の期間以上であるときに第1制御信号を非活性状態とする。

(もっと読む)

半導体集積回路装置

【課題】SOI基板に形成されたMOSトランジスタを含む半導体集積回路装置において、半導体集積回路装置に入力される電源電圧が高い場合であっても、SOI基板のBOX酸化膜やシリコン層を厚くすることなく、回路動作を安定させる。

【解決手段】MOSトランジスタM1〜M9は、シリコン基板、BOX酸化膜及びシリコン活性層を有するSOI基板に形成され、かつ、ソース拡散層の底部及びドレイン拡散層の底部がBOX酸化膜に到達して形成されている。エンハンスメント型PchMOSトランジスタM3,M4、M5,M7は、デプリーション型NchMOSトランジスタM10を介して、電源電圧が入力される電源端子VDDに接続されている。MOSトランジスタM10は、ソース、ゲート及びボディが結線されて定電流源として機能し、ソース電位がシリコン基板電位よりも高くなることで飽和電流が減少する電気的特性をもっている。

(もっと読む)

半導体装置およびその製法

【課題】トレンチ構造のトランジスタセルがマトリクス状に多数個形成され、そのゲート電極に金属膜からなるゲート配線がコンタクトされる半導体装置でも、ゲート耐圧を充分に高くすることができる構造の半導体装置を提供する。

【解決手段】半導体層1に凹溝11が形成され、その凹溝11内にゲート酸化膜4が形成され、その凹溝11内にポリシリコンなどからなるゲート電極5が設けられるトレンチ構造のトランジスタセルがマトリクス状に配列されたセル領域10を有している。そして、金属膜からなるゲート配線9とコンタクトするため、ゲート電極5と連続してゲートパッド部5aが設けられるが、そのゲートパッド部5aが凹溝11と同時に設けられる凹部12内に形成されている。

(もっと読む)

集積回路装置、電気光学装置及び電子機器

【課題】 静電気を集積回路装置の特定の端子に誘導し、さらに静電気が誘導される端子を含む特定の出力セルのみで静電気耐圧を強化することで大多数の入出力セルのサイズを小さくすること。

【解決手段】 電気光学装置200は、電気光学パネル100と、それを駆動する集積回路装置1とを含む。電気光学パネルは、第1基体110に形成された複数のセグメント電極112と、第2基体120に形成された共通電極122とを含む。集積回路装置は、複数のセグメント電極専用端子SEG1〜SEGm−2と、共通電極専用端子TP0,TP1とを含む。電気光学装置200は、複数のセグメント電極と複数のセグメント電極専用端子とをそれぞれ接続する複数の第1配線220と、共通電極と少なくとも一つの共通電極専用端子とを接続する第2配線230とを含み、第2配線のインピーダンスが複数の第1配線の各々のインピーダンスよりも小さい。

(もっと読む)

半導体集積回路

【課題】ロジック電圧を下げた場合に遅延差の増加量を抑えることができ、出力リファレンス信号に対する出力データ信号の相対的遅延のより狭い最大値と最小値の幅の仕様に対応できる半導体集積回路を提供する。

【解決手段】第1の電圧の供給を受けて動作するロジック部110と、第1の電圧と異なる第2の電圧の供給を受けてリファレンス信号およびデータ信号を出力する出力部130と、ロジック部から出力されるリファレンス信号およびデータ信号に遅延を与えて出力部に入力する中間部120と、を有し、出力リファレンス信号に対する出力データ信号の相対的遅延の最大値、最小値で定義されるAC特性が規定され、中間部は、出力部とロジック部の出力との間に、第1の電圧と分離された第3の電圧の供給を受けてデータ信号に遅延を与えて第2の電圧領域の出力部に入力する遅延部を含む。

(もっと読む)

1,061 - 1,070 / 9,686

[ Back to top ]