国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

1,031 - 1,040 / 9,686

半導体装置、およびその製造方法

【課題】従来に比して高いESD耐量性能を有するESD保護回路を備えた半導体装置、およびその製造方法を提供する。

【解決手段】内部回路に用いられる第1の半導体素子と、静電気による内部回路の破壊を抑制するESD保護回路として用いられる第2の半導体素子とを備える半導体装置の製造方法であって、基板に第1の半導体素子および第2の半導体素子各々についての端子領域層を形成する端子領域層形成ステップと、基板上の前記第2の半導体素子の端子領域層を除く領域について結晶欠陥を形成させる処理を施す欠陥形成ステップと、金属膜を第1の半導体素子および第2の半導体素子各々の端子領域層表面に形成する金属膜形成ステップと、金属膜と、第1の半導体素子および第2の半導体素子各々の端子領域層とをシリサイド化するシリサイド化ステップとを含む、半導体装置の製造方法である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】トランジスタが有するしきい値相当分の電圧/電流のロスを低減し、プロセスの簡略化、及び回路構成の簡素化を目的とした整流特性を有する半導体装置(RFID)を提供する。

【解決手段】無線によりデータの交信が可能な半導体装置(RFID)を構成する素子に整流回路を設ける。整流回路において、電波を受信するアンテナと整流回路のトランジスタのゲートとドレイン端子との間に、コイルを重ねて配置することで、電波を受信するアンテナとコイルの結合を利用して、ダイオード単体と比較しダイオードとコイルが出力する電圧を大きくし、整流効率を向上させる。

(もっと読む)

半導体装置およびその製造方法

【課題】より低コストで、より信頼性の高いMIMキャパシタを有する、より信頼性の高い半導体装置、およびその製造方法を提供する。

【解決手段】本製造方法は、半導体基板SUBを準備する工程と、半導体基板SUBの一方の主表面上に、アルミニウム層AC1を有する第1の金属電極LEL1と、第1の金属電極LEL1上の誘電体層DECと、誘電体層DEC上の第2の金属電極UELとを形成する工程とを備える。第1の金属電極LEL1を形成する工程においては、表面がRmax<80nm、Rms<10nm、Ra<9nmの関係を満たすように、アルミニウム層AC1が形成される。第1の金属電極LEL1を形成する工程には、少なくとも1層の第1のバリア層T1を形成する工程と、第1のバリア層T1上に、アルミニウム層AC1を形成する工程と、アルミニウム層AC1を構成する結晶を再結晶化する工程とを含んでいる。

(もっと読む)

増幅回路装置

【課題】J−FETを増幅回路装置として採用する場合に、意図しない低周波信号の入力を防止し、規格値を超過するドレイン電流が発することを回避する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FETのゲート−ソース間に接続される抵抗とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。n型半導体基板上にバックゲート領域となるp型半導体層を設けてpn接合を形成し、この接合容量をハイパスフィルタ5の容量とする。

(もっと読む)

半導体チップおよびその設計方法

【課題】設計期間が短く、面積効率が高く、電源配線における電圧降下が小さな半導体チップと、その設計方法を提供する。

【解決手段】この半導体チップは、複数の電源ドメインD1〜D4に分割された内部回路2を備える。互いに異なる電流駆動能力を有する複数種類のレギュレータR1,R2を予め準備しておき、各電源領域毎に、当該電源領域の最大負荷電流を供給するために必要なレギュレータの種類と数を選択し、選択した1または2以上のレギュレータによって当該電源領域用の電源回路を構成する。したがって、設計期間が短くて済む。

(もっと読む)

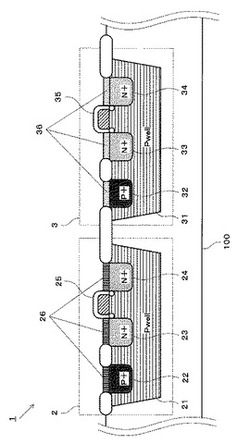

半導体装置

【課題】 パワートランジスタ及びSBD素子を有する半導体装置において、SBD素子の耐圧を高める。

【解決手段】 半導体装置は、半導体基板の主面に第1および第2領域を有し、前記第1および第2領域内にはそれぞれ複数の第1および第2導電体が形成され、前記第1領域内の隣接する第1導電体間には、第1半導体領域と、前記第1半導体領域内にあって第1半導体領域と逆の導電型を持つ第2半導体領域とが形成され、前記第2領域内の隣接する第2導電体間には、前記第2半導体領域と同導電型でかつ第2半導体領域より低濃度の第3半導体領域が形成され、前記第3半導体領域の下には第3半導体領域と同導電型で、かつ第3半導体領域より高濃度の第4半導体領域が形成され、前記第2領域の半導体基板上には金属が形成され、前記金属は前記第2半導体領域と電気的に接続され、前記第3半導体領域は、前記金属と接触しショットキー接合を形成している。

(もっと読む)

半導体装置

【課題】補償容量素子を構成する容量絶縁膜が破壊されることのない半導体装置を提供する。

【解決手段】第1の電圧が供給される第1の電源端子29と、第2の電圧が供給される第2の電源端子23と、容量絶縁膜42と該容量絶縁膜42を挟んで形成される第1及び第2電極とを其々備えており、前記第1及び第2の電源端子間に直列に設けられる複数の補償容量素子4と、奇数番目の前記補償容量素子4と次の偶数番目の前記補償容量素子4とを各々接続する第1の配線層に形成された第1の容量接続配線と、偶数番目の前記補償容量素子4と次の奇数番目の前記補償容量素子4とを各々接続する第2の配線層に形成された第2の容量接続配線と、前記第1及び第2の容量接続配線のいずれか一方に隣接して設けられ、実質的に固定された電圧が供給されるシールド配線5と、を備える。

(もっと読む)

保護回路および半導体装置

【課題】小面積で、ESD強度を向上させた保護回路を提供する。

【解決手段】接地電位線から電源電圧線への方向が電流の順方向となる第1のダイオードと、接地電位線から信号線への方向が電流の順方向となる第2のダイオードと、接地電位線から電源電圧線への方向が電流の順方向となる第3のダイオードと、信号線から電源電圧線への方向が電流の順方向となる第4のダイオードと、を有する。第1および第2のダイオードは、接地電位線に接続された第1の拡散層を共有し、第3および第4のダイオードは、電源電圧線に接続された、第1の拡散層とは異種の導電性の第2の拡散層を共有している構成である。

(もっと読む)

半導体装置及びその製造方法

【課題】主スイッチング素子の温度の急上昇に対応することができ、主スイッチング素子の保護を十分に行うことができる半導体装置を提供する。

【解決手段】半導体装置100は、横型構造のパワーIGBTである主スイッチング素子60と横型構造のサイリスタである感熱素子70とを備える。主スイッチング素子60と感熱素子70とが同一のP−型半導体基板1上に形成されている。感熱素子70のアノード電極22が、主スイッチング素子60のゲート電極8と電気的に接続されている。感熱素子70のカソード電極20が、主スイッチング素子60のエミッタ/ソース電極9と電気的に接続されている。

(もっと読む)

駆動制御装置

【課題】ターンオン時に問題となるダイオードの逆回復電流低減等の特性について所望の特性を得られるようにする。

【解決手段】ダイオードD3およびインダクタL1による直列回路がダイオードD1に並列接続されているため、負荷電流が還流するときにはインダクタL1の作用によってダイオードD3の順方向に流れ続けやすくなる(図5(b))。また、トランジスタM2のゲートに第1オン制御電圧が印加される前にトランジスタM1のゲートに0を超える電圧で且つトランジスタM1のしきい値電圧Vth未満の第2オン制御電圧(ON’:図5(a)、図5(b))を印加している。インダクタL1およびダイオードD3に流れ続けているときに、ダイオードD1に逆回復電流が流れる。

(もっと読む)

1,031 - 1,040 / 9,686

[ Back to top ]