国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

1,011 - 1,020 / 9,686

半導体装置

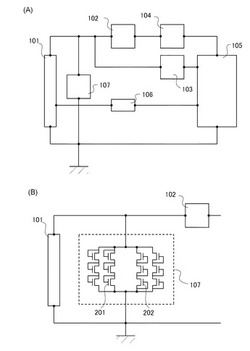

【課題】通信距離が極端に短い場合においても正常に動作し、且つ通信距離が長い場合においては、保護回路での消費電力を抑え、信頼性の高い半導体装置(RFID)を提供する。

【解決手段】無線によりデータの交信が可能な半導体装置(RFID)を構成する素子を保護するための保護回路107を設けることに特徴を有する。そして、整流回路102において生成された直流電源電位が所定の値(基準値)以上となるときに保護回路107が動作するようにし、生成される直流電源電位の値を小さくする。一方、整流回路102において生成された直流電源電位が所定の値(基準値)以下となるときは、保護回路107が動作しないようにし、生成された直流電源電位の値をそのまま用いる。また、保護回路107のトランジスタ201,202は、酸化物半導体層により構成されており、トランジスタ201,202のオフ電流を下げ、保護回路107での消費電力を抑える。

(もっと読む)

半導体集積回路及び半導体集積回路装置

【課題】従来技術と比較して占有面積が小さく、かつ基板電流が流れる経路の抵抗を低く抑え、寄生バイポーラトランジスタの動作を抑制することができる半導体集積回路及び半導体集積回路装置を提供する。

【解決手段】p型半導体基板10に形成されたドレイン領域D1、ソース領域S1、及びp型活性領域Bと、ドレイン領域D1とソース領域S1との間に形成されたゲート電極TG1と、ドレイン電極TD1と、ソース電極TS1と、基板電極TB1とを備えたNMOSトランジスタMN1と、ソース領域S1とp型活性領域Bとの間に形成されたドレイン領域D2及びソース領域S2と、p型活性領域Bと、ドレイン領域D2とソース領域S2との間に形成されたゲート電極TG2と、ドレイン電極TD2と、ソース電極TS2と、基板電極TB2とを備えたNMOSトランジスタMN2とを備え、NMOSトランジスタMN2は、基板電極TB1とソース電極TS1との間に接続される。

(もっと読む)

電流制御用半導体素子、およびそれを用いた制御装置

【課題】ゲインa、およびオフセットbの変動を動的に補正することで、1チップのIC内で高精度な電流検出が可能な電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】

同一半導体チップ上に、トランジスタ4と、電流−電圧変換回路22とADコンバータ23とを有する。参照電流生成回路6は、負荷2の電流に電流パルスIcを重畳して、ADコンバータが出力する電圧デジタル値を変動させる。ゲインオフセット補正部8は、参照電流生成回路6による電圧デジタル値の変動を信号処理して、ADコンバータ23が出力する電圧デジタル値と負荷の電流デジタル値の線形関係式におけるゲインa及びオフセットbを動的に取得する。電流デジタル値演算部12は、ゲインオフセット補正部8により取得されたゲイン及びオフセットを用いて、ADコンバータが出力する電圧値を補正する。

(もっと読む)

半導体装置、電子装置、及び半導体装置の製造方法

【課題】第1インダクタと第2インダクタを構成する金属材料のマイグレーションに起因して第1インダクタと第2インダクタの絶縁が確保できなくなることを、抑制する。

【解決手段】半導体チップ100は配線基板200の第1面上に実装されており、多層配線層を有している。第1インダクタ112は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は第1インダクタ112に対向している。封止樹脂400は、配線基板200の少なくとも第1面と、半導体チップ100とを封止している。溝500は、封止樹脂400と多層配線層の界面のうち、少なくとも第1インダクタ112と第2インダクタ122の間に位置している部分の全域に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上の第2の層間絶縁膜17上にヒューズ層18Tが形成され、ヒューズ層18Tは第3の層間絶縁膜20で覆われる。第3の層間絶縁膜20上には、キャップメタル24に覆われたパッド電極23が形成され、それらは第1及び第2のパッシベーション膜25,26に覆われる。次に、ヒューズ層18T上で開口する第1のレジスト層27をマスクとして、ヒューズ層18T上で第2のパッシベーション膜26から第3の絶縁膜の厚さ方向の途中までをエッチングする。その後、パッド電極23上で開口する第2のレジスト層30をマスクとして、パッド電極23上で第1及び第2のパッシベーション膜25,26及びキャップメタル層24をエッチングしてパッド電極23の表面を露出する。その後、保護膜32を形成する。

(もっと読む)

半導体装置

【課題】高い比精度が要求される複数のトランジスタの特性ばらつきを低減する。

【解決手段】本発明の半導体装置は、半導体基板上に配置されたトランジスタTr1と、半導体基板上で見たキャリアのドリフト方向がトランジスタTr1のキャリアのドリフト方向と同じ方向となる向きに配置されたトランジスタTr2と、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51b同士を接続する拡散層51cと、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51bまたはその拡散層同士を接続する拡散層51cの表面に接続され、拡散層51a,51bに給電するためのコンタクトプラグ61と、を備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】ゲートリセスの深さの制御を安定的に行なえるようにして、ノーマリオフ動作のデバイスを安定的に作製できるようにする。

【解決手段】半導体装置を、基板1の上方に設けられたGaN電子走行層2と、GaN電子走行層2上に設けられた第1AlGaN電子供給層3と、第1AlGaN電子供給層3上に設けられたAlN電子供給層4と、AlN電子供給層4上に設けられた第2AlGaN電子供給層5と、第2AlGaN電子供給層5及びAlN電子供給層4に設けられたゲートリセス9と、ゲートリセス9に設けられたゲート電極12とを備えるものとする。

(もっと読む)

窒化物系半導体装置

【課題】導通抵抗が低く、かつ高い電圧を維持すると共に、ゲート絶縁膜の破壊を抑制したゲート信頼性の高い窒化物系半導体装置を提供することを目的とする。

【解決手段】AlGaN層20上に形成されたショットキー電極22が、正孔をソース電極30に流す(輸送する)ため、ゲート絶縁膜24、特にトレンチ部23のコーナー部に集中して電圧が印加されることがなくなる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】プローブ跡を除去でき、かつ、製造コストが増加することを抑制できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】この半導体装置は、回路が形成された基板100と、この基板100上に形成され、表面に保護絶縁膜300が形成された多層配線層と、この多層配線層の最上層の配線層に位置し、上記回路に接続し、かつ、表面が保護絶縁膜と略同一面となっている電極パッド200と、を備える。また、このような半導体装置の製造方法は、回路が形成された基板100上に、この回路に接続し、かつ、保護絶縁膜300から突出した突出部201を有する電極パッド200を形成する工程と、プローブ端子500を電極パッド200に接触させることにより、回路の動作テストを行う工程と、突出部201の少なくとも表面を研磨する工程と、有する。

(もっと読む)

1,011 - 1,020 / 9,686

[ Back to top ]