国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

961 - 970 / 9,686

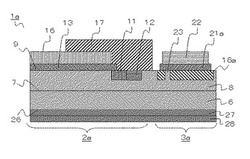

半導体装置およびその製造方法

【課題】シリコン以外の半導体で形成される半導体素子で使用可能なTEGを有する半導体装置およびその製造方法を提供する。

【解決手段】SBD部2aと、SBD部2aの電気特性を測定するためのTEG部3aと、を備えた半導体装置1aであって、SBD部2aは、n型のSiCドリフト層8と、SiCドリフト層8上に、SiCドリフト層8の表面9と接触して形成された第1のショットキー電極13と、を有し、TEG部3aは、SiCドリフト層8の表面9を含む箇所に形成されたp型のイオン注入層18aと、SiCドリフト層8上に、SiCドリフト層8の表面9と接触して形成された第2のショットキー電極21aと、第2のショットキー電極21aと電気的に接続され、SiCドリフト層8とは接触しないようにイオン注入層18a上に形成された電極パッド22と、を有する

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】入出力端子と半導体スイッチとの間を接続する配線同士が交差する箇所が発生しても、端子間のアイソレーション特性を向上させつつ、サイズ及びコストを抑制可能な半導体装置を提供する。

【解決手段】半導体スイッチ回路(20)は、複数の入力端子(31,32)のうち任意の入力端子を配線層(51)又は再配線層(251)を介して複数の出力端子(41〜44)のうち任意の出力端子と接続させるように構成される。複数の入力端子及び複数の出力端子のうち、ある端子と半導体スイッチ回路との間を接続する配線と、他の端子と半導体スイッチ回路との間を接続する配線とが交差している箇所において、交差する配線のうち、一方の配線を配線層とし、他方の配線を再配線層とする。

(もっと読む)

コンデンサとその製造方法ならびに多層配線基板

【課題】簡便・安価に製造可能な浮遊インダクタンスの小さいコンデンサ部品と、その製造方法を提供する。また、前記コンデンサ部品を低背化した部品と、その低背コンデンサを内蔵した多層配線基板を提供する。

【解決手段】有機材料の単分子膜を誘電体とするコンデンサにおいて、コンデンサ用電極のうち少なくとも一つが、誘電体単分子膜に担持された触媒物質によって開始する無電解めっきで形成されることを特徴とするコンデンサ。コンデンサを支持基材の上に形成することで、薄膜コンデンサを部品として扱うことが可能となる。また、前記支持基材を薄く研削することで、部品の低背化が可能となる。

(もっと読む)

素子評価用半導体集積回路

【課題】 インバータ等の論理ゲートからなる大規模なゲートチェーンを有し、そのゲートチェーンにおいて不良の原因となっている論理ゲートを特定することが容易な素子評価用半導体集積回路を提供する。

【解決手段】 多段接続された複数の論理ゲートからなるゲートチェーンと、モニタ信号線MONと、ゲートチェーンにおける各論理ゲートの出力ノードとモニタ信号線MONとの間に各々介挿され、当該モニタユニットMUaを指示する制御信号が与えられることにより、モニタ信号線MONに当該出力ノードの電圧に依存した信号を発生させる複数のモニタユニットMUaと、ゲートチェーンにおける複数の論理ゲートの出力ノードを順次モニタ対象とし、モニタ対象とする論理ゲートの出力ノードに接続されたモニタユニットを指示する制御信号を発生するモニタユニット選択手段を有する。

(もっと読む)

テストエレメントグループおよび半導体装置

【課題】保護ダイオードの有無に拘らず、素子特性を精度良く測定することの可能なテストエレメントグループおよびそれを備えた半導体装置を提供する。

【解決手段】テストエレメントグループ10において、電界効果型トランジスタからなるn個の素子DUT1〜DUTnが規則的に配置されている。ドレイン線DLおよびソース線SLがそれぞれ、全ての素子DUT1〜DUTnに対して共通化されており、その一方で、ウェル線WLが素子DUT1〜DUTnごとに1つずつ設けられている。選択対象の素子(選択素子DUTx)の素子特性を測定する際には、基板バイアス効果を利用して、非選択対象の素子(非選択素子DUTy)に流れるオフリーク電流を小さくする。

(もっと読む)

半導体装置

【課題】同期整流方式のDCDC変換装置において、短絡防止期間中に、同期整流用FETのドレインが負電圧となると、基板−ドレインの間に電流が流れ、基板の電位が揺すられる。同期整流用FETを内蔵した素子の場合、この基板の電位の揺れは制御回路の誤動作を招く。

【解決手段】P型基板とバックゲートとが分離されたNチャネルMOSFETを2段縦積みにした構造を有する複合素子を、同期整流用FETとして用い、複合素子の上段側FETを、メイン側FETがオフかつ下段側FETがオフとなる短絡防止期間において、オフとする。

(もっと読む)

半導体装置

【課題】プロセスを簡素化し低コスト化を実現するとともに、さらに、システムを簡素化しノイズ対策を可能にするMEMSレゾネータ及びMEMSレゾネータの製造方法を提供する。

【解決手段】MEMSレゾネータの製造方法は、基板10上に形成された半導体デバイスとMEMS構造体部4とを有するMEMSレゾネータ2の製造方法であって、半導体デバイスは、上部電極30と下部電極26とを有するONOキャパシタ部6と、CMOS回路部8と、を含み、ONOキャパシタ部6の下部電極26を、第1シリコン層26を用いて、形成する。MEMS構造体部4の下部構造体16とONOキャパシタ部6の上部電極30とを、第2シリコン層52を用いて、形成する。及び、MEMS構造体部4の上部構造体18とCMOS回路部8のゲート電極34とを、第3シリコン層54を用いて、形成する。

(もっと読む)

保護装置

【課題】 USBコネクタと被保護部品間の信号ラインに接続されるESD破壊の保護装置として、双方向pn接合ダイオードが用いられるが、従来の構造では製造工程が複雑、煩雑で保護装置の低コスト化や汎用性に限界があった。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面にpn接合を形成し、互いに離間する第1n+型不純物領域および第2n+型不純物領域を設け、第1n+型不純物領域とコンタクトする第1導電層と、第1導電層にコンタクトし入力端子に電気的に接続する第1電極と、第2n+型不純物領域にコンタクトする第2導電層と、第2導電層にコンタクトし接地端子に電気的に接続する第2電極とを設けて横型の双方向pn接合ダイオードによる保護装置を提供する。

(もっと読む)

半導体装置

【課題】トレンチゲートをゲート電極で完全に埋め込むトレンチゲート型MOSFETにおいて、パフォーマンスに優れた半導体回路装置を提供する。

【解決手段】第1のトレンチ溝7を複数有し、第一のトレンチ溝7をゲート電極材料9で完全に埋設するトレンチゲート型MOSFETであって、互いに第1の導電型のソース10および第2の導電型のウェル5の電位が異なる、第1のトレンチ縦型MOSFET11と第2のトレンチ縦型MOSFET12との間に第2のトレンチ溝14を有し、第2のトレンチ溝の内面には絶縁膜8cが形成され、さらに第2のトレンチ溝の内部には第1の導電型のゲート電極材料9cが埋設されている。

(もっと読む)

961 - 970 / 9,686

[ Back to top ]