国際特許分類[H01L27/088]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 1種類の半導体構成部品だけを含むもの (8,288) | 電界効果構成部品のみを含むもの (6,291) | 構成部品が絶縁ゲートを有する電界効果トランジスタであるもの (5,861)

国際特許分類[H01L27/088]の下位に属する分類

相補型MIS電界効果トランジスタ (2,948)

国際特許分類[H01L27/088]に分類される特許

101 - 110 / 2,913

半導体装置

【課題】トンネル型FETのオン電流とオフ電流との比と、単位基板面積あたりのオン電流を増大させる。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に絶縁膜を介して形成されたゲート電極と、前記ゲート電極の側面に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記半導体基板上に順に積層された第1導電型の下部主端子層と、中間層と、第2導電型の上部主端子層とを有し、前記ゲート絶縁膜を介して前記ゲート電極の側面に形成された積層体とを備える。さらに、前記上部主端子層は、前記ゲート電極の側面に、前記ゲート絶縁膜と半導体層を介して形成されている。

(もっと読む)

炭化珪素半導体装置

【課題】スイッチング素子のソースおよびドレイン間に還流ダイオードが接続された構造を有する炭化珪素半導体装置を一の炭化珪素基板を用いて提供する。

【解決手段】第1層34は第1導電型を有する。第2層35は、第1層34の一部が露出されるように第1層34上に設けられ、第2導電型を有する。第1〜第3不純物領域は、第2層35を貫通して第1層34に達する。第1および第2不純物領域11、12の各々は第1導電型を有する。第3不純物領域13は、第1および第2不純物領域11、12の間に配置され、かつ第2導電型を有する。第1〜第3電極S1、D1、G1は、第1〜第3不純物領域11〜13のそれぞれの上に設けられている。ショットキー電極SKは、第1層34の一部の上に設けられ、第1電極S1に電気的に接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】素子面積の増加を抑制しつつ、動作速度が向上する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置は、ボディ領域11a、11bと、ボディ領域11a、11b上にゲート絶縁層12a、12bを介して配置されるゲート電極13a、13bと、ボディ領域11a、11bを挟んで配置される一対のソース/ドレイン領域14a、14b、14cと、を有する電界効果型トランジスタ10a、10bを複数備え、複数のトランジスタ10a、10bは、ボディ領域11a、11b同士が電気的に接続されており、複数のトランジスタ10a、10bの内の一のトランジスタ10aのゲート電極13aのみが、複数のトランジスタ10a、10bの内の何れかのトランジスタのボディ領域と電気的に接続される。

(もっと読む)

トレンチポリシリコンダイオード

【課題】シリコン内にダイオード構造を位置させた半導体製造方法を提供する。

【解決手段】トレンチポリシリコンダイオードを製造する方法は、N+(P+)型基板上にN−(P−)型エピタキシャル領域を形成すること、エピタキシャル領域内にトレンチを形成すること、さらに、前記トレンチ内に絶縁層を形成し、前記トレンチをポリシリコンで充填する。さらに、P+(N+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのP+(N+)型領域を、N+(P+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのN+(P+)型領域を形成しトレンチ内にポリシリコンダイオードを形成することを含み、ダイオードの一部は、トレンチの上面より低い。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

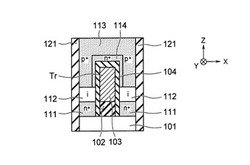

半導体装置の製造方法

【課題】エピタキシャル成長後に不純物を導入するためのイオン注入工程を省略する。また、エピタキシャル成長層の厚さがばらついた場合であっても、ピラー部にまで不純物が導入されることによるトランジスタ特性の変動を防止する。

【解決手段】基板の主面にシリコンピラーを形成した後、シリコンピラーの下の基板内に、シリコンピラーと逆導電型の第1の拡散層を形成する。シリコンピラーの側面にゲート絶縁膜を介してゲート電極を形成する。次に、シリコンピラーの上面上に不純物を含むシリコンをエピタキシャル成長させることで、シリコンピラーと逆導電型の第2の拡散層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧で動作するMISトランジスタと高電圧で動作するMISトランジスタや抵抗素子等の素子とを混載した半導体装置において、不純物の導入による素子の特性のばらつきを抑える。

【解決手段】半導体装置は、第1のゲート絶縁膜4aと、第1のゲート電極6aと、第1のゲート電極6aの両側方に形成された第1のLDD領域7aと、第1のLDD領域7aの外側に位置する第1のソース/ドレイン領域13aとを有する第1のトランジスタ30を備える。第1のトランジスタ30は、第1のゲート電極6aの上面上及び側面上から第1のLDD領域7aの少なくとも一方上に亘って設けられた絶縁膜を有しており、前記絶縁膜のうち前記第1のゲート電極の側面上に設けられた部分の膜厚は、前記絶縁膜のうち前記第1のLDD領域の少なくとも一方上で最も薄い部分の膜厚よりも大きい。

(もっと読む)

101 - 110 / 2,913

[ Back to top ]