国際特許分類[H01L29/06]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体本体 (3,016) | 半導体本体の形状に特徴のあるもの;半導体領域の形状,相対的な大きさまたは配列に特徴のあるもの (1,731)

国際特許分類[H01L29/06]の下位に属する分類

整流,増幅,またはスイッチされる電流を流す電極が接続されている半導体領域をもつものであって,その電極が3つ以上の電極を持つ半導体装置の部分であるもの (1)

整流,増幅,またはスイッチされる電流を流さない電極が接続されている半導体領域をもつものであって,その電極が3つ以上の電極を持つ半導体装置の部分であるもの

国際特許分類[H01L29/06]に分類される特許

81 - 90 / 1,730

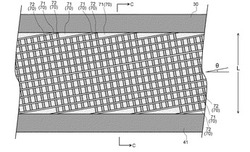

半導体装置

【課題】パワー半導体素子において、周辺の電界強度を緩和する構造を小さな面積で実現する。

【解決手段】周辺領域Qにおいては、半導体層との間に周辺層間絶縁層(絶縁層)を介して複数の多結晶シリコン層70が、ソース電極30から端部ドレイン電極41の間にかけて設けられる。多結晶シリコン層70には、その長手方向が水平方向から傾斜した(傾斜角θ、0<θ<90°)傾斜部が設けられている。多結晶シリコン層70の傾斜部においては、p型領域71と、n型領域72とが長手方向に交互に多数形成されている。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

パワーMOSFET、IGBTおよびパワーダイオード

【課題】トレンチフィル方式によるスーパジャンクションMOSFETは、ボイドフリーの埋め込みエピ成長が必要な為、トレンチの面方位を一定方向に揃えることが要求される場合がある。また、特にチップコーナ部のカラムレイアウトが、チップコーナの対角線に対して左右が非対称になった場合、チップコーナのカラム非対称性からブロッキング状態での等電位線の様子はコーナ部で湾曲し、等電位線が密になるポイントが発生し易く、耐圧低下を引き起こすおそれがある。

【解決手段】本願発明は、パワーMOSFET等のパワー系半導体能動素子に於いて、ほぼ矩形を呈するアクティブセル領域等の周りのチップ周辺領域に、リング状のフィールドプレートを設け、そのフィールドプレートは、前記矩形の辺に沿った部分の少なくとも一部にオーミックコンタクト部を有するが、前記矩形のコーナ部に対応する部分には、オーミックコンタクト部を設けないものである。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】斜めイオン注入を行わなくても、外周耐圧構造を形成でき、かつ、高いドレイン耐圧が得られるようにする。

【解決手段】凹部16の底面に形成されたP型領域18と、トレンチ13内に配置されたP+型層15、および、凹部17の底面に形成されたP型領域19とによってP型リサーフ層20を構成することで電界緩和構造とする。P型リサーフ層20がトランジスタセル領域R1の周囲を囲むような構成とされることから、外周耐圧構造領域R2に延びる電界をさらにトランジスタセル領域R1の外周側に延ばすことが可能となり、ブレークダウン位置を凹部17の底面におけるN-型ドリフト層2にシフトできるため、電界緩和を行うことが可能となる。したがって、ドレイン耐圧を向上させることが可能となる。

(もっと読む)

半導体装置

【課題】高耐圧のパワー半導体素子における周縁部の素子破壊を抑え、耐圧を向上させることを可能とする。

【解決手段】第1導電型の第1の半導体層と、第1の半導体層の表面に第2導電型の拡散領域を有するセル部と、第1の半導体層の表面に、それぞれセル部を囲むように形成された複数の第2導電型の第2の半導体層と、第1の半導体層の表面に、第2の半導体層の外周に離間して形成され、第1の半導体層より高濃度の第1導電型の第3の半導体層と、第1の半導体層の表面の、第2の半導体層と、第3の半導体層との間に設けられ、第2の半導体層より低濃度の第4の半導体層と、複数の第2の半導体層のそれぞれ内側に、第2の半導体層より低濃度で、第4の半導体層と不純物濃度又は導電型が異なる複数の第5の半導体層と、を備える。

(もっと読む)

窒化物半導体装置

【課題】ドレイン電極配線によって形成されるフィールドプレートに起因する電流コラプス現象への影響が抑制された窒化物半導体装置を提供する。

【解決手段】窒化物半導体からなる機能層20と、機能層20上に離間して配置されたソース電極3及びドレイン電極4と、ソース電極3とドレイン電極4間で機能層20上に配置されたゲート電極5と、機能層20上に配置された層間絶縁膜7と、層間絶縁膜7上に配置され、ドレイン電極4と電気的に接続されたドレイン電極配線41とを備える窒化物半導体装置であって、ゲート電極5とドレイン電極4間において、層間絶縁膜7を介してドレイン電極配線41が機能層20と対向する領域を有さない。

(もっと読む)

半導体基板の製造方法

【課題】トレンチ内を結晶性の高いエピタキシャル膜で埋めることができ、特にpnコラムの形成に適する半導体基板の製造方法を提供する。

【解決手段】ドライエッチングにより半導体基板10aにトレンチT1を形成するトレンチ形成工程と、120℃以下の低温で行うケミカルドライエッチング(CDE)またはウエットエッチングによりトレンチT1の表層部をエッチングして、第1ダメージ層D1を除去する第1ダメージ層除去工程と、半導体基板10aを非酸化性かつ非窒化性の雰囲気下において1050℃以上の高温で熱処理を行い、第1ダメージ層D1の下層に存在する第2ダメージ層D2の結晶性を回復する第2ダメージ層回復工程と、トレンチT1内にエピタキシャル膜3を形成して、トレンチT1をエピタキシャル膜3で埋め込むトレンチ埋め込み工程とを有してなる半導体基板10の製造方法とする。

(もっと読む)

III族窒化物系電子デバイス

【課題】キャリア補償の影響を低減可能なIII族窒化物系電子デバイスを提供する。

【解決手段】III族窒化物系電子デバイス11では、ドリフト層15は主面13a上に設けられており、また1×1017cm−3未満のシリコン濃度を有するn−型III族窒化物系半導体からなる。このシリコンはドナーとして作用する。合成オフ角は主面13aの全体にわたって0.15度以上である。合成オフ角は、例えばIII族窒化物支持基体13のC面の単位法線ベクトルVCNと主面13aの単位法線ベクトルVPNとの成す角度である。合成オフ角の値は、主面13a上にわたって分布している。ドリフト層15内における炭素濃度NCは3×1016cm−3以下である。

(もっと読む)

電子デバイス

【課題】改良されたプレーナデバイスを提供する。

【解決手段】電子デバイスは、移動電荷キャリアを支持する基板と、該基板面上に形成されてその両側に第1および第2の基板領域を定義し、該第1および第2の基板領域は該絶縁体によって定義される細長いチャネルによって接続され、該チャネルは該第1の領域から該第2の領域への基板内の電荷キャリア流路を提供し、該第1および該第2の基板領域間の伝導度は、この2つの領域間の電位差に依存する。該基板は有機材料とすることができる。移動電荷キャリアは、0.01cm2/Vs〜100cm2/Vsの範囲の移動度を有することができ、該電子デバイスはRFデバイスであってもよい。

(もっと読む)

81 - 90 / 1,730

[ Back to top ]